数据采集系统中SDRAM控制器的FPGA设计

2017-09-03雷能芳

雷能芳

(渭南师范学院 数理学院,陕西 渭南 714000)

数据采集系统中SDRAM控制器的FPGA设计

雷能芳

(渭南师范学院 数理学院,陕西 渭南 714000)

针对SDRAM时序控制复杂等设计难点,提出了一种基于现场可编程门阵列 (FPGA)设计SDRAM控制器的方法。使用状态机的设计思想,采用Verilog硬件描述语言对时序控制程序进行了设计。通过Modelsim SE 6.0开发平台进行了时序仿真,得到的SDRAM读写仿真波形图时序合理、逻辑正确。

FPGA;SDRAM控制器;状态机;Verilog硬件描述语言;时序仿真

数据存储是数据采集系统中的重要组成部分,同步动态随机存储器(Synchronous Dynamic Random Access Memory,SDRAM)因其具有精度高、读写速度快、支持突发式读写及价格低廉等优点,成为数据缓存器的首选存储介质。但其需要不断地刷新,控制时序和机制比较复杂,给用户操作带来不便[1-2]。因此其接口控制电路的设计是关键。而且,随着集成电路和可编程逻辑器件的快速发展,使得FPGA在处理速度、硬件资源和灵活性方面具有更大的优越性[3-4]。基于FPGA的这种优势,本文提出了一种基于FPGA芯片,采用大容量高速缓存器SDRAM来对传输数据进行缓存,不但解决了存储容量问题,而且也解决了速率问题[5]。

1 SDRAM工作原理

1.1 SDRAM有以下几个工作特性

1)SDRAM的初始化

SDRAM在上电后要有200 us的输入稳定期,在这个时间内不可以对SDRAM接口做任何操作;之后由一个预充电指令完成对所有页的预充电操作;接着发出8条刷新操作指令;最后在模式配置指令下完成SDRAM内部模式寄存器的配置[6-8]。

2)访问存储单元

通常一个SDRAM中包含几个Bank,SDRAM是以Bank为组织,由Bank地址线BA控制Bank之间的选择,每个Bank的存储单元是按行和列寻址的。为了减少I/O引脚数量,SDRAM复用地址线,所以在读写SDRAM时,先由行激发命令激活要读写的Bank,并锁存行地址,然后在读写指令有效时锁存列地址。

3)刷新

为了提高存储密度,SDRAM采用硅片电容存储数据,而电容总是倾向于放电,因此SDRAM光是上电并不能一直保存数据,必须在电容放电完成之前给电容提前充一次电即执行一次自动刷新指令以避免数据丢失。

4)预充电

由于SDRAM的寻址具有独占性,所以在进行读写操作后,如果要对另一行进行寻址,就要将原来有效(工作)行关闭,重新发送行/列地址。Bank关闭现有工作行,准备打开新行的操作就是预充电。

5)操作控制

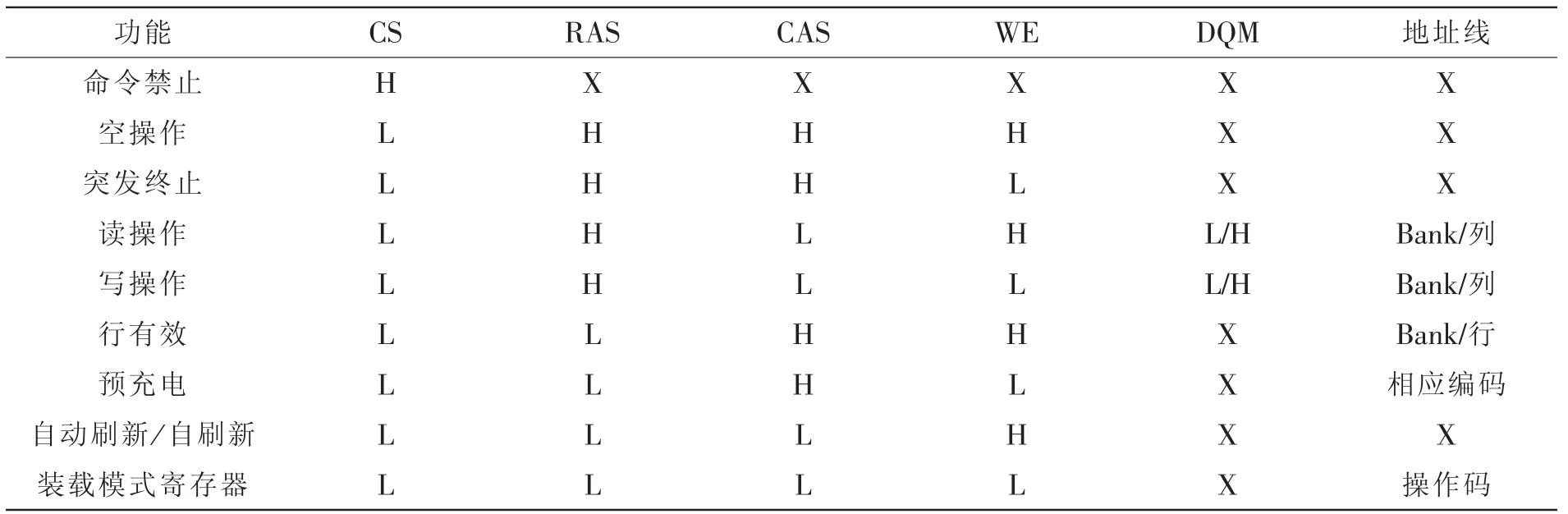

SDRAM的具体控制命令由一些专用控制引脚和地址线辅助完成。CS、RAS、CAS和WR在时钟上升沿的状态决定具体操作动作,地址线和Bank选择控制线在部分操作动作中作为辅助参数输入。SDRAM具体操作指令如表1所示。

表1 SDRAM 操作命令真值表

1.2SDRAM的几个重要参数

tRCD:SDRAM[8-10]行列地址线复用,地址线分两次送出,先送行地址线,再送列地址线,而且二者之间要有一定时间间隔tRCD。

CL(CAS Latency,CAS 潜伏期):读命令与数据有效之间的延迟时间。

tREF:对所有行完成一次刷新的时间。目前公认的标准是,存储体中电容的数据有效保存期上限是64 ms。

tRP(Precharge command Period,预充电有效周期):在发出预充电命令之后,要经过一段时间才能允许发送行激发命令打开新的工作行。

BL(Burst Lengths,突发长度):对某一 Bank 同一行中相邻的存储单元连续进读/写操作所涉及到的存储单元(列)的数量。SDRAM可实现突发式的读/写,支持的突发长度可设置为1个,2个,4个,8个数据周期或者全页模式。SDRAM虽然支持数据全页突发传输方式,但一次最多只能传输完一行的数据,这是因为当存储数据所在的行不同时,需要用预充电命令释放当前行并由行有效命令重新激活所需行。

2 SDRAM控制器的FPGA实现

本设计使用的SDRAM芯片是HY57V643220D型号芯片,有4个Bank,2根Bank选择线BA1、BA0,每一个 Bank 有 11 行(A10~A0)、8 列(A7~A0),容量为4Bankx 512 Kx 32 bit,即8 MB。FPGA采用ALTERA公司的Cyclone系列芯片EP1C12Q240C8。

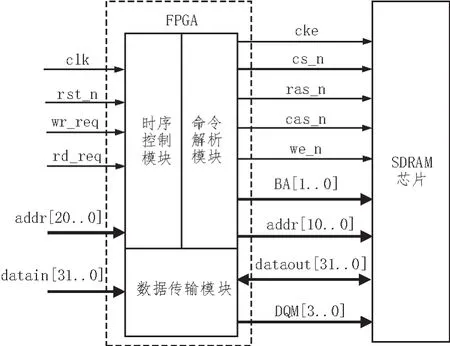

SDRAM控制器逻辑图见图1。它主要由时序控制模块、命令解析模块及数据传输模块[11-14]组成。下面详细介绍各个子模块的功能及Verilog HDL[15]设计方法。

图1 SDRAM控制器逻辑图

2.1 时序控制模块

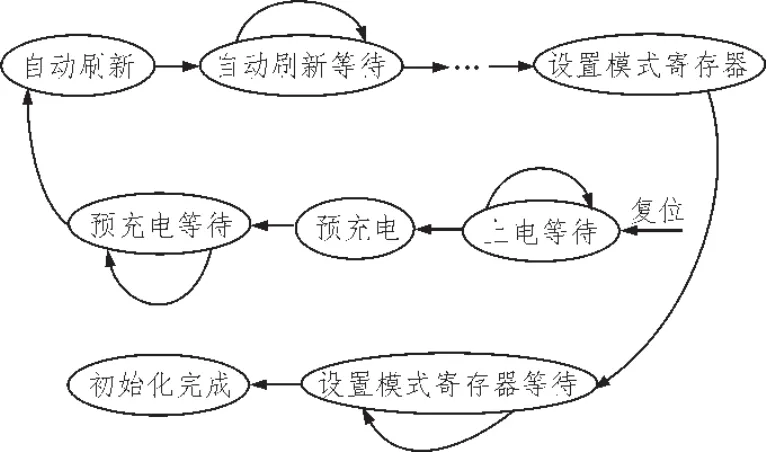

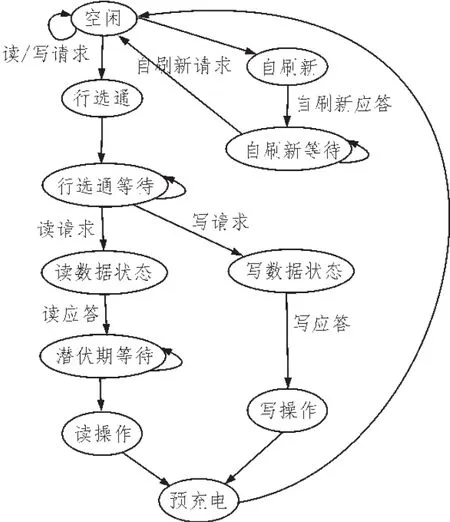

时序控制模块是SDRAM控制器的核心。该模块内部设有两个状态机,其中一个用来控制上电初始化的状态迁移,另外一个用来控制正常工作时的状态迁移。通过对各个状态的保持时间的控制,完成SDRAM的上电初始化、定时刷新和读写控制等状态的迁移。SDRAM初始化时状态迁移示意图如图2所示,正常工作时状态迁移示意图如图3所示。

图2 初始化状态迁移示意图

图3 SDRAM读写状态迁移示意图

系统加电后SDRAM控制器先进入初始化状态,依次完成如下过程:上电等待至少200 us;所有Bank预充电;8次自动刷新过程;模式寄存器设置等过程。初始化完成后,SDRAM将进入正常工作状态。

不操作SDRAM时控制器处于空闲状态。在接到读/写请求之后,SDRAM处于行选通状态。因为行、列地址线复用,二者之间有一个tRCD的时间间隔,此时间间隔通过行选通等待状态来完成,之后控制器根据读/写请求信号进入读/写数据状态,同时控制器产生一个SDRAM读/写应答信号。如果控制器产生的是读应答信号,经过CL的潜伏期进入读操作;如果控制器产生的是写应答信号,SDRAM开始进行写操作。在完成读/写操作后若需要换行进行读/写,控制器必须执行一次预充电命令关闭原来有效工作行,然后进入到空闲状态等待下一轮读/写操作。SDRAM要不断进行刷新才能保留住数据,当有自刷新请求信号产生时,控制器进入自刷新状态,而且自刷新操作优先级高于读/写操作。

2.2 命令解析模块

命令解析模块是利用SDRAM命令真值表,根据时序控制模块产生的各个不同状态对FPGA和SDRAM 的接口控制信号 cke、ras_n、cas_n、we_n 等进行赋值,从而来实现对SDRAM的控制。

2.3 数据传输模块

数据传输模块就是要在指定的时间状态里,根据时序控制模块的不同状态指示读写SDRAM相应地址的数据,以实现对SDRAM数据总线的控制。由于dataout是双向数据线,故要有一个方向控制位,也就是当作为输入数据线时,输出就是高阻态;当作为输出口时,输入就为高阻态。

3 时序仿真验证

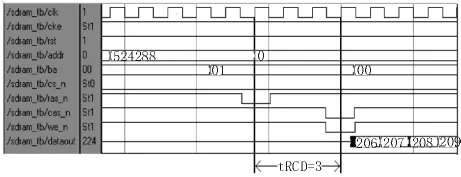

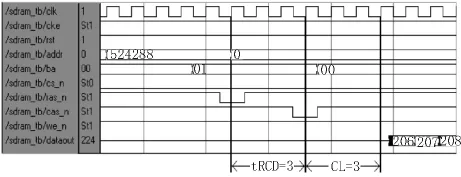

在本设计中,突发长度BL设置为全页突发模式,潜伏期CL设置为3,行列地址线有效时间间隔tRCD设置为3。使用仿真工具Modelsim SE对SDRAM控制器进行了时序仿真[7-8]。图4为突发写操作的时序仿真波形,行选通后再经过3个时钟周期,发出写操作命令,依次往Bank 0中写入206、207、208、209等256个32位数据。图5为突发读操作的时序仿真波形,行选通后再经过3个时钟周期,发出读操作命令,等待3个时钟的潜伏期,从SDRAM的Bank 0 中依次读出 206、207、208、209 等 256 个 32位数据,实现了正确的全页突发读/写操作。

图4 SDRAM突发写时序仿真波形

图5 SDRAM突发读时序仿真波形

4 结束语

文中结合SDRAM的控制指令,介绍了一种基于FPGA的SDRAM控制器的设计方案。设计中通过状态机的设计思想,采用Verilog硬件描述语言编程实现对SDRAM逻辑控制。FPGA开发采用Altera公司的Quartus II9.1与Modelsim SE 6.0进行综合、布局布线与仿真。仿真结果表明,用现场可编程门阵列FPGA器件对SDRAM进行复杂时序的控制设计是准确可行的。SDRAM作为高速的数据缓存,在基于FPGA的控制下,将会在高速、高密度、高端的数字存储和传输系统中得到更加广泛的使用。

[1]李木国,何文涛,刘于之.基于PCI总线高速数据采集卡的SDRAM控制器设计[J].计算机测量与控制,2011,19(10):2578-2580.

[2]张富贵,陈宇熠,吴雪梅,等.SDRAM控制器的FPGA设计及验证[J].中国农机化学报,2013,39(5):238-241.

[3]惠为君.基于FPGA的SDRAM控制器[J].电脑知识与技术,2015(5):241-242.

[4]项力领,刘智,杨阳,等.单片SDRAM的数据读写乒乓操作设计[J].长春理工大学学报:自然科学版, 2013,36(5):140-143.

[5]刘浩淼,卞树檀,朱守保.SDRAM控制器简易化设计[J].电子设计工程,2013,19(19):52-54.

[6]向强,蔡威,姬高飞,等.基于FPGA的图像数据缓存控制器设计[J].西南民族大学学报:自然科学版, 2013,39(3):461-463.

[7]王永康,顾晓东.基于FPGA的星载图像实时处理系统设计[J].电子设计工程, 2015,23(3):179-181.

[8]康磊,雒明世.基于FPGA的双端口SDRAM控制器的实现[J].电气自动化, 2013,35(4):97-99.

[9]柳炳琦,庹先国,蒋鑫.基于FPGA的多路数据采集系统的研究与设计 [J].核电子学与探测技术,2013,35(4):622-625.

[10]刘文彬,朱名日,郑丹平.基于FPGA的大容量高速采集系统的设计 [J].计算机测量与控制,2014,22(11):3751-3753.

[11]杨会建,田成军,杨志娟,等.基于FPGA的SDRAM乒乓读写操作设计[J].长春理工大学学报:自然科学版, 2015,38(2):67-71.

[12]侯宏录,张文芳.基于FPGA的SDRAM控制器设计方案[J].兵工自动化, 2012,31(2):57-59.

[13]孙佳郡,刘子龙,何明军.基于FPGA的高效率SDRAM读写双口控制器设计[J].制造业自动化,2013,35(10):115-117.

[14]肖积涛,马幼鸣,周鸣争,等.基于FPGA的高速数据采集系统的设计与实现[J]计算机技术与发展,2012,22(6):217-219.

[15]王金明.数字系统设计与Verilog HDL[M].4版.北京:电子工业出版社,2011.

Design of SDRAM controller in data acquisition system based on FPGA

LEI Neng-fang

(School of Mathematics and Physics, Weinan Teachers University, Weinan 714000, China)

According to the difficulty in complex timing control of SDRAM,a general SDRAM controller is designed using Field Programmable Gate Array (FPGA).The timing control program is designed by using the design concept of state machine and Verilog hardware description language.By using the simulator of the Modelsim SE 6.0,the simulative waveforms for reading and writing SDRAM are presented with reasonable time sequence and correct logic.

FPGA; SDRAM controller; state machine; Verilog HDL; timing simulation

TN929.11

:A

:1674-6236(2017)15-0137-04

2016-06-22稿件编号:201606158

陕西省教育厅科学研究计划项目(14JK1247);渭南师范学院特色学科建设项目(14TSXK07)

雷能芳(1973—),女,陕西澄城人,讲师。研究方向:数据采集与传输。