一种基于FPGA的多路图像拼接的4K高清显示设计

2017-08-09作者邹江江国海曾丽娟遵义师范学院

作者/邹江,江国海 ,曾丽娟,遵义师范学院

项目基金:黔科合LH字【2015】7008

一种基于FPGA的多路图像拼接的4K高清显示设计

作者/邹江,江国海 ,曾丽娟,遵义师范学院

项目基金:黔科合LH字【2015】7008

目前各大电视、显示器厂商的4k高清技术处理方案主要是采用基于台湾晨星等4k处理芯片设计的,而采用该方案若需要增加新的图像数据处理功能或者改变某一项功能却显得尤为困难。本文采用基于FPGA的多路图像拼接的4K高清显示设计方案,即利用FPGA将4路分辨率为1920*1080的图像信号拼接为一幅分辨率为3840*2160的4K图像信号,并通过DisplayPort接口发送到高清4K显示器进行显示。本文详细介绍了DVI数据处理硬件电路、DisplayPort接口硬件电路设计过程,并介绍了FPGA的DDR3设计及DisplayPort接口程序设计流程,最后通过试验验证设计的正确性。

4k高清;DVI;DisplayPort;DDR3

引言

近年来,随着4K高清电视、显示器的普及,使得4k的高清技术得到越来越广泛的应用,目前各大电视、显示器厂商的4k高清技术处理芯片主要基于台湾晨星等4k处理芯片设计的,但增加功能或者更改设计比较困难,无法做到自主可控设计的目的。目前基于FPGA的处理图像的速度与能力得到了较大的提高,已经可以满足4k高清显示对图像数据处理的高速要求,采用FPGA作为4K图像处理的主控芯片方案已经得到了充分的验证,本文主要是针对特殊图像拼接领域里面利用FPGA进行多路图像拼接设计的。

图1 实现4k高清显示原理框图

1. 系统总体设计

本系统要求将4路分辨率为1920*1080的DVI视频图像拼接成1路3840*2160分辨率的4k高清图像并发送至4K高清显示器进行显示。具体设计思路为将PC主机提供的4路DVI图像信号连接到本系统的DVI输入接口,4路图像信号经过DVI信号调理芯片DS16EV5110A进行信号调理,经调理的DVI信号利用DVI时序转换器TFP410A进行转换为标准的DVI时序信号,标准的DVI时序包括RGB数据、行同步HSYNC、场同步VSYNC和DE信号;FPGA采集4路DVI图像信号存入DDR3芯片,待4路DVI图像信号全部存入DDR3芯片MT41J256M16HA之后,再将4路DVI图像数据从DDR3芯片同时读出,最终通过displayport接口发送到4k高清显示器进行显示,SN65DP130S为displayport信号调理芯片,对displayport信号的增加和减弱具有重要的调节作用,系统总体框图如图1所示。

FPGA采用xilinx公司生产的kinetx—7系列的XC7K325T—2FFG900I,FPGA内部逻辑模块包含FIFO模块、DDR3总线控制模块、AXI_DDR3的IP核、MicroBlaze软核和DisplayPort模块;其中FIFO主要用于保存采集到的DVI数据,DDR3总线控制模块负责DDR3总线逻辑的调度和对axi_7series_ddr3 IP核的控制,使其能够高效高速的处理DVI输入的数据;axi_7series_ddr3模块为kinetx—7的DDR3控制的IP核模块。

2. 系统硬件设计

图2 DVI时序转换图

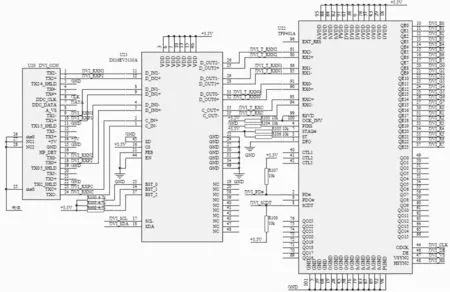

DVI图像由DVI接口输入到DS16E5110A信号调理器,再经DVI转换芯片TFP401A转换为标准的DVI时序,包含像素时钟ODCK、像素有效信号DE、场同步信号VSYNC、行同步信号HSYNC和24bit的像素点RGB数据,电路原理图如图2所示。DVI_CON接口的第6管脚CLK和第7管脚DATA别连接EEPROM 24LC02B的SCL和SDA管脚,EEPROM保存EDID信息,一旦检测到热插拔信号主机就会主动通过I2C时序读取EEPROM的EDID信息,输出相应的图像信号。

DisplayPort接口电路原理图如图3所示,SN75DP130S为DisplayPort信号均衡器,FPGA通过I2C总线配置SN75DP130S,使其满足输出的信号与FPGA中displayport的GTX端口信号强弱相适应。辅助通道AUX_CH曼彻斯特编码与主机进行通信,使其适应高速的displayport高速信号的传输。

图3 DP信号发送原理图

3. 系统程序设计

3.1 DDR3程序控制模块设计

DVI输入信号像素时钟ODCK、像素有效信号DE、场同步信号VSYNC和行同步信号HSYNC和像素点24bit的RGB数据。FPGA在检测到场同步信号VSYNC下降沿出现之后,等待DE信号有效并且将有效的像素数据存入FIFO,当FIFO的数据计数值DATA_COUNT计到一行1920个像素点的时候,调用DDR3内核将一行数据写入SDRAM存储芯片中,DVI数据处理流程如图4所示。

图4 DVI数据处理流程图

采用AXI总线操作DDR3内核,DDR3内核设置的主频为800MHz,可以满足高速的读写要求。AXI Data Width 设置为512bit;DDR3_SDRAM Data Width一共由4片16bit数据位的SDRAM组成一个64bit的DDR3数据接口。在将DVI图像数据写入AXI总线过程中,需要将24bit的DVI RGB[23∶0]数据先组成一个32bit的RGB[31∶0]数据,具体操作位高8bit补0;把数据拼接成一个512bit的AXI数据接口,需要16个RGB像素点才可以拼接成512bit的数据。一行1920个像素点的数据可以组成120个512bit的AXI总线数据,数据拼接框图如图5所示。

3.2 DisplayPort发送4K高清图像数据程序设计

DisplayPort协议包含在xilinx DisplayPort IP核中,因此要实现DisplayPort发送4K高清视频数据功能必须要使用xilinx 官方发布的DisplayPort IP核,DisplayPort IP核是硬核,IP核当中一些参数需要软件配置才能更好的使用,特别是配置SN65DP130S均衡器的时候利用软件配置参数就显得尤为重要。为了配置DisplayPort IP核的参数,本文调用了xilinx FPGA自带的MicroBlaze软核对DisplayPort IP硬核进行配置,MicroBlaze软核与DisplayPort IP硬核的硬件连接图如图6所示。

lnk_clk_p和lnk_clk_n分别为SN65DP130S产生的高频输入时钟;lnk_tx_lane_p[3∶0] 和lnk_tx_lane_ n[3∶0]分别为传输的差分数据的两端;tx_hpd为热插拔信号;aux_tx_io_p和aux_tx_io_n分别为辅助信号I2C的SDA信号的差分对;iic的iic_scl和iic_sda为配置SN65DP130S参数的时钟和数据线;rs232_uart为打印MicroBlaze的打印输出信息端口,MicroBlaze内核软件工作流程图如图7所示。

图5 数据拼接原理图

图6 DisplayPort硬核及外围元件连接原理图

图7 MicroBlaze软核的软件程序运行流程图

MicroBlaze内核程序的采用C语言编写,在生成的的工程硬件导出硬件Hardware之后,再利用SDK生成对应的软件工程,生成的软件工程包含BSP底层驱动Driver,通过编写软件程序控制DisplayPort参数的配置与发送数据的过程管理,可以实现4K高清图像的发送。

4. 试验验证

对多路视频图像拼接系统进行试验验证时,需要将4路PC机的发送的分辨率为1920*1080的图像通过DVI接口线连接到多路视频图像拼接系统电路板,再从多路视频图像拼接系统用DisplayPort线连接到4K高清显示器进行显示,测试结果如图8所示,在高清显示器上显示4路windows桌面图像,可见设计满足4路图像拼接要求。

5. 结语

试验结果表明,该基于FPGA的多路图像拼接4K高清显示系统能满足多路图像拼接和4K高清显示要求。基于FPGA的多路图像拼接与4K高清显示技术对于自主可控的硬件系统具有使用灵活、全新定制功能,广泛应用于自主控制设计领域,本文对于自主设计4K高清显示方面具有一定的指导意义。

* [1]徐军,钱占飞,贺岸,卢静.4K超高清电视发展趋势研究报告[J].中国数字电视.2013(10).

“双十一”购物狂欢节,是指每年11月11日的网络促销日,源于淘宝商城(天猫)2009年11月11日举办的网络促销活动。下面我将列举从2009年至2017年“双十一”天猫和淘宝的总销售额以及各年销售额的增长率,如表所示:

* [2]吴炜.视频图像处理技术的发展应用探析[J].硅谷.2014(01).

* [3]孙贵涛.支持4k分辨率的多格式视频处理系统设计与实现[D].成都:电子科技大学硕士学位论文,2015:12~14.

* [4]刘旭凤.基于4K2K电视构架的视频解码显示研究[D].济南:山东大学硕士学位论文,2015:9~13.

* [5]刘佳庆.基于FPGA的视频解码系统的设计与研究[D].哈尔滨:哈尔滨理工大学硕士学位论文,2013:24~25.

* [6]陈浩利.基于FPGA的超高分辨率视频信号处理系统的研究及实现[D].广州:华南理工大学硕士学位论文,2011:35~38.

* [7]熊文彬,蒋泉,曲建军,于军胜.基于FPGA实现的视频显示系统[J].液晶与显示.2011,(01):7~8.

* [8]陈伟,黄秋元,周鹏.高速电路信号完整性分析与设计[M].电子工业出版社,2009:34~35.

图8 4路分辨率为1920*1080的图像拼接画面