高集成系统异步FIFO门限设计

2017-07-19韩佳伟

韩佳伟

(兰州交通大学 电子与信息工程学院,甘肃 兰州 730070)

高集成系统异步FIFO门限设计

韩佳伟

(兰州交通大学 电子与信息工程学院,甘肃 兰州 730070)

在保证数据传输实时性要求的同时,要求实现主机对多个节点的控制时,可以引入异步FIFO存储器。方向标志与门限的方法是存储器空/满状态判断的主要方法之一,保证系统内多个存储器有效工作需要根据写入/读出速率、节点数等参数建模计算门限值。文中针对不同参数在Matlab环境下进行仿真,验证出计算的合理性。该方法不仅保证了多个存储器的有效工作,同时有效提升了存储空间的利用率,为实际应用提供了参考。

异步FIFO;门限;存储器状态

针对不同时钟域的数据通信,异步FIFO存储器可有效实现不同时钟域的通信。异步FIFO存储器的设计难点在于空/满状态的判断,目前国内主要研究的是格雷码的异步FIFO电路控制,但是格雷码本身具有一定的局限性,而门限式的异步FIFO也可以应用于空/满状态的判断。不同以往的单个FIFO存储器研究,高集成化系统下FIFO门限的不仅取决于读取速率,而且还与FIFO存储器的数目有关系。

1 FIFO原理和结构

先进先出FIFO(First Input First Output)是一种解决不同时钟域通信的存储器,它能对数据进行快速、顺序的存储和发送[1],与传统的RAM系列存储器相比,这种存储器为双端口存储器,没有外部地址端口所以不需要对地址进行单独的存储,在数据的有效读写操作过程中,其内部固有的读写指针进行加1操作可完成数据的读写功能。FIFO存储器容量与存储器宽度和深度有关,其宽度是执行一次读写操作的数据位,在成品的单片机中是固定的,如MCU 8位和16位。FIFO深度=数据量×(写入速率-读取速率)/写入速率,它表示可存储多少个8位或16位数据,如可存储8个8位数据,则存储容量为8×8。FIFO作为数据流存储器,一般应用于写入速率大于读取速率的环境中[2]。 FIFO的结构有线性、并行、树形、折肴形、环形等,在这些结构中由于环型的FIFO结构设计相对容易,因此被广泛接受[3]。

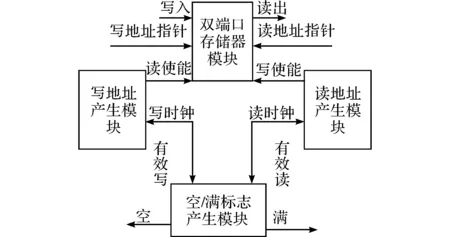

图1 异步FIFO结构图

异步FIFO存储器作为从一个时钟域向另一个时钟域传递数据流的存储器,执行在一个时钟域控制下将数据写入到FIFO存储器,在另外一个时钟域下将数据从FIFO存储器中读取的操作过程[4]。异步FIFO设计结构有双端口存储器模块、读地址产生模块、写地址产生模块、空/满标志产生模块组成。

(1)双口存储器模块一端用于将数据写入FIFO中,另一端用于从FIFO中读取数据,其内部有两个指针分别指向写入数据和读取数据,FIFO控制器通过读写信号控制指针由此产生空/满信号;

(2)写地址产生模块根据写时钟和写有效信号产生递增的写地址,读地址产生模块根据读时钟和读有效信号产生递增的读地址。当写有效时,将数据写入双端口RAM存储器中,读有效时,将数据从对应读地址读出;

(3)空/满标志位产生模块是读写地址相互比较生成空/满标志。当读写地址差值等于某一个预先设定值的时候,通过比较器判断产生空/满标志,这种情况正是状态的预判断,并非存储器真正达到空/满状态,这种方法简单易行可有效解决数据的空读取,但是预设值的设置仍需详细的计算,否则还会发生空读取。

图2 异步FIFO标志产生逻辑

2 异步FIFO的门限

目前空满状态判断主要有格雷码和预判断来实现,格雷码(Gray code)是一种准权码,假设建立一个指针,它的宽度为n+1,深度为2n的FIFO,此时将格雷码指针转换为二进制码指针。随着数据读写其指针指向地址值也在变化,当指针的二进制码中最高位不一致而其它N位都相等时,可以判定FIFO为满状态,当指针完全相等时FIFO为空状态。但格雷码有个缺点就是只能定义2n深度,相对于二进制具有一定的局限性,所以格雷码必须循环一个2n,否则就不能保证两个相邻码元之间相差一位的条件[5]。

预判断即为方向标志与门限方式,方向表示了FIFO存储数据的“朝向”,例如写入数据引起FIFO越来越满与读取数据引起FOFO越来越空的方向为FIFO的方向位[6]。当写入数据后数据量超过设定存储上限时就认为FIFO即将满,随即停止写入数据,当读取数据后数据量低于存储下限就认为FIFO趋向于空。虽然保守的空/满判断不利于存储器空间的合理利用,但一定程度上降低了空读取现象的发生,即以空间换取存储器的稳定。由于时钟的延迟,当FIFO满状态时,上端仍发送程序到FIFO此时,预先预留的空间可存储数据。同样,到达下限时数据不能立即写入此时预留的数据可先行读取出来。

预门限设定只是根据个人选择设定,一般情况下设定FIFO容量的25%为下限,FIFO容量的75%为上限[7],这种方式易造成存储空间的浪费。实际应用中FIFO的门限由上行速度、下行速度等所因素决定,单个FIFO存储器可根据计算得出较为合适的门限值。当应用于高集成化系统时,门限的设定还与存储器的数量有关。合适的门限值可保证存储器不发生溢出和无效读取,从而避免整个系统通信冲突导致数据的流失,以至于系统崩溃,无论格雷码还是预判断的方法,其目的都是防止FIFO发生数据溢出和空读取,以此保证系统的可靠性。

图3 高集成系统结构

如图3所示,高集成化系统下可假定单个存储器上行速率Va;程序传输效率u;下行速率Vb;系统节点切换时间T;存储器存储上限Qt;存储器存储下限Qb。

主机向存储器i传输程序时间为

(1)

存储器k达到下限时剩余传输时间为

(2)

主机需向m个存储器发送程序时,最低级权限存储器p(p (3) 避免引起通信冲突条件一 Tk>Tp (4) 即 (5) 达到上限的FIFO存储器r(r (6) 避免引起通信冲突条件二 Tr>Tp (7) 即 (8) 由式(5)和式(8)可得 (9) (10) 式(9)和式(10)即建模计算得出FIFO上下限,可发现其上限值大于下限值的两倍。考虑实际应用所以有Vau-2Vb(m-1)>0。根据具体m值可得出具体的门限值,选择存储器容量时选取比上限值稍大的存储器,从而避免存储容量的浪费,提高存储器利用率。 某数控车间主机通过具有FIFO存储器的CAN-RS232/RS485智能转换模块发送程序至m台数控机床,此时CAN总线速率有50 kbit·s-1( 1 000 m),125 kbit·s-1(500 m),250 kbit·s-1(250 m)。CAN总线采取标准帧格式传输效率为60%,数控机床程序消耗率有4 800 bit·s-1,9 600 bit·s-1,19 200 bit·s-1,节点切换时间为0.005 s,在Matlab环境下进行仿真,将数据代入式(9)和式(10)中,结果如下: (1)不同总线速率下节点与门限关系(程序消耗率为4 800 bit·s-1),如图所示。 图4 接入节点数与存储上限关系 图5 接入节点数与存储下限关系 在程序消耗率一定的情况下,随着CAN总线速率的增大,FIFO存储器存储程序所需时间减小,但接入数控机床数和对应门限值也在增大。而数控机床数一定时,随着CAN总线速率增大,门限值在减小; (2)不同程序消耗率下节点与门限关系(总线速率为250 kbit·s-1),如图所示。 图6 接入节点数与存储上限关系 图7 接入节点数与存储下限关系 CAN总线速率一定情况下,随着程序消耗率减小,一定量程序消耗时间增大,可接入数控机床数和对应门限值也在增大。而数控机床数一定时,随着程序消耗率减小,门限值在减小。 综上所述,根据数控机床台数等参数,确定了CAN-RS232/RS485智能转换模块中存储模块的存储下限设置为1 kB,上限设置为8 kB。以往为保证数据传输实时性,实行点对单点的控制,而存储转换模块应用可实现点对多点的控制。应用于数控设备中,一台上位机控制多台数控设备,保证了数据传输的实时性,提高了上位机的使用效率以及有效解决了数据溢出/空读的发生。 对于异步FIFO存储器设计的主要难点,论文阐述了采用空/满状态预判断的方案。在高集化系统下多个异步FIFO存储器不发生溢出和无效读取前提下,通过时钟的读写速率以及存储器数目等因素来计算门限值。以CAN-RS232/RS485智能转换模块为例,结合实际数据,可得出智能转换模块的具体门限值,并应用到实际电路。实践证明此方案的异步FIFO存储模块性能稳定,空/满判断可靠。 [1] 司岚山.一种高速大容量异步FIFO存储器的设计[D].南京:江南大学,2013. [2] 王齐双,黄震春,浦海峰.基于FPGA的异步FIFO的设计方案及性能[J].弹箭与制导学报,2014,34(6):185-189. [3] 陈标龙,王宝成,周江华.基于FPGA和FIFO技术的多串口系统设计与实现[J].计算机测量与控制,2013,21(10):2835-2837. [4] 肖静娴.基于FPGA的异步FIFO缓存器设计[J].电子测量技术,2009,32(11):92-94. [5] 章伟,范丽珍,王红展.一种有效的FIFO复位策略[J].电子科技,2014,27(10):59-60. [6] 施华钧.高效异步FIFO的设计实现[M].长沙:湖南大学,2013. [7] 倪露,邹学玉.LZW的异步FIFO输入缓冲设计[J].电子测量技术,2015,38(4):19-23. [8] 张松,李筠. FPGA的模块化设计方法[J].电子测量与仪器学报,2014,28(5):560-565. [9] 董大成,张建东. 基于FPUA的UART IP核设计与实现[J].计算机测量与控制,2012(8):2251-2253. [10] 段素蓉,庄圣贤.一种内置FIFO全双工U ART的设计与实现[J].通信技术,2010,43(2):46-50. [11] 许建峰,姚浩,唐亮,等.一种基于重传功能的新型FIFO设计[J].江苏科技信息,2016(2):47-49. [12] 杜海东.基于SFP光电模块的高速数据存储器的设计与研究[D].太原:中北大学,2015. [13] 许奥利.Matrix2可配置标量数据存储器的设计及实现[D].长沙:国防科技大学,2014. [14] 郭铮,张会新,朱思敏.基于FPGA的飞控系统数据存储器的设计与实现[J].计算机测量与控制,2014,21(1):190-194. [15] 张杰.一种高速数据存储方法的研究 [D].合肥:中国科学技术大学,2013. Asynchronous FIFO Threshold High Integration System Design HAN Jiawei (School of Electronic and Information Engineering, Lanzhou Jiaotong University, Lanzhou 730070, China) The asynchronous FIFO memory can be introduced for real-time data transmission to host the control of multiple nodes. The memory empty/full state is determined mainly by the direction marks and threshold method. The effective work of multiple memories in the system requires calculating the threshold by modeling according to such parameters as the written/read rate and the number of nodes. Matlab simulation is performed of different parameters to validate the rationality of the calculation. This method not only ensures the effective work of multiple memories, but also effectively enhances the efficiency of storage. asynchronous FIFO; threshold; memory status 2016- 08- 31 韩佳伟(1990-),男,硕士研究生。研究方向:电路与系统可靠性。 10.16180/j.cnki.issn1007-7820.2017.07.041 TN432 A 1007-7820(2017)07-146-04

3 结果仿真

4 结束语