433 MHz CMOS功率放大器设计

2017-03-23胡世林郝明丽

胡世林,孙 凯,2,郝明丽

(1.中国科学院微电子研究所 新一代通信射频芯片技术北京市重点实验室,北京100029;2.山东大学 信息科学与工程学院,山东 济南250100)

433 MHz CMOS功率放大器设计

胡世林1,孙 凯1,2,郝明丽1

(1.中国科学院微电子研究所 新一代通信射频芯片技术北京市重点实验室,北京100029;2.山东大学 信息科学与工程学院,山东 济南250100)

基于IBM 0.18um SOI CMOS工艺,设计了一款工作在433 MHz的两级AB类功率放大器。驱动级和输出级均采用共源共栅结构以提高电源电压,从而提高输出功率。采用了自适应偏置电路解决了共源管和共栅管之间电压分布不均的问题,提高了电路可靠性。输入级采用了电压-电压反馈降低增益,提高电路稳定性。片内集成了输入匹配、级间匹配电路。后仿真结果表明,该放大器的增益为33.97 dB,1 dB压缩点为28.12 dBm,PAE为23.86%。

功率放大器;SOI;共源共栅;自适应偏置;电压-电压反馈

近年来,基于CMOS工艺的高性能射频功率放大器一直是研究的热点和难点[1-3]。一方面,基于CMOS工艺的射频电路易与数字电路集成,从而降低整体芯片的成本;另一方面,随着CMOS工艺进入深亚微米区域,器件的击穿电压也随着降低,限制了CMOS功率放大器的输出功率。

对于功率放大器而言,输出功率与电源电压的平方成正比,与漏端的负载阻抗成反比[4]。所以,可以通过增大电源电压和减小负载阻抗来提高输出功率。但是由于负载阻抗必须匹配到50欧姆,而较低的负载阻抗会使得输出阻抗转换网络的阻抗转换比偏高。由集总参数元件组成的阻抗转换网络功率损耗会随着阻抗转换比的升高而升高[5]。故而,漏端的负载阻抗不能取的过低。所以,就提高功率放大器的输出功率而言,提高电源电压的优势比降低负载阻抗更明显。

以文中设计的433MHz功率放大器为例:433 MHz这一频段短距离传输能力强,广泛应用于物联网、智能家居等领域[6],但是属于免申请段发射接收频率,不需要管理,导致该频段的设备易被干扰,所以无线通信系统需要使用较大输出功率的功率放大器[7]。为了降低CMOS器件低击穿电压对性能造成的负面影响,文中设计的功率放大器采用了一种自适应偏置共源共栅放大电路。该电路能够均匀的将电压分布在共源管和共栅管,从而使得电路即使工作在比较高的电源电压下,也依旧能够保证可靠性。

1 自适应偏置电路设计

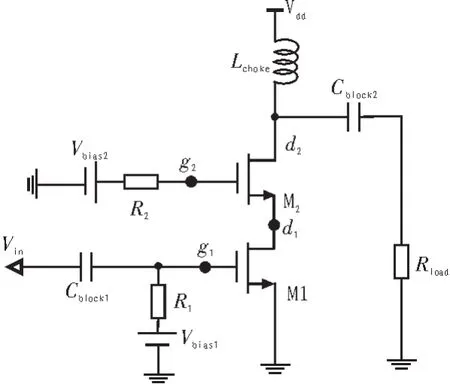

如图1是普通共源共栅电路原理图[8],其中M1的漏极和M2的源极连在一起,这样可以增加输出阻抗,提高增益;另外,由于M1和M2共同分担电源电压,因此可以适当提高电源电压以增加输出功率。Cblock1和Cblock2是交流耦合电容, 在输入输出端隔离直流信号;Lchoke是扼流电感,用来避免输出交流信号通过M2的漏端流出到地。下面我们来分析一下在大信号情况下,共栅管和共源管的电压分布。

图1 普通共源共栅放大电路

在不考虑knee电压的情况下,M2的漏极电压摆幅是0到2倍Vdd[9]。所以,M2栅漏电压最大为:

当g1点电压达到最小时,根据共源电路的特性,d1点电压达到最高;根据共栅电路的特性,d2点电压也达到最高。因此,当g1电压趋近于0时,d2点电压达到2Vdd,而d1点电压最高不能超过Vbias2,故M1栅漏电压最大值为:

由于 M2偏置在饱和区, 即 Vdd>Vbias2, 所以Vmax_M2>Vmax_M1。为了保证M1管的可靠性,就必须选择较小的电源电压,从而降低了最大输出功率。

为了消除因为共源管和共栅管因为栅漏电压分布不均给输出功率带来的不利影响,本文采用了能自动调节M2栅极电压的电路。新增电路如下图虚线框内所示:

现在来分析一下自适应偏置电路的原理。

图3为M2管的交流小信号电路图。直观上理解,一方面Cadapt可以给M2栅端电压Vg充放电,另一方面由于Cgd的存在,Vg可以随着Vd变化。所以,Vg变得不再固定。下面是详细推导:

由漏端的电流守恒可得:

图2 自适应偏置共源共栅放大电路

图3 交流小信号图

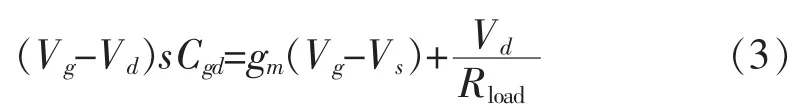

由栅端电流守恒可得:

(3)(4)式同时对Vs微分,消去dVd得

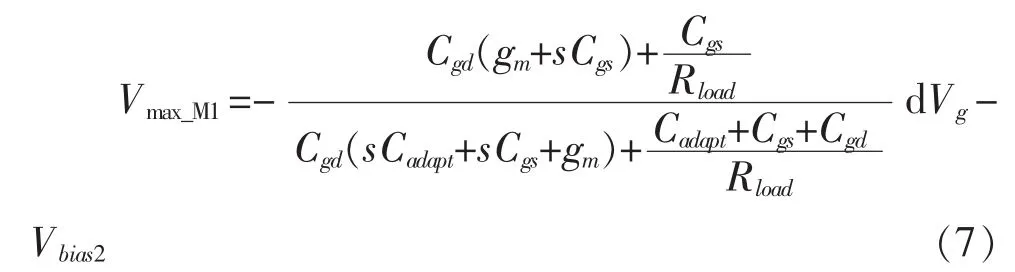

M2的最大栅漏电压为:

M1的最大栅漏电压为:

通过观察(6)(7),变量Cadapt在两式最后一项的分母上,通过适当调节Cadapt的值可以得到Vmax_M1= Vmax_M2。

如此,可以使得M1管和M2管的栅漏电压达到相同,电源电压达到最大。最后,电路的电源电压设定为4.2 V,在电路的瞬态仿真过程中,共源管和共栅管都工作在安全区域以内。

2 功率放大器设计

文中设计了一款基于SOI CMOS工艺,工作频率在433MHz的AB类功率放大器[10]。该放大器由两级组成,原理图如图4。

图4 功率放大器芯片原理图

虚线内部是片上部分,输入匹配电路,级间匹配电路均采用CLC匹配形式,有利于调节匹配网络Q值,拓展带宽[11];同时也省去了耦合电容。由于仿真得到的电感值偏高,在版图上的面积过大,所以为了节省面积,降低芯片成本,电感放在片外由分立元件实现。负载阻抗匹配网络对功放的输出功率影响最大,为了防止仿真模型不够精确造成实际输出功率不够理想,所以也放在片外实现。

为了满足输出功率的要求,设计从输出级开始。ADS2014的sourcepull模板和loadpull模板通过仿真出电路在不同负载阻抗和源阻抗的情况下的输出功率,PAE和增益来得到最佳负载阻抗和源阻抗。针对设计要求,我们设定MOS管的尺寸为12 mm。C1、R1和C2、R2分别构成输出级和驱动级的自适应偏置电路。C1值和C2确定为5 pF,R1和R2的值确定为10.8 k欧姆;确定为M1和M3的栅压确定为0.55 V。

当驱动级的尺寸选为2 mm时,输出功率能够满足驱动输出级的要求。但是,在设计过程中发现,在不加反馈的情况下,整个电路的功率增益为42.29 dB,并且低频出现震荡。因此,为了降低驱动级增益,保证电路的稳定性,在驱动级共源管的栅端和共栅管的漏端串联电阻Rf和电容Cf形成电压-电压反馈。经过反复调试Rf和Cf的值,最后确定当Rf为500欧姆,Cf为1pF时,低频震荡消失,此时,功率增益为34 dB。

由于芯片通过键合线连接到PCB板上,而键合线会降低电路的输出功率,增益以及增加电路的不稳定性[12]。所以,前仿真设计时必须考虑键合线的影响。通过ADS提供的键合线模型,仿真出单根键合线在433 MHz下阻抗值为0.035+j*0.968,其中实部可忽略不计,虚部等效为356 pH的电感。为了减少键合线对电路的影响,需要对版图做优化设计。如图4所示,M3的漏极接地,此处的键合线对电路性能的影响最大。由于M3和M4的尺寸较大,可以采用对称式布局使得M3的接地pad尽可能大,这样可以打上多根键合线,减小电感。另外,M3漏端的接地引线采用工艺库中电导率最高的顶层金属实现,寄生阻抗值可以达到最小。最后版图布局如图5所示,M3的两个接地pad分别可以打3根键合线,由于互感的存在,仿真得到的等效电感值为200pH。同时应用HFSS软件对键合线的仿真验证[13],与ADS得到的结果大致相同。

最后,电路前仿真得到线性增益为35.013 dB,输出1 dB压缩点的功率为29.01 dBm,此时的PAE为28.16%。

3 后仿真结果和分析

版图照片如图5所示。

图5 版图照片

后仿真得到的S参数如下所示:

仿真过程中,片外分立元件使用村田提供的器件库来实现。其中输入匹配网络和级间匹配网络的两个电感值分别为22 nH和12 nH。片内集成的四个电容值分别是6 pF、7.94 pF、5.73 pF和10.7 pF。版图由Cadence软件绘制完成。仿真结果如图7,在输入信号频率为433 MHz,信号源阻抗和负载阻抗为50欧姆情况下,小信号参数S11和S22均在-10 dB以下,匹配良好;S21达到了34 dB,增益符合要求。

图6 S参数

图7为输出功率,增益,PAE随输入功率变化的曲线图。

图7 输出功率、增益、PAE随输入功率的变化

由图中我们可以看出,线性增益为33.97 dB,功率增益1 dB压缩点的输出功率为28.12 dBm,PAE为23.86%;功率3dB压缩点的输出功率为29.01dBm,PAE为29.54%。对比前仿真的结果,性能出现了恶化,这是因为后仿真中考虑了导线、管芯之间的高频寄生电容和电感。另外,该电路的缺点是PAE偏低,可以通过采用Doherty电路结构[14]或包络跟踪电源调制器[15]来提高效率。

4 结 论

设计了一款433 MHz CMOS共源共栅功率放大器。该电路的特点在于应用了自适应偏置电路以提高可靠性;并且在片内集成了输入匹配电路和级间匹配电路;输出功率和增益较大。测试结果表明,该放大器线性增益为33.97 dB,功率增益1 dB压缩点的输出功率为28.12 dBm,PAE为23.86%。

[1]林俊明,郑耀华,张志浩,等.CMOS射频功率放大器高效率和高线性度研究进展 [J].电子技术应用,2015,41(11):17-23.

[2]P.Oβmann.Design of a Fully Integrated Two-Stage Watt-Level Power Amplifier Using 28-nm CMOS Technology[J].IEEE Transactions on Microwave Theory and Techniques,2016,64(1):188-199

[3]G.Xu,T.Liu,Y.Ye,J.Li,F.M.Ghannouchi.Generalisedtwobox cascaded Hammerstein-like digital predistorter for wide-band RF power amplifiers[J]Electronics Letters,2016,55(4):293-295

[4]池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[M].北京:清华大学出版社,2006:294-295.

[5]Ichiro Aoki,Scott Kee,Rahul Magoon et al.A fully-integerated quad-band GSM/GPRS CMOS power amplifier[J].IEEE Journal of Solid-State Circuits,2008,43(12):2747-2758.

[6]刘杰,章韵,陈建新.利用利用433 MHz射频通信技术实现智能家居系统[J].计算机应用,2012,32(S2):68-72

[7]Guohua Yang,Kui Zhang,Nirvana Meratnia,et al.Finding optimum settings for a 433MHz radio for long range communication,information science and control engineering(ICISCE),2015 2nd International Conference on[C]//Shanghai,2015:239-244

[8]Behzad Razavi,陈贵灿,程军.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003:70-75.

[9]Thomas H.Lee,余志平,周润德.CMOS射频集成电路设计[M].北京:电子工业出版社,2012:378-380.

[10]邓宏贵,曹祥,罗安,等.AB类功率放大器的设计与仿真研究[J].光电子技术,2005,25(4):229-233.

[11]陈邦媛.射频通信电路[M].北京:科学出版社,2002.

[12]周永强,王立新,张万荣,等.射频功率晶体管内匹配技术中键合线的建模仿真与参数提取[J].电子器件,2011(4):363-366.

[13]冯坤,朱思衡,邹晶晶,等.PCB、键合线和芯片联合仿真方法的研究[J].微波学报,2012(S2):252-254.

[14]Jang H,Roblin P,Quindroit C,et al.Asy-mmetric doherty power amplifier designed using modelbased nonlinear embedding[J].IEEE Transac-tions on Microwave Theory and Techniques,2014,62(12):3436-3451.

[15]Watkins G T,Mimis K.A 65%efficient envelope tracking radio-frequency power amplifier for orthogonal frequency division multiplex[J].IET Microwaves,Antennas&Propagation,2015,9(7):676-681.

433MHz CMOS power amplifier design

HU Shi-lin1,SUN Kai1,2,HAO Ming-li1

(1.Institute of Microelectronics of Chinese Academy of Sciences,Beijing 100029,China;2.School of Information Science and Engineering,Shandong University,Jinan 250100,China)

A 433MHz class-AB power amplifier is designed based on IBM 0.18um SOI CMOS process.To improve the output power,the driver stage and the output stage is designed using the cascade structure.To solve the problem of the unbalanced voltage between the common gate MOSFET and the common source MOSFET,the self-adaptive-bias design is used,and this improves the reliability of the circuit.This chip integrates the input match circuit and the inter stage match circuit.The post-simulation shows that the gain of the amplifier is 33.97dB,1dB compression point is 28.12dBm and the PAE is 23.86%.

power amplifier;SOI;cascode;self-adaptive-bias;voltage-voltage feedback

TN432

:A

:1674-6236(2017)05-0158-04

2016-03-16稿件编号:201603197

胡世林(1990—),男,湖北黄冈人,硕士。研究方向:射频集成电路设计。