一种SATA III的Sigma-Delta小数分频扩频时钟产生器设计

2017-02-23龙强,田泽,邵刚,王晋

龙 强,田 泽,邵 刚,王 晋

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

一种SATA III的Sigma-Delta小数分频扩频时钟产生器设计

龙 强1,2,田 泽1,2,邵 刚1,2,王 晋1,2

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

整数分频扩频时钟产生器具有较大的频率分辨率,不能满足SATA III的要求,针对该问题提出了一种SATA III的6 GHz Sigma-Delta小数分频扩频时钟产生器的设计。扩频时钟产生器基于65 nm CMOS工艺,采用了数字MASH Sigma-Delta频率调制技术和一个产生33 kHz的三角波产生器,输出频率达到6 GHz,向下扩频达到5 000 ppm。测试结果表明,在1.2 V的电源电压下,功耗为48 mW,非扩频时钟的峰峰抖动为8 ps,电磁干扰降低了15 dB。 Sigma-Delta小数分频扩频时钟产生器克服了整数分频器扩频时钟产生器的缺点,较好地满足了SATA III的要求。

扩频时钟产生器;Sigma-Delta;SATA III;小数分频

0 引言

近年来,随着芯片的工作速度越来越快,数据率也达到了Gbits/s,由此造成了信号路径中的电压和电流的高次谐波引入的电磁干扰问题愈发严重。作为高速接口电路中的主要的噪声源,必须采取各种方法降低电磁干扰。传统的方法主要是通过切断或者减小电磁干扰的辐射量,但是这种方法高昂的成本不适合深亚微米电路。基于频率调制技术的扩频时钟技术简单、有效,大大降低了成本。基于前人的研究基础,本文给出了一种创新性Sigma-Delta小数分频扩频时钟产生器的设计,将内部时钟的中心频率通过频率调制,并将功率谱分散到一个较宽的频率范围内,提高了扩频时钟产生器的频率分辨率,降低了时钟抖动和电磁干扰。

1 扩频时钟产生器设计

在现代通信系统,如SATA中,广泛采用高速串行连接方式,并采用扩频时钟下扩频技术减小电磁干扰,保证高频辐射信号不污染其他电器设备[1]。下扩频技术如图1(a)所示,下扩频将需要的频率移动到fnormal~(1-δ)fnormal之间,fnormal是SATA III的标准频率,6 GHz。δ为SATA III中规定的5 000 ppm的调制系数,fm为对应的30~33 kHz的三角波调制频率。扩频频率为:

(1)

如图1(b)所示,采用扩频技术,电磁干扰减小了7 dB。

图1 下扩频技术原理

扩频时钟通过改变内部时钟的中心频率,大大减小了电磁干扰,在现代通信系统中获得了广泛的应用。基本的扩频时钟产生器基于锁相环架构,包括压控振荡器、鉴频鉴相器、电荷泵、低通滤波器、可编程分频器和扩频时钟调制器。目前主流的扩频时钟产生器主要有4种结构。

输入参考时钟调制扩频时钟产生器[2]通过将三角波产生器调制输入参考时钟完成扩频功能,调制器产生的周期的输入频率信号和锁相环的分频器的输出信号作为鉴频鉴相器的输入信号,压控振荡器将周期性的输出频率扩频到一定的频率范围内并分散了输出信号的能量。但是在SOC应用中,这种方法不能有效处理数字信号处理电路对模拟电路的影响,外部抖动信号降低了扩频频谱的性能。

振荡器控制电压调制扩频时钟产生器[3]通过直接调制压控振荡器的控制电压来达到频率调制的目的,由于工艺变化,这种方法的扩频精度受到一定的限制。

输出相位插值调制扩频时钟产生器[4]采用了相位插值器实现扩频功能。对于传统的锁相环来说,压控振荡器的输出频率为参考频率的N倍,N为分频器的分频比。对于输出相位插值扩频时钟产生器来说,扩频时钟调制器控制相位插值器产生输出相位,压控振荡器的输出频率为参考频率的P/(NP+1)倍,其中P为相位的个数。但是由于相位插值器较差的线性度,导致在相位切换过程中扩频时钟产生器的精度有所降低,电磁干扰抑制性能下降。

分频器反馈环路调制扩频时钟产生器[5]通过调制分频器完成扩频功能,通过扩频时钟产生器调制器产生三角波数字信号改变分频器的分频比可以轻易地实现频率调制。这种方法中,模拟电路和数字电路对工艺变化不敏感,可以实现数模混合电路的单片集成,是上述4种方法中最简单有效的方法,非常适合于SATA III的应用。

2 基于小数分频锁相环的扩频时钟产生器设计

在SATA III中定义了30~33 kHz的调制频率和5 000 ppm的调制量[6],对于6 GHz的频率来说,整数锁相环较大的频率分辨率不能满足SATA III的频偏要求,因此必须采用小数分频锁相环实现扩频功能,以满足SATA III的要求。

2.1 小数分频锁相环Sigma-Delta调制器设计

一般来说,小数分频锁相环会产生分数杂散,使用Sigma-Delta调制器通过噪声整形[7],将量化噪声推到高频可以消除分数杂散[8]。本文采用了基于Sigma-Delta小数分频锁相环的扩频时钟产生器,扩频时钟产生器的架构如图2所示。

图2 Sigma-Delta小数分频锁相环扩频时钟产生器

扩频时钟产生器包括鉴频鉴相器、电荷泵、压控振荡器、低通滤波器、高速预分频器、多模分频器(MMD)、Sigma-Delta调制器和三角波产生器。三角波产生器产生一个30~33 kHz的周期性三角频率,并控制二阶Sigma-Delta调制器,Sigma-Delta调制器输出一个-1~2随机整数。通过将Sigma-Delta调制器的输出转化成多模分频器的二进制比特流,多模分频器的模从118(N-2)变化到121(N+1),在反馈回路中实现了小数分频锁相环的连续频率调制。扩频频率如式(2)所示,其中m=(0,1~38~1,0),k为Sigma-Delta调制器累加器的比特数,N为多模分频器的分频比[9]。

(2)

假如m=38,k=6,N=120,调制量δ为:

(3)

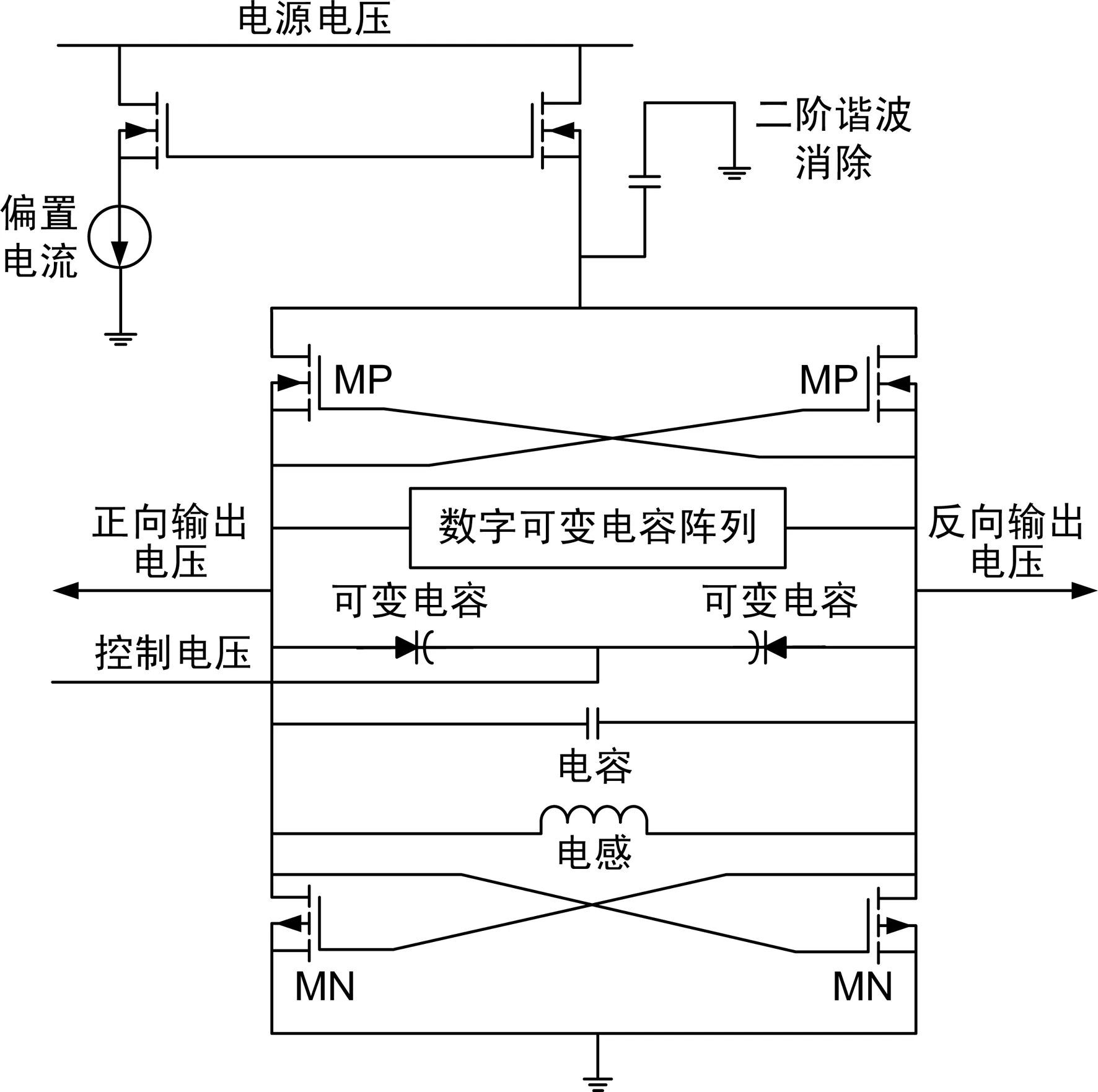

2.2 LC 压控振荡器设计

LC压控振荡器的电路结构如图3所示,压控振荡器包含1个交叉耦合负阻产生电路、1个恒定gm偏置电流产生电路[10]和PN结可变电容器CVPN。Vcntrl为压控振荡器的控制电压。数字可变电容阵列采用数字控制[11],保证了工艺变化条件下压控振荡器的频率覆盖范围[12]。

图3 LC压控振荡器电路结构

2.3 高速预分频器设计

由于压控振荡器具有较高的震荡频率,同时多模分频器的最高工作频率较低,因此需采用高速预分频电路,将振荡器的震荡频率减小一半,高速预分频电路采用电流模逻辑(CML)电路,高速预分频电路结构如图4所示,高速预分频电路采用2个CMLD锁存器构成主从触发器,同时引入负反馈,实现了预分频电路的除2功能[13]。

图4 高速预分频电路

2.4 多模分频器设计

多模分频器[14]的电路结构如图5所示,多模分频器由n位2/3双模分频电路串联构成,Sigma-Delta调制器产生一个多比特位的字符串控制2/3双模分频器,通过调整比特位来改变多模分频器的分频比。多模分频器的分频比为:

(4)

式中,n=6,分频比介于118和121之间。

图5 多模分频器电路结构

2.5 多级噪声整形(MASH)Sigma-Delta调制器设计

如果分频器的模直接由计数器控制,分频器周期性地开关会导致分频器周期性地积累误差,相位误差通常在分频器一个固定的分频比上累积,在下一个分频比上,相位误差会逐渐的补偿。因此相位误差显著地影响低通滤波器的幅度进而导致分数杂散。采用多级噪声整形(MASH)Sigma-Delta调制器[15]将量化噪声推到高频频率[16]。本文采用的二阶MASH Sigma-Delta调制器由2个级联的二阶Sigma-Delta调制器构成,这种调制器是无条件稳定的,可以大大地降低分数杂散。Sigma-Delta调制器采用全数字架构,其架构如图6所示,包含累加器和寄存器,噪声传递函数为:

N[Z]=f[Z]+(1+Z-1)2qa[Z]。

(5)

图6 MASH 1-1 Sigma-Delta调制器架构

3 测试结果分析

扩频时钟产生器采用SMIC65nmCMOS工艺,其芯片显微照片如图7所示。采用数字MASHSigma-Delta频率调制技术和一个产生33kHz的三角波产生器,输出频率达到6GHz,向下扩频达到5 000ppm。在1.2V的电源电压下,功耗为48mW,非扩频时钟的峰峰抖动为8ps。

图7 扩频时钟产生器芯片显微照片

本文采用了Sigma-Delta小数分频扩频时钟产生技术,将量化噪声推到高频频率,减小了时钟抖动,电磁干扰降低了15dB。电磁干扰抑制测试结果如图8所示。

图8 电磁干扰抑制

测试结果比较如表1所示,其中扩频量均为5 000ppm。由表1可知,Sigma-Delta小数分频扩频时钟产生技术采用先进的65nmCMOS工艺,在芯片面积、功耗以及EMI减小方面具有明显的优势。

4 结束语

Sigma-Delta小数分频扩频时钟产生器克服了输入参考时钟调制扩频时钟产生器、振荡器控制电压调制扩频时钟产生器、输出相位插值调制扩频时钟产生器和分频器反馈环路调制扩频时钟产生器等扩频时钟产生器的缺点,并采用MASH Sigma-Delta调制器等创新性技术,克服了自身缺点,各项设计指标完全满足SATA III对扩频时钟的要求,各项测试结果符合SATA III协议要求,对于更高数据率的SerDes具有很强的适应性和兼容性,可广泛兼容PCIE3.0、SATA3.0等协议。

[1] SerialATA Revision 2.6 Specification.Serial ATA Interna tional Organization[S].

[2] LEE H R,KIM O,AHN G,et al.A Low Jitter 5 000 ppm Spread Spectrum Clock Generator for Multi-channel SATA Transceiver in 0.18 mm CMOS[C]∥Proc.IEEE Int.Solid-State Circuit Conf.,2005:162-163.

[3] KOKUBOM.Spread-spectrum Clock Generator for Serial ATA Using Fractional PLL Controlled by ΔΣ Modulator with Level Shifter[C]∥Proc.IEEE Int. Solid-State Circuit Conf.,2005:160-161.

[4] CHEN W T,HSU J C,LUNE H W,et al.A Spread Spectrum Clock Generator for SATA-III[J].IEEE International Symposium on Circuits and Systems,2005(3):2 643-2 646.

[5] SHIN J S,SEO I L,KIM J Y,et al.Low-jitter Added SSCG with Seamless Phase Selection and Fast AFC for 3rd Generation Serial-ATA[C]∥IEEE Custom Integrated Circuits Conference,2006:409-412.

[6] 宋广怡.超宽带高速数据传输技术研究[J].无线电工程,2014,44(5):23-25.

[7] 赵锁军,李 伟,刘英超.一种宽带高速跳频频率合成器的设计[J].无线电工程,2014,44(1):68-71.

[8] 吴俊晨,任文成,徐志平.利用PLL减小时钟前沿抖动的研究[J].无线电工程,2013,43(2):52-54.

[9] 余 江,曹云建,熊 韬.一种2~4 GHz宽带接收机的小型化前端设计[J].无线电通信技术,2016,42(2):96-98.

[10] DECA,SUYAMA K.RF Micromachined Varactor with Wide Tuning Range[J].IEEE,Radio Frequency Integrated Circuits (RFIC) Symposium,1998,33(11):922-924.

[11] YU Yueh-hua,SU Feng-kuan,EMERY CHEN Yi-Jan,et al.A 1 V Wide Tuning Range VCO for UHF DTV Tuner[C]∥Microwave Conference,AMPC 2007,Asia-Pacific,2007:1-4.

[12] KIM Jongsik,SHIN Jaewook,KIM Seungsoo,et al.A Wide-Band CMOS LC VCO With Linearized Coarse Tuning Characteristics[C]∥Circuits and Systems II:Express Briefs,IEEE Transactions on ,2008:309-403.

[13] HASSAN H,ANIS M,ELMASRY M.MOS Current Mode Circuits:Analysis,Design and Varialibity[J].IEEE Transactions on Very Large Scale Integration Systems,2005,13(8):885-898.

[14] 曲 勃,周建军,莫婷婷.一种新型7.5 GHz 3.4 mA相位切换三模预分频器[J].信息技术,2008,32(10):38-40.

[15] LI Di,YANG Yin-tang,WANG Jiang-an,et al.Design of a Low Power GPS Receiver in 0.18 μm CMOS Technology with a ΣΔ Fractional-N Synthesizer[J].J Zhejiang Univ-Sci C (Comput & Electron),2010,11(6):444-449.

[16] MUERB De,STEYAERT M.CMOS Fractional-N Synthesizers:Design for High Spectral Purity and Monolithic Integration[C]∥Norwell:Kluwer Academic Pubilshers,2003:53-61.

[17] SONG Min-young.Piecewise Linear Modulation Technique fo r Spread Spectrum Clock Generation[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2013(21):1 234-1 245.

[18] CHOI Young-ho.A Fractional-N Frequency Divider for SSCG Using a Single Dual-modulus Integer Divider and a Phase Interpolator[C]∥SoC Design Conference (ISOCC),International,2012:68-71.

龙 强 男,(1979—),博士,工程师。主要研究方向:射频集成电路锁相环以及射频前端。

田 泽 男,(1967—),博士,研究员。主要研究方向:VLSI设计、SoC设计方法学、嵌入式微处理器体系结构与VLSI实现和嵌入式应用系统开发。

Design of a SATA III SSCG Based on Sigma-Delta Fraction-N Synthesizer

LONG Qiang1,2,TIAN Ze1,2,SHAO Gang1,2,WANG Jin1,2

(1.AeronauticalComputingTechniqueResearchInstituteofAVIC,Xi’anShaanxi710068,China;2.AeronauticalScienceandTechniqueKeyLaboratoryofIntegrateCircuitandMicro-systemDesign,Xi’anShaanxi710068,China)

Due to larger frequency resolution,integer frequency division spread spectrum clock generating appliances can not meet the requirements of SATA III.In this paper,a 6 GHz Sigma-Delta Fraction-N spread spectrum clock generator(SSCG) for serial AT Attachment Generation 3 (SATA III) is presented.Employing digital MASH Sigma-Delta modulator and 33 kHz triangular profile address generator,the SSCG achieves an output clock of 6 GHz which has an 5 000 ppm down spread spectrum amount.The SSCG is designed based on 65 nm CMOS process.The power dissipation is 48 mW under a 1.2 V supply.The peak-to-peak jitter of non spread spectrum clock is 8 ps.And the EMI reduction is 15 dB with normal frequency spread modulation from 6 GHz to 5.97 GHz.The Sigma-Delta Fraction-N spread spectrum clock generator overcomes the disadvantages of integer frequency division spread spectrum clock generator,satisfying the requirement of SATA III.

SSCG;Sigma-Delta;SATA III;Fraction-N divider

10.3969/j.issn.1003-3106.2017.01.15

龙 强,田 泽,邵 刚,等.一种SATA III的Sigma-Delta小数分频扩频时钟产生器设计[J].无线电工程,2017,47(1):62-66.

2016-10-19

总装备部预研基金资助项目(9140A08010712HK6101)。

TN792

A

1003-3106(2017)01-0062-05