基于FPGA的改进结构的DDS设计与实现*

2016-12-03马永奎高玉龙张士伟赵东来

王 硕,马永奎,高玉龙,张士伟,赵东来

(哈尔滨工业大学 通信技术研究所,黑龙江 哈尔滨150001)

基于FPGA的改进结构的DDS设计与实现*

王 硕,马永奎,高玉龙,张士伟,赵东来

(哈尔滨工业大学 通信技术研究所,黑龙江 哈尔滨150001)

主要介绍了数字频率合成器的原理和杂散来源,给出了节约存储空间的ROM表的压缩算法,采用相位抖动和平衡DAC方法对DDS结构进行了改进,抑制了相位截断误差和减小了DAC非理想特性的影响。仿真分析了用于相位抖动的随机序列周期性对杂散的影响,最后基于FPGA平台实现了改进结构的DDS,并对结果进行了测试。测试结果表明DDS用作跳频器时,杂散抑制优于40 dBc。采用此种方法设计的DDS杂散抑制度高,稳定性好,性能优越。

DDS;杂散抑制;相位抖动;FPGA

0 引言

跳频系统由于抗干扰能力强被广泛应用,其中最重要的器件为频率合成器,它决定了系统的性能。越来越多的设备都依赖于频率合成技术,所以频率源可以称作为许多电子系统的“心脏”。数字频率合成器(Direct Digital Synthesizer,DDS)由于具有频率分辨率高、转换时间快、相位噪声低等传统技术无法实现的优点,在频率合成技术领域中占有重要地位。

DDS的缺点是输出信号频谱杂散多,因此杂散抑制成为了研究DDS的重要课题。传统的滤波方式主要依赖低通滤波器,虽然可以在一定程度上滤除杂散,但频谱纯度不高。本文在此基础上分析杂散来源,采用只读存储器(Read-Only Memory,ROM)的压缩算法、相位抖动法及平衡DAC法3种方法结合的方式,从根本上抑制了杂散,节约了存储空间,优化了性能。最后基于可编程逻辑器件(Field-Programmable Gate Array,FPGA)实现了改进结构的DDS。与专用DDS芯片相比成本更低、操作更加灵活,而且还能在线更新配置。

1 DDS的基本原理及杂散分析

1.1 DDS的基本原理

DDS的基本结构组成如图1所示。它由L位相位累加器、ROM、数模转换器(Digital to Analog Converter,DAC)及低通滤波器(Low Pass Filter,LPF)组成。fclk为时钟频率,用于提供DDS各部分的同步工作;L为相位累加器的位数,相位累加器是DDS的核心部分,作用是对频率控制字Fcw进行累加,当累加器溢出时,就完成了一个周期。累加器的输出数据代表了输出波形的相位,通过相位幅度转换器可以实现相位到幅值的变换。相位幅度转换可以有很多种方法[1],最常用的是查表法,该方法需要将波形数据预先存储在ROM表中。本文就采用了ROM查表的设计方法,D为ROM存储数据位数,即为DAC的位数。经过模数转换器得到相应的阶梯波,最后在经过低通滤波器进行平滑后,得到所需频率的平滑连续波形。

DDS的输出频率为 fout=Fcw·fclk/2L,因此改变频率控制字即可改变DDS的输出频率。DDS遵循奈奎斯特采样定律,即最高的输出频率是时钟频率的一半,即 fout= fclk/2L。但由于受低通滤波器的限制,实际的最大输出频率为时钟频率的 40%。频率分辨率为f=fclk/2L,时钟一般固定,因此相位累加器的位数就决定了频率分辨率,位数越多,频率分辨率越大。

1.2 DDS的杂散分析

在实际的DDS中,由于ROM容量及数据量化位数有限分别带来了相位截断误差εp(n)和幅度量化误差εm(n),同时DAC的非理想化也带来了转换误差εDA(n)。正是这些误差在信号频谱中引入了杂散成分,据此可以构造出DDS杂散(误差)来源模型,如图2所示[2]。

图2 DDS杂散(误差)来源模型

取相位累加器输出L位中的高W位进行ROM寻址,即舍去低的B=L-W位,设输入信号s(n)为:

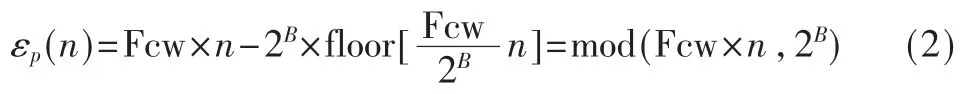

由此可得到相位截断误差:

其中floor[x]表示对 x作不大于 x的取整运算。由式(2)可知,当 Fcw=a×2B(a为整数)时,εp(n)为 0不存在相位截断误差,只有当 Fcw≠a×2B才存在相位截断误差。由此可知 εp(n)是以 2B/(2B,Fcw)为周期的序列,在频域上以 fc为周期,在(0,fc/2)内由∧=2B-1/(2B,Fcw)根离散谱线组成。

由文献[2]分析可知如下结论:在(0,fc/2)内,s(n)的频谱由 Γ=2L-1/(2L,Fcw)根离散谱线组成,其中幅度不为0的谱线最多只有(2∧+1)根。在(0,fc/2)内,s(n)的杂散频率为:

其中〈x〉y表示 x对 y取模值;相应于 fk±杂散分量的幅值为:

式(4)表明,ζk±为 k的单调减函数,当 k=1时可得到杂散幅度的最大值。

式(5)表示相位截断引起所有杂散中的最大幅度(k= 1),其中有:

则当式(6)取最大值 π/2时,由式(5)可得最大杂散幅度:

可见,相位舍位 B每减少 1位,杂散改善约为6 dB。

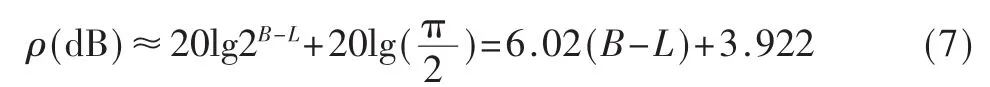

εM(n)被认为在[-2-D/2,2-D/2]区间内均匀分布的白噪声,则由量化引起的信噪比为[3]:

由式(8)可见,量化位数D每增加一位,则 SNR将提高6 dB。

通常认为除了DAC有的限位数外,DAC的瞬间毛刺、DAC的非线性、时钟的泄漏等非理想特性都是导致DDS输出频谱纯度低的因素。

由上述分析可知,增加ROM表的存储位数可有效地抑制杂散。本文采用了ROM压缩法抑制相位截断误差引起的杂散,同时采用DAC平衡法抑制DAC非理想特性引起的杂散,提高频谱纯度。

2 杂散抑制处理

2.1 基于对称性的4:1压缩算法

根据正弦波的对称性,对ROM进行了4:1压缩,节省了存储空间,提高了利用率。地址位的最高位即第10位用于判断波形是处于[0,π]范围内,还是处于[π,2π]范围内;次高位即第9位用于判断波形是位于[0,π/2]范围内,还是处于[π/2,π]范围内;由于进行了压缩,故ROM表中存储的正弦波的地址位为 8 b,即 ROM深度为28;考虑到 DAC的精度为 8 b,故 ROM表中的正弦波的数据位为8 b,即ROM宽度为8;于是,ROM的存储容量为 28×8,若不进行压缩,ROM的存储容量为 210×8,可见,存储空间节省了四分之一。这里的正弦波由Matlab生成,是对正弦波[0,π/2]之间进行 256个点的抽样,并量化成 8 b。优化的结构如图3所示[4]。

2.2 相位抖动法及DAC非线性的改进

相位抖动法主要是针对相位截断误差信号存在的周期性问题,将有规律的周期性杂散信号转换成随机的、无规律的信号[5],从而达到抑制杂散的作用。相位抖动为幅值在[0,2B]范围内均匀分布的周期性随机扰动序列。

图3 ROM压缩后的DDS框图

同时采用了平衡DAC结构的方法,改善DAC非理想特性造成的杂散,如图4所示,在此结构下的DAC结构完全相同,幅度量化后将信号取非,通过DAC后,将输出0信号相减,从而抑制由于DAC非理想造成的杂散。

图4 改进后的DDS结构图

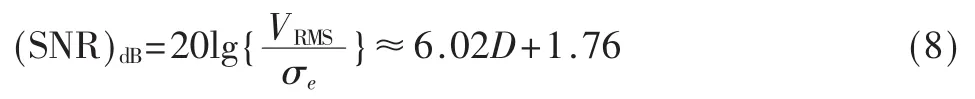

设相位累加器的位数L=10,频率控制字Fcw=127,相位截断位数B=4,幅度量化位数D=10。对DDS频谱进行 Matlab仿真,如图5所示,离散单根谱线由相位截断误差和幅度量化误差引起。

图5 未加相位抖动的DDS输出频谱

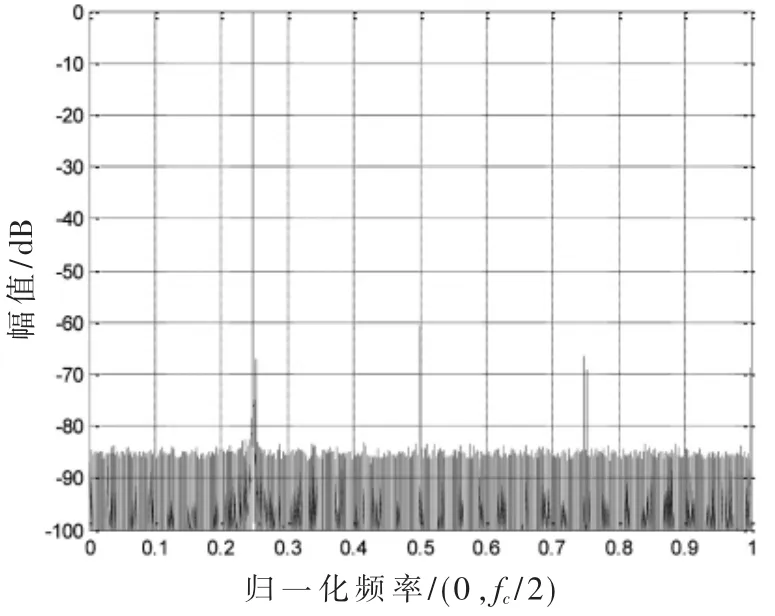

在上述条件下加入相位抖动 r(n),r(n)为幅值在[0,2B]范围内均匀分布的周期性随机扰动序列,取其周期为1 000 000个采样点。将 r(n)与相位累加器的输出相加,达到抑制杂散的作用。仿真结果如图6所示。

对比以上两图可知,加入相位抖动后,由相位截断误差造成的单根幅值较高的谱线被打散,分布到底部噪声。杂散的抑制是以增加底部噪声为代价的,而底部噪声不会影响DDS的频谱。故采用此种方法抑制了杂散,最大抑制大于20 dB。

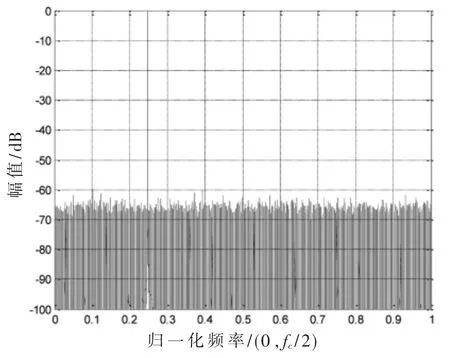

相位加抖的原理是利用周期更大的随机序列将误差序列的周期性打散,故随机序列的周期越大,对杂散信号的抑制越大。改变随机序列的参数,将 r(n)周期设为10 000采样点,DDS输出频谱如图7所示。

由此可知,增加随机序列 r(n)的周期,可以抑制底部噪声,但 r(n)的周期越大,硬件实现越困难。实际应用中,随机序列周期的选取应在硬件条件允许范围内尽可能降低底部噪声。

图6 随机序列r(n)=1 000 000时DDS输出频谱

图7 随机序列r(n)=10 000时DDS输出频谱

3 DDS的硬件实现及测试

本文的硬件实现平台为Xilinx的Virtex-5芯片,在此FPGA平台上实现DDS[6]。ADC为ADI公司的AD9709,它是一款支持最高采样速率为125 M、具有双通道、数据精度为8 b的数模装换器。

本文实现的DDS作为某跳频系统项目中的跳频器使用,对采用改进结构后的DDS指标进行了测试。跳频频谱图如图8所示。

图8 改进DDS结构前跳频频谱图

其中,频段为5 MHz~15 MHz,跳频频率间隔为5 MHz,频率切换时间为10 ns,跳频驻留时间为 40 μs,杂散<-40 dBc。

频谱仪实测的3个频点为 5 MHz、10 MHz、15 MHz。由于DDS为数字系统,当它从一个频率转化到另一个频率的切换时间应为一个时钟周期,即10 ns。由图可以得出跳变频率的杂散低于-40 dBc,采用改进结构后,DDS杂散抑制度提高。

4 总结

本文给出了基于Xilinx Virtex-5芯片实现跳频系统中的DDS,并对ROM查找表的结构进行了优化,节省了ROM资源,更重要的是从根本上有效地抑制了相位截断误差和幅度量化误差。同时采用相位抖动和非平衡DAC的改进结构对杂散进一步抑制。实测结果表明,跳频器的杂散抑制优于40 dBc。改进后的DDS杂散小,频谱纯度高,性能优越,易于实现。

[1]刘晨,王森章.直接数字频率合成器的设计及 FPGA实现[J].微电子学与计算机,2004,21(5):63-65.

[2]李衍忠,蔡英杰.DDS谱质分析及其杂散抑制研究综述[J].现代雷达,2000,22(4):33-38.

[3]KROUPA V F.Phase and amplitude disturbances in direct digital frequency synthesizers[J].IEEE Transactions on Ultrasonics,Ferroelectrics,and Frequency Control.May 1999,46(3):481-486.

[4]孟玉洁,贾际义,陶成.DDS中几种关键的ROM压缩方法[J].天津通信技术,2004(1):37-39.

[5]卫恒,王德功.基于改进 DDS算法的任意信号发生器设计[J].电子技术应用,2015,41(6):38-41.

[6]刘争,李昆.基于 Verilog HDL的 DDS设计与实现[J].电子制作,2015(3).

Design and implementation of the improved structure of DDS based on FPGA

Wang Shuo,Ma Yongkui,Gao Yulong,Zhang Shiwei,Zhao Donglai

(Communication Research Center,Harbin Institute of Technology,Harbin 150001,China)

The principles and spectrum of digital frequency synthesizer(DDS)have been introduced in this paper.Three methods that constitute the improved structure of DDS have been given,including the ROM compression algorithm that saves storage space, the phase jitter injection method that restrains phase truncation error,and the balanced DAC structure method that reduces the influence of its non-ideal characteristics.Stray interference caused by the periodicity of the random sequences,employed for phase jittering,has been analysed through simulations.Moreover,this paper has also implemented the improved structure of DDS in an universal FPGA platform.The test results show high stability and spurious suppression which is better than 40 dBc,when the improved DDS is used for frequency hopper.

DDS;spurious suppression;phase jitter;FPGA

TN949.6

A

10.16157/j.issn.0258-7998.2016.03.008

王硕,马永奎,高玉龙,等.基于 FPGA的改进结构的 DDS设计与实现[J].电子技术应用,2016,42 (3):28-30,34.

英文引用格式:Wang Shuo,Ma Yongkui,Gao Yulong,et al.Design and implementation of the improved structure of DDS based on FPGA[J].Application of Electronic Technique,2016,42(3):28-30,34.

2015-07-30)

王硕(1992-),女,硕士研究生,主要研究方向:跳频通信系统的FPGA实现。

马永奎(1973-),男,硕士研究生导师,主要研究方向:扩频通信传输技术、高灵敏度卫星导航接收机算法。

高玉龙(1978-),男,硕士研究生导师,主要研究方向:认知无线电、通信信号处理、软件无线电等。

国家重点基础研究发展计划(61301101);国家自然科学基金项目(2013CB329003)