基于PCI-E的北斗导航授时卡设计*

2016-11-21孙慧婷

王 军,孙慧婷,姜 志,王 磊,何 昕

(1.苏州科技大学,江苏苏州215009;2.中国白城兵器实验中心,吉林白城137001;3.中国科学院长春光学精密机械与物理研究所,长春130033)

基于PCI-E的北斗导航授时卡设计*

王军1,3*,孙慧婷1,姜志2,王磊1,何昕3

(1.苏州科技大学,江苏苏州215009;2.中国白城兵器实验中心,吉林白城137001;3.中国科学院长春光学精密机械与物理研究所,长春130033)

为提高Linux系统时间的精确度,设计了基于PCI-Express总线接口的北斗导航授时卡。北斗导航卫星信号接收模块输出时间定位信息,FPGA(Field-Programmable Gate Array,现场可编程门阵列)解出标准时间存入双口RAM,PCI-E驱动芯片将双口RAM内数据送到PCI-E总线供上位机调用。实验结果证明:授时卡在Linux系统下运行稳定,功耗较低,授时精度达到60 ns。

Linux;PCI-Express;FPGA;授时

计算机时间基本由网络时间或主板时钟芯片提供,导致时间误差大,在工业控制、数据测量等领域无法完成特定任务。为解决计算机时间误差较大问题,部分学者提出基于Windows系统PCI总线接口的GPS授时卡[1-2]。这种方法的不足在于:数据吞吐量、带宽的限制使得PCI总线逐渐被PCI-E总线所取代,且GPS授时方式以及美国微软Windows系统无法在国家安全敏感部门使用。针对上述不足,基于开源Linux系统,设计了PCI-E总线接口的北斗授时卡。

1 PCI-E授时卡总体设计

授时卡总体设计了3个模块:北斗卫星解码模块、可编程逻辑器件以及PCI-E驱动模块,总体框图如图1所示。北斗卫星解码模块通过天线接收北斗卫星授时信号,将$GPRMC格式码流传输给FPGA串行通讯模块,FPGA解出$GPRMC码中的时间定位信息输入到双口RAM中。PCI-E驱动模块在接收到计算机的命令后将时间信息传输到PCI-E总线上供计算机应用层软件获取[3-5]。

图1 授时卡总体硬件框图

2 授时卡硬件设计

可编程逻辑器件 FPGA采用 Altera公司CycloneⅣ系列中的EP4CE22E22C8N,该芯片具有144个IO端口、36个RAM块、2个PLL锁相环、18个嵌入式乘法器、4种配置方式和AS、JTAG下载调试接口。北斗卫星解码模块采用和芯星通UM220-III为主芯片,授时精度可高达15 ns,与FPGA采用串口通信且有多种波特率可供选择,只要保证有一颗卫星连接正常,芯片就能输出准确的时间信息。PCI-E驱动芯片采用PLX股份有限公司研发的PEX8612,支持I/O端口映射和扩展ROM以及中断,大大简化了授时卡硬件程序开发。授时卡部分硬件连接图如图2所示。

北斗卫星导航模块UM220与FPGA采用串行通讯,RXD与FPGA串行模块发射端连接,接收FPGA设置指令;TXD与FPGA接收端连接,输出时间定位信息码流;并通过PPS输出标准时间秒头至FPGA。PCI-E驱动芯片PEX8612将本地数据地址线分别与FPGA虚拟双口RAM的8 bit双向数据线、8 bit位单向地址线相连,通过读写信号线控制与FPGA进行数据交互;两对差分信号连接PCI-E金手指与计算机PCIE总线通讯[3-5]。

图2 授时卡部分硬件连接图

3 授时卡软件设计

3.1时间定位信息解码程序设计

北斗导航卫星UM220-III模块可输出标准GPRMC格式信息,各部分信息之间采用“,”隔开,定义如表1所示。

表1 UM220-III输出帧格式

FPGA解析数据帧主要采取状态机检测法,当检测到$GPRMC帧头,开始进入解码状态,检测到第1个‘,'字符,进入时间状态机,将时分秒h.min.s赋给时间变量;检测第2个‘,'字符,进入定位状态机,根据字符修改定位标志位;检测第3个‘,'字符,进入纬度状态机,将纬度赋给相应变量;之后按照上述思想,检测‘,'字符从而进入相应的状态机完成信息的提取。时间解码流程图如图3所示。

3.2PCI-E驱动芯片控制软件设计

FPGA利用IP核建立一个虚拟双口RAM包括时钟信号、读写使能信号、读写地址以及读写数据。FPGA将写地址、时间数据放到地址线和数据线上,完成时间的解码后产生一个写使能信号,时间数据写入到固定的寄存器。将北斗导航卫星接收模块输出的PPS信号当作PCI-E驱动芯片的硬件中断信号,当Linux系统应用层软件使能硬件中断,进入中断子程序对PCI-E总线设备端口读时间数据,PCI-E驱动芯片将PCI-E总线协议数据读写转化为读取FPGA虚拟双口RAM的读写[6-9],流程图如图4。

图3 时间解码流程图

图4 PCI-E总线时间信息读取流程图

4 测试结果

实验计算机采用华硕主板,Intel酷睿i5-4590处理器主频3.3 GHz,4G内存,操作系统为Ubuntu Kylin 15.04,内核版本Linux 3.19.0。打开终端窗口,使用insmod命令加载PCI-E驱动模块如图5,并且通过lsmod命令检测驱动是否加载成功,驱动模块显示列表如图6。

图5 驱动加载命令图

图6 驱动模块显示列表图

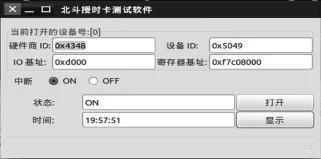

驱动加载完毕后,打开采用GTK+函数库编写的授时测试软件出现图7界面,输入设备号点击“下一步”按钮就会出现图8授时卡应用软件主界面。从主界面中能够查询硬件商和设备编码,以及I/O和寄存器基址。点击“打开”按钮打开授时卡中断,状态栏显示ON状态表示设备中断打开,点击“显示”按钮就能显示标准北京时间。

图7 授时卡应用软件初始界面图

图8 授时卡应用软件主界面

使用Tektronix公司的TDS-2014C示波器检测北斗卫星标准秒头(橙色)与授时卡授时秒头(绿色)误差60 ns,波形如图9。

图9 授时秒头与标准秒头波形图

5 结论

Linux系统下设计的北斗授时卡采用 PCI-E桥接芯片,缩小PCI-E总线开发过程,简化硬件语言开发难度。北斗卫星导航授时有效克服GPS授时安全问题,且授时精度高、兼容性好,在Linux系统下运行稳定,为Linux系统时间校对提供一种新方法。

[1]刘军良,胡永辉,候雷.基于PCI总线的GPS授时卡设计[J].电子测量与仪器学报,2008(s2):122-127.

[2]赵志雄,李孝辉,刘娅,等.PCI总线的高精度大量程时间间隔计数器研制[J].电子测量与仪器学报,2014,28(12):1317-1323.

[3]鞠康.基于FPGA的PCI-E数据采集电路设计[D].哈尔滨:哈尔滨工业大学,2014.

[4]杨子元,包启亮,王旭.基于PCIE/104总线的高速数据接口设计[J].现代电子技术,2011,34(14):75-78.

[5]李木国,黄影,刘于之.基于FPGA的PCIe总线接口的DMA传输设计[J].计算机测量与控制,2013,21(1):233-237.

[6]雷雨,任国强,孙健,等.基于PCIE的高速光纤图像实时采集系统设计[J].电子技术应用,2013,39(10):136-140.

[7]李玉峰,韩晓红,刘洋,等.基于FPGA的高速数据采集系统的实现与性能分析[J].电子器件,2012,35(6):709-712.

[8]信侃.基于Xilinx FPGA的PCIe总线接口设计与实现[J].无线电通信技术,2014,40(4):94-97.

[9]孙晓晔.基于PCIE的SG DMA高速数据传输系统[J].计算机技术与发展,2013,23(9):195-199.

王军(1979-),男,汉,江苏徐州,苏州科技大学副教授,博士,主要研究方向为光电测控技术与仪器;

孙慧婷(1992-),女,汉,江苏东台,苏州科技大学硕士研究生,硕士,主要研究方向为智能信息处理。

Design of Beidou Navigation Timing Card under Linux PCI-E Bus*

WANG Jun1,3*,SUN Huiting1,JIANG Zhi2,WANG Lei1,HE Xin3

(1.Suzhou University of Science and Technology,Suzhou Jiangsu 215009,China;2.Bai Cheng Ordnance Test Center of China,Baicheng Jilin 137001,China;3.Changchun Institute of Optics,Fine Mechanics and Physics,Chinese Academy of Science,Changchun 130033,China)

To improve Linux system time accuracy,timing card was designed based on PCI-Express interface by Beidou navigation satellite.Module receives Beidou navigation satellite signal and outputs time location information,FPGA(Field-Programmable Gate Array)decodes time and puts it into dual-port RAM,PCI-E drive sent time data to the PCI-E bus for system transferring.Test results show that card is stable and low power,and the timing error is 60 ns under Linux system platform.

Linux;PCI-Express;FPGA;timing

TN927

A

1005-9490(2016)05-1063-04

项目来源:国家自然科学基金项目(61472267);江苏省普通高校研究生科研创新计划项目(KYLX15_1311);苏州科技大学研究生创新项目(SKCX15_050)

2015-10-17修改日期:2015-11-18

EEACC:633010.3969/j.issn.1005-9490.2016.05.009