基于PLC技术的并行定时器设计研究

2016-10-21陆雪影

陆雪影

【摘要】PLC中自带有定时器,但是一般PLC自带的定时器数量有限,在有有的应用中,较少的定时器数量难以PLC的应用,为此,需要通过外扩定时器来满足PLC应用的需求。在本文的研究中,对基于PLC的外扩256个并行外部定时器进行研究。

【关键词】PLC技术;并行定时器

定时器指令是PLC工作运行中的重要指令,可以进行构造时序、人为制造中断等各种应用,是PLC应用中不可或缺的重要手段。

1. 定时器设计

常用的PLC微控制器的内部定时器数量有限,在有大量定时任务需要完成时,PLC自带的内部定时器难以满足应用的需求,因此需要通过外扩定时器芯片,来实现大量定时器单元的设计。

1.1 总体结构设计

在本课题所研究的并行定时器中,实现了256个定时范围为1~228,最小定时时间为1ms定时器。由于并行定时器的定时范围宽、单元数量多,因此采用并行方式执行,在较短的时间内对所256个定时单元进行扫描,完成一次定时操作。

为了节省接口数量,并行定时器单元的输入输出接口采用双向I/O接口。外部控制器访问定时器的方式是按照一定的时序实现数据的写入和读取,定时器内部定时单元的访问和操作通过相应命令来控制。定时器的内部框架图设计如图1所示。

1.2 定时器命令设计

在定时器总体设计过程中,PLC与并列控制的外部定时器之间通过命令的方式来实现数据的交互。定时器的命令范围控制命令和读取命令两种。在PLC与外部定时器进行数据通信的过程中,为了保证256个外部定时器单元初始化成功和正确读取,PLC的输入输出频率应该在300kHz以上。在PLC的地址总线中,输入0x000-0x0ff表示256个定时器中某个定时器的编号,而0x00-0x120表示将256个定时器划分为8组每组数量为32个定时器的中断标志组,通过分组可以更快的实现对定时器的初始化和读取操作。

(1)控制命令

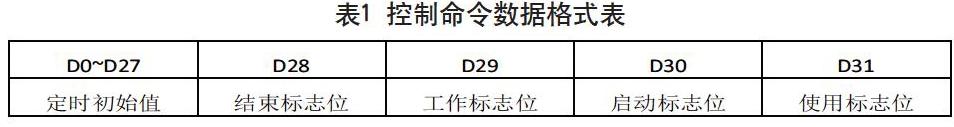

PLC向定时器单元发送的初始化、启用、停用、暂停等控制命令,控制命令的输入格式如表1所示。

通过设置相应的定时器地址,并且输入定时器初始数据,PLC就可以控制256个外部定时器单元中的某个定时器启动,当启动标志位和使用标志位同时置1,并且结束标志位和工作标志位同时置0时,控制外部定时器开始工作。当启动标志位或者使用标志位中的某个位置0时,定时器停止工作,并且载入初始值,等待下一次被PLC启用。

(2)读取命令

的那个RW端置高电平后,PLC可以访问定时器单元内的定时数据来获取相应的定时状态和定时值信息。当读取命令的输入地址为0x100时,可以并行读取1个定时器单元组中的32个外部单元的数据,0表示定时单元未启动或者未结束,1表示定时器时间到达。

2. PLC程序控制

PLC程序是指PLC并行控制256个外部定时器单元的程序。程序的主要模块分为如下五个部分的内容。

2.1 1kHz分频模块

分频模块将50MHz的方波进行分频,实现分频为50%占空比的1kHz频率信号输出。在分频时需要一个计数器进行输出控制,计数器的计算公式如式(1)所示。

(1)

根据式(1)计算得到计数次数为25000,因此当技术次数为25000时,输出1kHz取反,获得50%占空比的1kHz方波。

2.2 地址计数模块

在访问两端RAM时,通过地址技术模块输入地址,当PLC模块需要读取外部定时器中的定时数据时,地址计数器模块停止计数,在完成读取操作后,继续进行地址增加,在完成一个循环之后,等待下一次1kHz脉冲到达。

地址计数采用11位寄存器,11个寄存器的低3位保持地址持续时间,在8个时钟周期的持续时间中,完成一次单元操作。在单元操作完成后,地址计数器累加,地址计数所指向的地址后移。

2.3 计时与逻辑控制模块

计时与逻辑控制模块读取两端口RAM中的数据,读取RAMCR中的数据并判断当前定时的定时状态和定时初始值;读取RAMCE中的数据,进行减操作,开始进行定时。如果在计时与逻辑控制模块运行过程中发现了定时结束的定时单元,则将RAMCE中的D27和D28位置分别设置为0和1,如果定時单元未技术则设置为1和0,其余情况设置为0和0。

3. 总结

PLC中自带了定时器以满足一般应用的需求,但由于PLC所在带的定时器较少,因此难以满足复杂应用的需求。在本文的研究中,采用PLC未接定时器的方式来扩充PLC的定时器的数量,并通过并行处理来提高定时器工作的实时性,提高定时器计数和定时的准确性。

参考文献

[1]孙志雄,谢海霞.基于FPGA的高速串并/并串转换器设计[J].现代电子技术,2014,(8):151-152.

[2]李克俭,付杰,蔡启仲,等.基于FPGA的串行定时器设计[J].广西工学院学报,2012,23(3):61-65.

[3]张炜,李克俭,蔡启仲,等.基于FPGA的PLC并行定时器的设计[J].计算机工程与设计,2013,34(4):1244-1249.