基于FPGA的LCD显示控制系统的设计

2016-10-19徐畅

徐畅

渤海大学工学院

基于FPGA的LCD显示控制系统的设计

徐畅

渤海大学工学院

本文主要介绍了关于LCD的视频控制芯片设计方案,介绍了系统功能的实现,以及FPGA的实现原理,LCD驱动原理,解决了DSP,LCD和FPGA,之间的协同合作的难题。

LCD FPGA LCD驱动

随着电子工程的不断发展,嵌入式系统的应用不断扩展,实现人机信息相互交互的界面已经是社会的趋势。通过研究发现以往的发光二极管已经无法满足市场的需要。发光二极管的显示控制部分比较简单,功能太少,无法对复杂的信息进行显示,而且控制起来也不方便。相于是LCD液晶显示器应运而生,代替了传统意义上的发光二极管,并且LCD在智能仪器的应用极为宽广。

很多的LCD是静态显示的,LCD的控制器大部分是以单片机为主,并且只能进行显示而不能实现实时交互。程序在执行的过程中只能一步一步进行,不能进行多任务并发进行。本论文是基于FPGA的LCD显示控制,硬件描述语言选择的是Verilog,SPARTAN系列选择的是XC2S50。通过Verilog进行语言文字的显示和控制。

1 LCD的概述

液晶显示的LCD做为一种目前比较流行的平板显示器件,它的形成是在电场存在的情况下从而导致液晶材料的位置进行了改变,最后透光性能进行了遮蔽。

根据商品的形式不同可以将LCD分为以下几种:

1.1液晶显示模块

该显示模块简称为LCM,该模块由三部分组成,分别是IC驱动,组装线路板和其它之类的商品。

1.2液晶显示屏

显示屏通常又可以称为LCD屏,该屏中的设备驱动程序是由使用者自己设计的。

根据LCD显示的形式不同,可以分为以下几种:

(1)单色显示。

顾名思义指的就是只有白色和黑色两种颜色,要么背景是黑色的,文字是白色的,要么背景是白色的,文字是黑色的。两种颜色相互间隔。

(2)彩色显示。

其中的彩色显示又可以分为两种,单彩色以及多彩色,并且这个多彩色中还分为真彩色以及伪彩色,他们的区分是根据显示的颜色总数进行的,8到32色的称为伪彩色,而256种颜色的称为真彩色。

LCD的器件分为TN,STN和TFT三种型号,这三种型号的性能是不断提高的,同时相对着相关的成本也就会增多。单色LCD制作中通常选择的型号是STN和TN两种,真彩色的LCD通常选择TFT。

LCD的显示离不开由LCD控制组成的驱动电路,这是LCD实现显示功能的首要前提,该基本的驱动电路是由背光电路,震荡电路以及供电电路等组成的。LCD的LCD的驱动程序中往往采用的是汇编或者C语言进行编程,这些驱动程序通常涉及到的有初始化,管理和数据处理程序。

2 FPGA的概述

随着信息时代的到来,工程领域的不断发展,可编程逻辑技术在电子工程领域的应用越来越广,一些新型的嵌入式产品的不断诞生,表明现代的工程技术将会不断的走向系统化,集成化以及电子化的发展道路。

FPGA是Field Programable Gate Array的缩写,从英文名称介绍可以知道指的是现场可编程的门阵列的意思,FPGA是以GAL,PAL和EPLD为发展基础的,在系统设计中得到了广泛的应用,其特点是系统的功耗比较低,逻辑容量的密度比较大。目前生产研发FPGA知名度比较高的公司主要有Lattis公司,Altera公司和Ximlinx公司等等。同时FPGA的前进目标是软件开发,工具开发和工艺器件方向这两个方向。FPGA在20世纪90年代进入了发展的黄金时代,2000年可控端口的数量相比于1990年增加了将近200倍。FPGA的硬件语言大体分为VHDL和Verilog HDL这两种。FPGA在发展的初步阶段使用的就是VHDL,而Verilog语言的前身是从C语言来的,因此大部分的编程者更倾向于用VHDL语言进行编程,VHDL的发展历程悠久,所以语法规范性,结构性都比较强,功能比较强大,Verilog语言的发展时间还不是很长,所以语法掌握起来比较容易,比较适合入学者。

FPGA模块部分拥有很多的功能,如下所示:

(1)产生驱动时序。因为不同类型的LCD,其显示面板上的刷新频率也不同,所以相应着他的分辨率参数也不相同。参数不同也就会导致产生不同的时序。所以FPGA电路模块的核心功能是如何使得时序的驱动程序是正确的。

(2)FPGA芯片中还包括了调节亮度,调节对比度等等。FPGA选择主要是以器件的功耗,性能,速度等因素进行选择。

3 LCD的驱动

3.1驱动分类

(1)静态驱动

静态驱动的基本原理是在相对应的一对电极间连续外加电场或者是连续不加电场。其中驱动的波形指的是当同相时液晶上没有电场,当反向是时液晶的上面就会添加一个矩形的波形。当这个添加的矩形波形的电压比液晶所设置的阀值还要高的时候,此时LCD就可以认为是选通的状态了。

(2)多路驱动

当电极是沿着X和Y的方向形成矩阵的时候,根据顺序依次把选通的波形给X电极,Y电极上施加的选通波形或者是非选通的波形和X电极上是同步的。

从多路驱动的原理中分析可以知道,电压会施加给选通相素也会施加给非选通的相素,为了实现选通的相素受选通电压的控制,非选通的相素受非选通的电压控制,LCD在光电性能方面的阀值必须要越大越好。

根据系统的要求,本论文中选择LCD液晶显示的器件是MTG-F32240X,该器件的像素是320*240,LCD的器件型号是FSTN,显示的方式是图形。

图1 LCD接口时序

3.2LCD显示驱动原理

该类型的液晶显示器的接口时序中所用到的驱动信号为CL1,CL2和FRM,目前该信号的工作频率可以参考如下:CL2=1.28MHz,CL1=16KHz,FRM=66Hz。LCD的驱动过程主要是首先移位脉冲CL2发出80个后,紧接着发出行频脉冲CL1,当CL1发出累计到240个后FRM信号就会跟着发出,当FRM信号发出结束后,这个过程是不断的进行循环,循环结束后液晶的显示控制过程也就结束了。接口时序图如图1所示。

4 选择显示缓存区的存储介质

显示数据以及处理数据的相关性不能太高,必须尽可能降低,可以通过把数据缓存的设备加入到系统设计中,从而让主处理器摆脱了操作上的单一性。目前数据缓存区的介质主要有两类,分别是FPGA内部双口和SRAM。本文采用的是FPGA内部双口RAM作为缓存区的存储介质。因为如果采用SRAM,可编程资源损耗过多,而且系统的稳定性受控制单元的直接影响。

该系统选择了前者作为存储介质的考虑因素,主要体现在:1、数据显示的连续性得到了实现;2、完成了16bitsDSP与LCD 4bits的数据格式的相互转化。本系统的显示数据缓存是2Kbytes的存储单元。

5 基于FPGA的LCD驱动器实现

LCD的驱动实现离不开驱动信号CL1,CL2以及FRM。缓存区端口地址是驱动信号决定的,当显示数据之前需要把中断数据的请求提交给DSP,然后DSP收到请求后就就继续进行下一帧数据的传送。

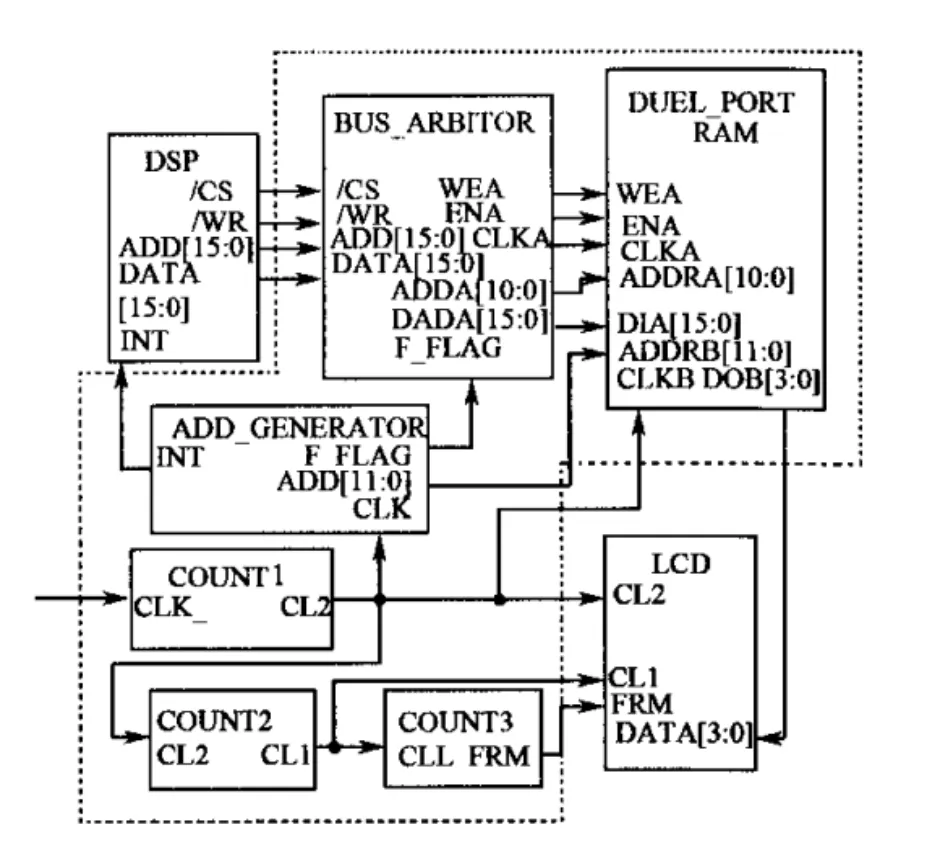

图2 LCD驱动结构图

从图中可以看出,当地址是在E00H之后时帧的数目就会发生改变,BUS-ARBITOR单元专门是记录帧的数目,接收到帧数目后中断传送的通知就会停止。缓存BUS-ARBITOR单元的显示是通过DSP进行刷新实现的。

由于定时中断的原因,所以DSP数据处理部分需要进行打断,通过资源占有率来指明部分功能对其他流程的影响情况。资源占有率用POC表示,是中断一次响应的时间ti与中断两次的时间tii之间的比值,如公式(1-1)所示:

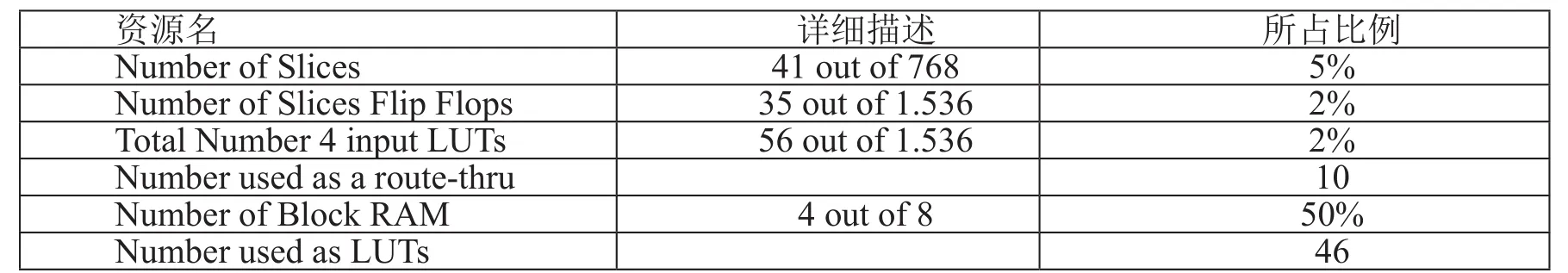

这个模块采用了VHDL描述语言,硬件资源占用情况如表1所示。

6 结语

本论文实现了基于FPGA的LCD显示控制器,介绍了LCD的相关理论知识,LCD的驱动原理以及FPGA的实现原理。本文论述了通过结合DSP。FPGA以及LCD的相互结合可以增强主要器件的工作性能,为工作的顺利完成提供了保证,也为软件硬件的设计提供了方案。

[1]周鹏,李圆圆. 基于FPGA的LCD液晶动态显示驱动程序的设计[J].电子质量,2014(11): 34-42.

[2]廖超平.基于FPGA的信号发生器按键LCD模块设计[J].科技资讯,2013 (26): 1-2.

表1