基于VHDL语言的数字钟层次化设计与实现

2016-10-13胡宏梅

胡宏梅

(苏州健雄职业技术学院 电气工程学院,江苏 太仓 215411)

基于VHDL语言的数字钟层次化设计与实现

胡宏梅

(苏州健雄职业技术学院 电气工程学院,江苏太仓215411)

EDA技术的关键就是用硬件描述语言来描述数字系统,简化了数字系统的设计过程。利用VHDL语言描述数字钟系统,采用自顶向下的方式设计,详述了数字钟底层文件中每个模块的设计思路,及顶层文件的生成,并通过下载仿真,最终实现了系统的设计,具有一定的可行性。

EDA技术;VHDL语言;数字钟;逻辑电路图;层次化设计

0 引 言

现代电子设计技术的核心是电子设计自动化技术,即EDA技术。利用EDA技术,电子设计师可以方便地实现IC设计、电子电路设计和PCB设计等工作,使电子系统设计更为简化和方便。它是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要方式,其中,VHDL语言已成为系统描述的国际公认标准,得到众多EDA公司的支持,越来越多的硬件设计者使用VHDL描述数字系统,综合效率和效果较好[1]。

本文详述使用VHDL语言实现对数字钟的层次化设计,将文本编辑和图形编辑两种方式混合使用,设计和实现数字钟对时、分、秒的计时。显示满刻度为23时59分59秒,再来一个脉冲,重新开始计时,最终通过将CPLD/FPGA开发系统上实现下载仿真。

1 系统设计框架

数字钟是一种用数字电子技术实现秒、分、时计时的钟表,实际上就是对标准频率(1 Hz)计数的计数电路[2]。

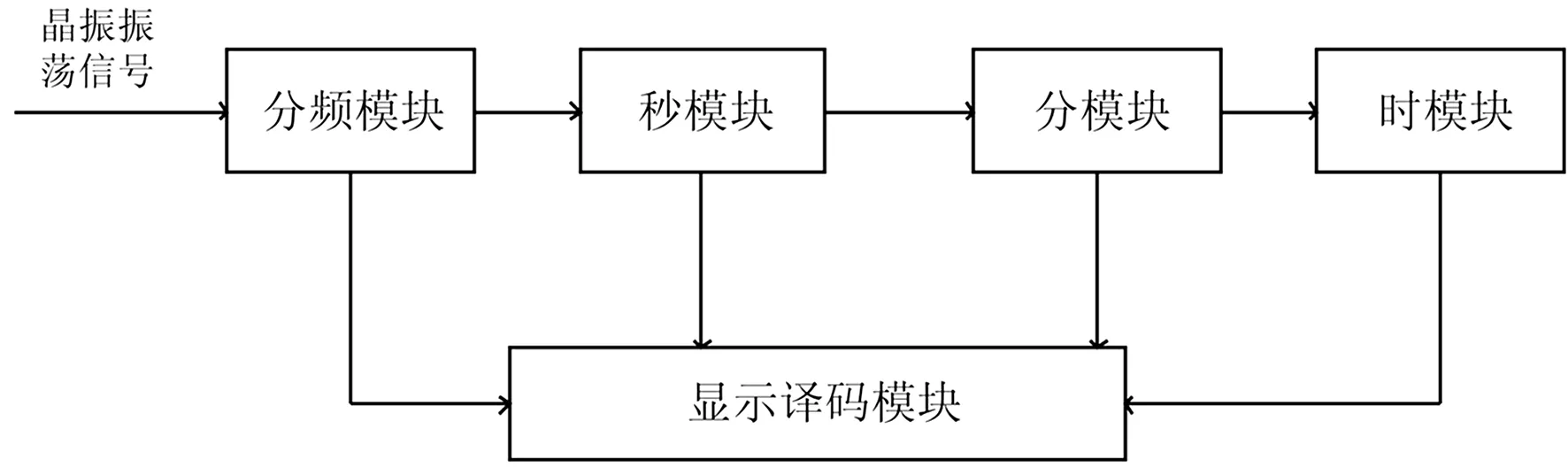

本文采用自顶向下的设计方法,底层文件为实现功能的模块设计,在文本编辑器中完成,各模块由VHDL语言编程实现。底层模块包括分频模块、分/秒模块、时模块及动态扫描模块组成,具体设计框图如图1所示。顶层文件是在图形编辑器中通过添加每个模块的逻辑符号,根据其逻辑关系进行连线,最终形成,如图2所示,FREQUENCY 是分频模块,SECOND_FEN是分/秒模块,HOUR是小时模块,DISPLAY为译码模块,SAOMIAO为扫描间隔模块,DONG_DISPLAY为扫描显示模块[3]。

分频模块:输入脉冲信号由石英晶体振荡器产生,由于晶振输出频率较高,为了得到1 Hz的秒信号,需要对振荡器的输出信号进行分频,作为数字钟的时间基准,然后经过分频器输出标准的秒脉冲;

秒模块:振荡信号经分频模块后产生秒信号,激励秒模块进行加1计数,计数60次开始向分模块产生进位;

分模块:秒模块的进位脉冲作为分模块的输入,计数60次开始向时模块产生进位;

时模块:小时模块接受到分模块产生的进位开始计数,计数24次归0;

译码显示模块:将秒、分、时的计数通过数码管进行译码显示,由七段译码器完成。

图2给出了该系统顶层设计文件。

图1 系统设计框图

2 底层文件设计方案

2.1分频模块

在数字逻辑电路设计中,分频器是一种基本电路,通过分频可以得到需要的时钟频率。常见的分频器有二进制分频器、偶数次分频器、奇数次分频器、占空比可调的分频器和小数分频器。分频的方法很多,最常见的就是利用加法器对时钟信号进行分频,当然也可以利用一些专用的电路结构来实现。

图2 系统逻辑电路图

N分频器是指产生的输出信号频率fout为输入信号频率fin的 1/N,即:

分频的实现是通过对输入信号脉冲计数,每计数N/2个脉冲,输出信号反相而的得到的。

图3 分频模块设计

本实验平台上有22.118 4 M ,10 M晶振,4 M(可分频至1 000 Hz)晶振,分别接在CPLD芯片的管脚P80,P183,P184,为实验器提供时钟信号。本文选择采用对10 M时钟信号进行脉冲法计数,计到4 999 999次,输出信号反相,即可产生频率为1 Hz的输出信号。具体分频思路如图3(a)所示,检查编译后,生成的逻辑符号如图3(b)所示。

2.2分/秒计数模块

分/秒计数为60进制的计数,分为个位和十位,其中,十位实现的是0到5的计数,个位是0到9的计数,在计数到59时,产生进位信号,如图4所示。

图4 分/秒模块设计

2.3时计数模块

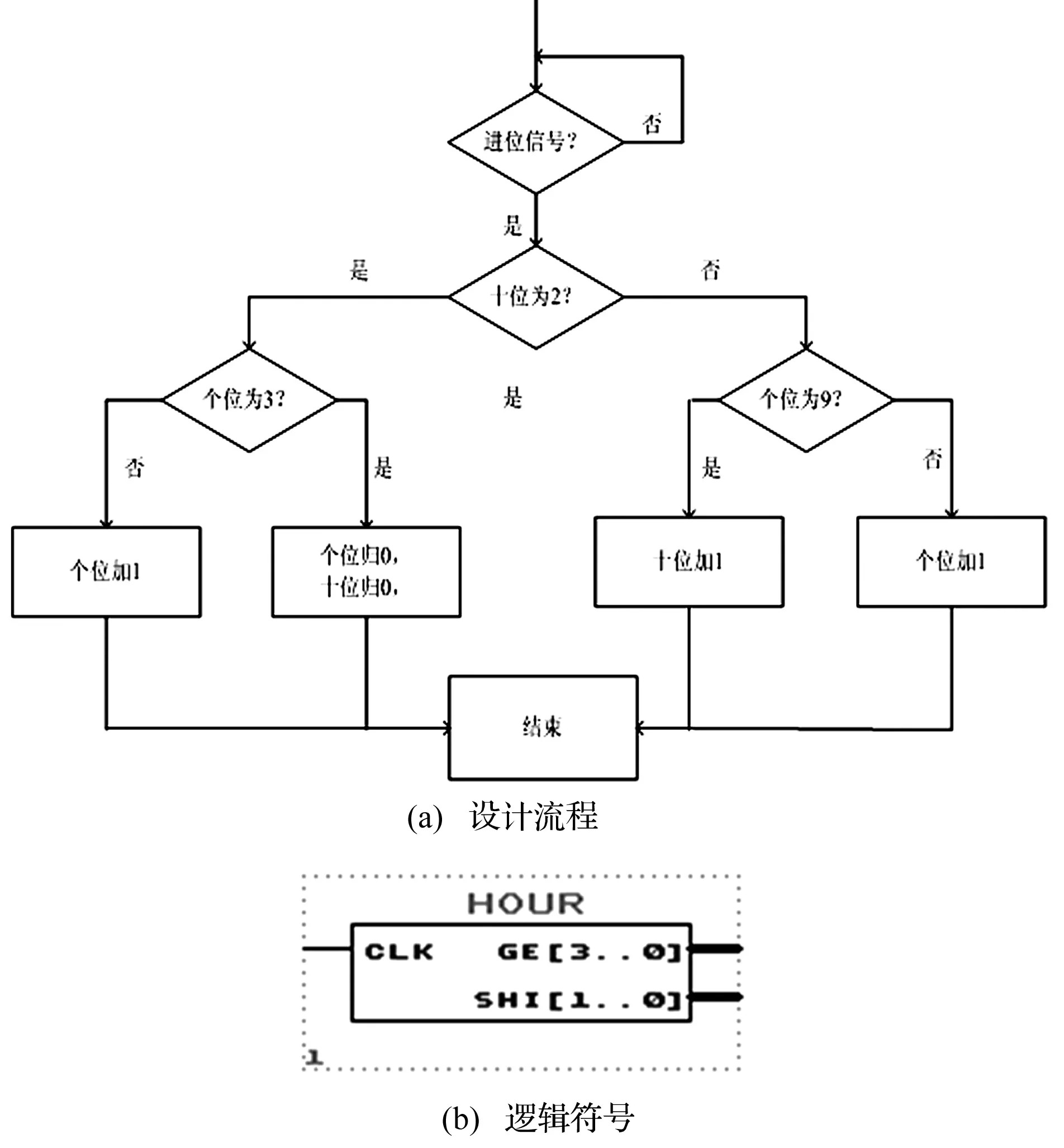

时信号的计数规律是当十位为0和1时,个位计数为0~9,个位计数到9,则往十位进位,个位归0;而十位计数到2时,个位只能为0~3,计数到3,则十位和个位共同归0,具体设计思路如图5(a)所示,所生成的逻辑符号为图5(b)所示。

图5 时模块设计

2.4译码模块

图6 译码显示模块

将秒计数、分计数、时计数编译成数码管的段码,送给动态扫描模块,供数码管显示。秒/分计数的个位共可显示0~9的数,需用4位二进制表示;而秒/分计数的十位可显示的是0~5的数字,需用3位二进制表示;而时计数的个位与十位只需2位二进制表示;所以会有三种译码模块,如图6所示。

2.5动态扫描模块

图7 动态扫描模块逻辑符号

动态扫描模块中包括扫描间隔模块和扫描显示模块,如图7所示。其中,扫描间隔模块作用是产生扫描时间,控制扫描模块的扫描时间;扫描显示模块即轮流向各位数码管送出字形码和相应的位选,利用发光管的余辉和人眼视觉暂留作用,使人的感觉好像每个数码管同时都在显示[4]。

本平台有10个数码管(SEG1~SEG10),采用共阴极8段LED显示。其中,SEG1—SEG6采用静态显示方式,SEG7—SEG10采用动态扫描显示方式。所以本文选择秒的显示采用静态显示方式,时、分的显示采用动态扫描显示[5-6]。

3 结束语

本文将按上述的设计思路编程、下载、仿真,开发环境为MAXPLUSII,检查编译,分配管脚,生成可以下载的后缀名为.pof的文件。选择的目标器件为EP1K30QC208-3,为ACEX1K系列,在KHF-1型CPLD/FPGA实验开发系统中实现仿真,最终可以实现时、分、秒正常显示。

[1] 廖超平. EDA技术与VHDL实用教程[M].北京:高等教育出版社, 2007.

[2] 李彦强,赵淑明. 用VHDL语言实现数字钟设计[J]. 山西电子技术, 2014,42(5):38-39.

[3] 纪欣然,丁一,梁致源. 基于FPGA的多功能数字钟设计[J]. 电子设计工程, 2012,19(16):177-179.

[4] 刘艳昌,王娜. 基于FPGA的多功能数字钟设计[J].河南科技学院学报:自然科学报, 2013,41(2):89-94.

[5] 郭小芳, 佘明辉. 基于单片机的多功能数字钟系统设计与分析[J]. 电子技术, 2012,39(6):35-38.

[6] 樊清海, 刘培培, 耿娟平. 基于单片机的数字时钟C语言设计[J]. 北华航天工业学院学报, 2010, 20(6):4-6.

Hierarchical Design and Implementation of a Digital Clock Based on VHDL Language

HU Hong-mei

(College of Electrical Engineering, Suzhou Chien-shiung Vocational Technical Institute, Taichang Jiangsu 215411, China)

One of the keys to EDA technology is to use a hardware description language (HDL) to describe the digital system, thus simplifying the design process of the digital system. VHDL is used to describe the digital clock system, and the design is completed in the top-down method. This paper describes in detail the design thought for each module in the bottom document of the digital clock as well as the generation of the top document. After downloading and emulation, the design of the system is completed finally. It has a certain reference value and is feasible to some extent.

EDA technology; VHDL language; digital clock; logic circuit diagram; hierarchical design

10.3969/j.issn.1000-3886.2016.01.036

TN79

A

1000-3886(2016)01-0113-03

胡宏梅(1982-),江苏太仓人,讲师,硕士生,研究方向:电子信息技术、通信与信息系统。

定稿日期: 2015-05-26