面向多任务密码处理的多核核间通信单元设计与研究

2016-09-26徐金甫

陈 帆 徐金甫 李 伟

(解放军信息工程大学密码工程学院 河南 郑州 450001)

面向多任务密码处理的多核核间通信单元设计与研究

陈帆徐金甫李伟

(解放军信息工程大学密码工程学院河南 郑州 450001)

为了解决面向多任务密码处理的多核核间通信机制的优化实现问题,设计一种混合通信机制。在分析多核处理架构及核间通信特点的基础上,融合了簇内共享存储通信和簇间NoC通信机制,同时引入了DMA通信机制,提出构建混合通信机制,进一步提升通信效率。其次,给出核间通信同步机制的优化实现,解决了同步和存储一致性冲突问题。最后,基于DesignComplier对设计方案进行了实验评估。实验结果表明,相比其他方案,该方案具有较小的资源代价和较高的性能指标,获得了满意的通信吞吐率。

多核密码处理器密码运算核间通信同步机制

0 引 言

信息安全领域中,单核密码处理器已无法满足密码算法日益增长的实现复杂性和高速性,因此多核密码处理器应运而生[1]。随着处理器数目的增加,如何有效地实现核与核之间的通信互联成为了突破多核密码处理器性能的关键[2]。

本文针对多核密码处理器的密码处理特性和核间通信需求,分析了密码算法处理特征,提出了符合密码算法硬件实现的混合核间通信架构,设计了核间通信同步模块,实现了多核处理器核间高效同步通信,并对其性能进行了评估。

1 多任务密码算法与核间通信机制分析与研究

1.1多任务密码算法分析与研究

当前的密码算法正朝着大位宽、多协议配合完成加密算法的趋势发展[3]。多任务密码处理结构是针对密码算法执行过程,按照多核并行处理模型的数据流特征将其拆分为多个处理子任务,并将子任务分别映射至各处理核单元,在时间与资源上保证密码算法执行的并行性。多核并行处理模型的数据流特征包括:基于任务拆分的多核并行处理模型、基于算法拆分的多核并行处理模型和安全协议多核并行处理模型[4]。

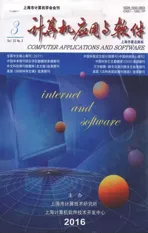

多核系统任务拆分工作流程如图1所示。

图1 多任务处理模型

任务分配单元按照密码处理任务的需求将多核系统重组成最佳执行模式,最大限度地提升密码处理的并行性。通过对多任务密码处理模型的分析可知,多任务密码算法实现加密处理任务的效率直接取决于核间数据传递的时效性。因此,多核系统的设计可通过优化核间通信单元及数据同步单元来提升多任务密码算法的实现效率。

1.2多核系统核间通信单元分析

目前,在密码多核处理器中,解决核间通信问题的方法主要有两类。一类是共享存储通信。如TI公司的OMAP4430[5],斯坦福大学的Hydra[6]等均采用共享存储通信,具有编程简单、易于利用软件编程实现通信调度的优点。但是由于访存带宽的限制,其可扩展性较差,随着处理核数增加,核间通信延迟显著增加,硬件开销也会迅速增加。另一类是消息传递通信。如麻省理工学院的RAW处理器[7],英特尔公司的80-Tile处理器[8]等均采用消息传递通信,具有较高的带宽和良好的可扩展性,适用于处理器数据较多的情况。但是随着处理核数目的增加,片上网络的通信延迟会明显增加,同时局部还会出现拥塞情况。

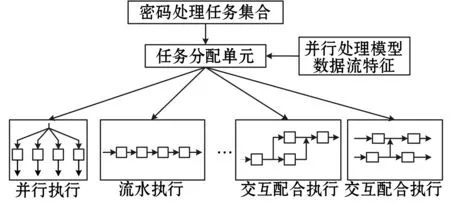

表1 共享存储与消息传递核间通信机制对比

通过分析表1总结的两种通信方式的特点及适用情景可知,当前主流的两种核间通信方式在针对不同通信需求的情况下各具优势。在实际应用中应按照实际通信情况进行合理选配不同机制。

1.3多任务密码算法对核间通信的需求分析

通过多核系统实现多任务密码算法,最大的优势之一就是多核系统相比于单核密码处理器能够提供更高的性能,而这种性能的提升并不是基于单核密码处理器的简单堆叠,而是通过充分挖掘多任务密码算法中的并行性,通过多核系统中高效的核间通信机制与同步技术有效地调度各处理器核单元,以此利用多核处理器在处理器数目上的优势来提高系统吞吐率。

基于上述分析,本文需要解决两个问题。第一,建立一种高效的核间通信机制。该机制能够支持较大的通信量和较小的通信延迟,同时能够便于扩展。第二,设计一种便于硬件实现且高效的数据同步方式,同时要能够与本文设计的通信机制有机衔接。

2 混合核间通信机制设计与实现

2.1混合核间通信机制

针对多任务密码算法对多核系统的通信要求,本文建立了一种混合通信机制。通过在设计中优化各通信机制的硬件实现,将多种通信方式集成在多核系统中。不同通信机制对应不同通信需求、多种通信机制并行配合使用,以此高效发挥各通信机制的优势。

针对簇内相邻核间通信,系统采用基于共享存储的通信方式,在簇内建立双缓冲结构的共享存储单元,以此实现相邻运算核心间数据的交互。双缓冲结构设计主要解决了数据“发送者”与“接收者”速度不一致、计算不同步所造成的数据遗失问题。第一级缓冲主要解决运算核心与第二级缓冲之间速度匹配问题,用较快的存储速度接收并暂存运算核心的计算结果,再以与第二级缓冲相匹配的速度将数据传递存储至第二级缓冲。第二级缓冲主要由共享存储单元实现,其作用是:主要依靠其较大的存储容量将第一级缓冲中的数据保存起来,等待数据接收者读取,完成核间数据交互。利用双缓冲结构的共享存储通信避免了簇内通信数据通过路由节点进行的数据包转发,以存储器的访问为代价有效减轻了片上网络的通信负荷。

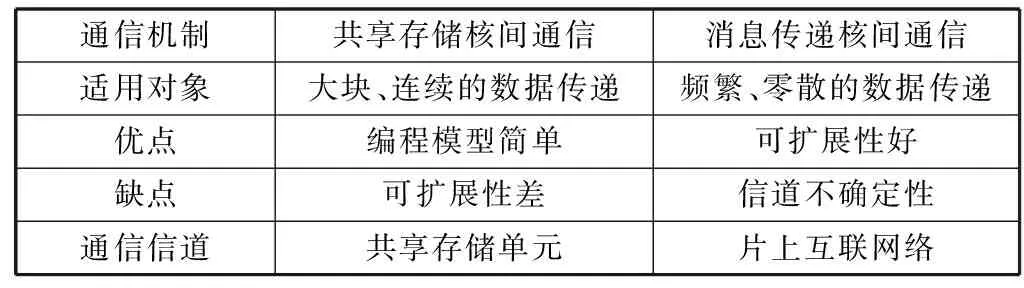

针对全局网络中簇间运算核心间的通信,系统采用基于片上网络的通信方式。通过“数据包头+数据包”的方式进行通信。本文设计的簇间通信数据包包头格式如表2所示。其中数据包长度代表了本次通信中数据包的个数;数据包包号代表了本次通信在本次运算任务中的执行位置;任务编号代表了本次通信所属的运算任务。

表2 数据包格式

通过建立簇间片上网络数据包通信方式,实现了整个网络上运算核心间通信数据的互联互通,保证了系统中任意运算核心间通信的灵活性。同时,由于片上网络通信方式中,数据包的传递在路由节点层,仅受路由节点互联结构的影响,与路由节点的规模无关。系统的扩展则只增加了路由节点的数目,而不影响路由节点的互联结构。因此片上网络的数据包通信方式保证了系统较好的扩展性。

由于片上网络的通信方式在数据交互时采用有限数据位的数据包进行交互,因此当大批量的数据在片上网络间进行交互时,片上网络负载较重,容易产生阻塞现象。因此针对簇间大批量数据传输的情况,本文引进了DMA传输方式也称为“直接存储器存取方式”[9]。该通信方式能够将相临共享存储单元之间存储的通信数据成批量进行传输,以减轻片上网络通信压力,同时减小通信时延。

通过三种通信机制的混合集成,在编写各个处理器核单元的执行程序时,根据通信的需求选用对应的通信机制。既保证了不同通信机制的优势得以发挥,又实现了多路通信的并行执行,降低了单一通信机制的通信负载。

2.2混合核间通信机制的硬件实现

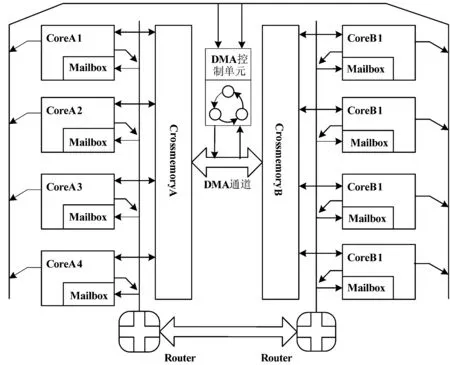

本文设计的混合通信机制硬件实现如图2所示。

图2 混合核间通信硬件结构图

在该多核通信系统中,整个系统通过路由节点(Router)进行互联与扩展,其中每个Router上连接四个密码处理核单元(CoreX)构成一个簇。在簇中,各处理核单元能够独立的与Router进行数据交互,通过Router对数据中转,以此实现数据在整个片上网络的互联互通。同时在每个簇内构建一个共享存储单元(Crossmemory),各处理核单元能够采用统一寻址的方式对Crossmemory进行数据读/写操作,以此实现簇内处理核单元的共享存储通信。在邻簇之间的共享存储单元间,建立一个DMA通道,DMA通道通过一个状态机控制通道的开关,两个簇中不同处理器核单元能够单独发出控制信号,以控制状态机状态转换。各处理器核单元本地设计了一个同步单元(mailbox),通过mailbox实现各通信机制的数据同步。

由文献[10]中,对算法操作特征的统计可知,分组密码的最大处理位宽一般不超过128bit、大部分序列密码处理的数据最大位宽都超过了128bit、杂凑算法本身独立的最大操作位宽一般不会操作128bit,但是其输出大小一般都超过了128bit。因此在本文设计的多核系统中,DMA通道定为256bit位宽,确保大多数密码算法通过DMA通道在一个周期内实现数据的传递。因为Router与Crossmemory因为与处理核单元要进行交互,所以数据位宽应与处理核单元保持一致,定为32bit。

2.3核间通信同步单元设计与实现

基于对多任务密码算法的分析可知,同步单元必须支持以下两种工作模式:①同步通信,即通信双方工作在同一对应任务下,通信数据均为本次任务所需数据。②异步通信,即通信双方工作在不同对应任务下,目的核未将任务1的数据读取完毕,源核已开始同步任务2的数据。

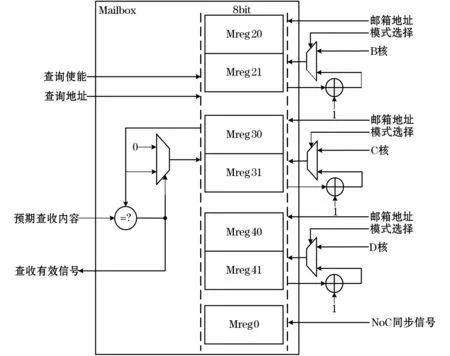

针对同步单元的要求,本文设计的邮箱同步模块,可以在硬件开销较小的情况下实现对共享数据一致性的保护。解决了多个处理器核访问共享数据存储单元时数据的读写先后顺序的问题。同步电路硬件实现结构如图3所示。

图3 邮箱同步单元硬件结构图

同步单元中针对本簇的另外三个核及簇间NoC同步,对应分别设计了一组寄存器。与处理器核对应的寄存器组由两个8bit的寄存器(Mreg**)组成,与NoC同步对应的寄存器组只包含一个8bit寄存器(Mreg0)。同步信号的传递通过硬连线的方式进行传递。在本地处理核单元中,由本核发送查询地址将指定寄存器中数据与预取数据对比,对比结果返回给本地处理器核。如果比对结果有效则清零相应寄存器。

同步机制设计中,针对不同的密码运算支持任务数、乒乓等不同的同步模式。针对不同的模式,在同步单元提供了两种同步方式——置数方式和“自加一”方式。通过模式选择信号采用不同的工作模式。同步过程中,由置数模式可控制通信任意长度的数据,由“自加一”模式可实现不同处理核之间的乒乓操作及规整的通信数据。

3 性能评估

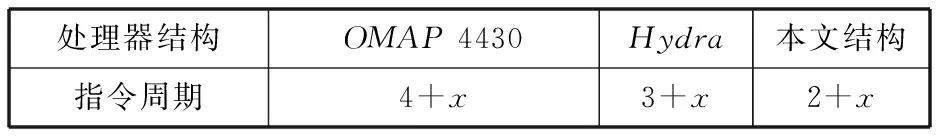

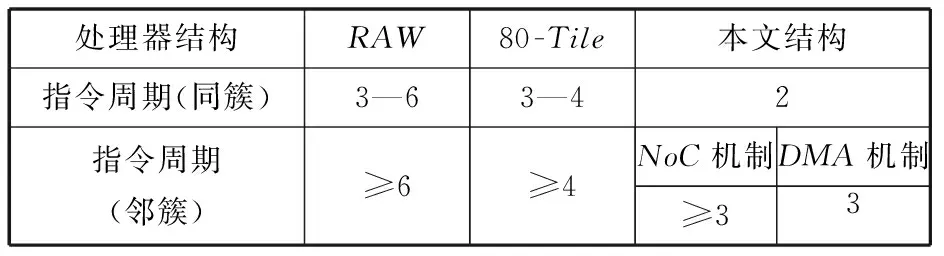

本文利用VCS仿真工具对三种通信机制进行了功能仿真,验证了其功能的准确性及时钟关系,验证结果如表3、表4所示。利用DesignComplier综合工具对本文设计的同步单元进行了综合验证,验证结果如表5所示。通过仿真、验证结果与文献中给出的处理器进行对比可知,本文提出的通信机制具有执行效率高、通信延迟短的优点,同步单元具有硬件开销小、同步效率高的特点。

表3 传输256 bit数据时共享存储通信机制对比情况

(备注:对比中,不考虑同步机制带来的影响,假设同步机制相同,且同步机制产生指令周期数为x。)

表4 传输一个数据包时NoC通信机制对比情况

(备注:本文结构下在邻簇传输情况下,NoC通信机制利用3条指令周期传输一个数据包,DMA通信机制利用3条指令周期传输256bit数据)

由表3、表4可知,在传输相同数据量时,本文提出的传输机制能够有效地提升数据传输速度,且随着通信核之间距离的增大,速度提升越明显。因此验证结果表明,本文改进取得了预期结果。

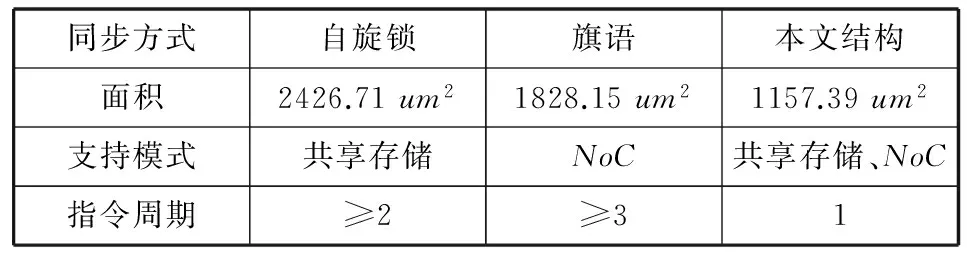

表5 同步单元性能对比

由表5可知,本文设计的同步单元硬件实现简单,占用硬件资源少,支持模式多,同步灵活,同步延迟短,同步效率高的特点。相比文献提出的同步单元,本设计显著地提升同步单元的性能,达到了预期的设计目标。

4 结 语

针对密码多核处理器中核间通信问题,本文深入研究了多核密码处理器的核间通信问题及同步机制。针对密码运算,本文改进了文献[7,8]中提出的适用于通用多核处理器的共享存储通信机制和核间信息传递通信机制,提出了簇间数据高速传输机制——DMA通信机制。和通用处理器中核间通信机制相比,在实现密码算法过程中,本文提出的结构效率更高、支持通信方式更灵活;与通用处理器中同步单元模块相比,本文提出的同步单元设计,硬件开销更小、同步效率更高,与存储结构的融合性更高。综合结果表明,该通信机制与同步单元能够灵活高效地实现核间通信需求,具有很好的应用前景。

[1] 谢子光.多核处理器核间通信技术研究[D].成都:电子科技大学,2009.

[2]JuX,QinY,YangL,etal.Overviewofinter-communicationmechanismonmulti-coreprocessor[C]//ComputerApplicationandSystemModeling(ICCASM),2010InternationalConferenceon.IEEE,2010,7:V7-187-V7-190.

[3]HowardJ,DigheS,HoskoteY,etal.A48-coreIA-32message-passingprocessorwithDVFSin45nmCMOS[C]//Solid-StateCircuitsConferenceDigestofTechnicalPapers(ISSCC),2010IEEEInternational.IEEE,2010:108-109.

[4]QuanH,XiaoR,YouK,etal.Asimplehigh-efficientinter-corecommunicationmechanismformulticoresystems[J].Pro.Asia-PacificSignalInf.Process.Association(APSIPA’11)ASC,2011 (338).

[5]SubramoniH,PetriniF,AgarwalV,etal.Intra-socketandinter-socketcommunicationinmulti-coresystems[J].ComputerArchitectureLetters,2010,9(1):13-16.

[6] 肖瑞瑾.多核处理器层次化存储体系研究[D].复旦大学,2012.

[7]YuZ,YouK,XiaoR,etal.An800MHz320mW16-coreprocessorwithmessage-passingandshared-memoryinter-corecommunicationmechanisms[C]//Solid-StateCircuitsConferenceDigestofTechnicalPapers(ISSCC),2012IEEEInternational.IEEE,2012:64-66.

[8]VangalSR,HowardJ,RuhlG,etal.An80-tilesub-100-wteraflopsprocessorin65-nmcmos[J].Solid-StateCircuits,IEEEJournalof,2008,43(1):29-41.

[9]HuW,WangR,ChenY,etal.Godson-3B:A1GHz40W8-core128GFlopsprocessorin65nmCMOS[C]//Solid-StateCircuitsConferenceDigestofTechnicalPapers(ISSCC),2011IEEEInternational.IEEE,2011:76-78.

[10]MaT,BosilcaG,BouteillerA,etal.Kernelassistedcollectiveintra-nodeMPIcommunicationamongmulti-coreandmany-coreCPUs[C]//ParallelProcessing(ICPP),2011InternationalConferenceon.IEEE,2011:532-541.

[11]WangMY,SuCP,HorngCL,etal.Single-andmulti-coreconfigurableAESarchitecturesforflexiblesecurity[J].VeryLargeScaleIntegration(VLSI)Systems,IEEETransactionson,2010,18(4):541-552.

DESIGNANDRESEARCHONMCP-ORIENTEDINTER-CORECOMMUNICATIONUNITFORMULTIPLECORES

ChenFanXuJinfuLiWei

(College of Cryptography Engineering,PLA Information Engineering University,Zhengzhou 450001,Henan,China)

Inordertosolvetheproblemofoptimisingimplementationinregardtomulti-taskcipherprocessing-orientedinter-corecommunicationmechanismformultiplecores,wedesignedamixedcommunicationmechanism.Basedonanalysingthemulti-coreprocessingarchitectureandthecharacteristicofinter-corecommunication,inthispaperwefirstproposetoconstructthemixedcommunicationmechanismbyintegratingthecommunicationmechanismofshared-memorywithinclustersandthemessagepassingmechanismamongclustersmeanwhileintroducingthedirectmemoryaccess(DMA)communicationmechanism,andthisfurtherimprovesthecommunicationefficiency.Secondly,wepresenttheoptimisingimplementationofinter-corecommunicationsynchronisationmechanismandthissolvestheproblemofconsistencyconflictinsynchronisationandstorage.Finally,weevaluatethedesignschemethroughexperimentbasedonDesignComplier.Experimentalresultsshowthattheschemehaslessresourcecostandhigherperformanceindicatorscomparedwithotherschemes,andachievessatisfiedcommunicationthroughputaswell.

Multi-corecipherprocessor(MCP)CipheroperationInter-corecommunicationSynchronisationmechanism

2014-10-24。陈帆,硕士生,主研领域:大规模集成电路设计。徐金甫,副教授。李伟,讲师。

TP309.7

ADOI:10.3969/j.issn.1000-386x.2016.03.076