应用于无线通信收发系统锁相环的研究*

2016-09-16陈海波张昆仑王林锋东南大学集成电路学院南京10096东南大学射频与光电集成电路研究所南京10096

陈海波,孟 桥,李 冬,张昆仑,王林锋(1.东南大学集成电路学院,南京10096;.东南大学射频与光电集成电路研究所,南京10096)

应用于无线通信收发系统锁相环的研究*

陈海波1,2,孟桥2*,李冬2,张昆仑1,2,王林锋2

(1.东南大学集成电路学院,南京210096;2.东南大学射频与光电集成电路研究所,南京210096)

无线通信收发系统需要锁定时间较短的锁相环,从而提高数据传输速率。主要对PFD和电荷泵模块进行研究,消除了PFD的盲区,引入的推入式电荷泵加快了锁相环的入锁。在此基础上设计了一种快速锁定电荷泵锁相环(CP-PLL),并采用TSMC 0.35μm CMOS工艺,Cadence Spectre/Virtuoso仿真工具对其进行验证。经测试,PLL能实现信号频率从203.4 MHz~286.6MHz范围内的锁定,锁定时间小于60个时钟周期,相位噪声-107.75 dBc/Hz@1MHz,功耗小于13.15mW。

无线通信收发系统;盲区;电荷泵锁相环;快速入锁;相位噪声

通信收发系统中的锁相环频率合成器,其锁定速度将直接影响到通信系统信道的切换速度,频率合成器的锁定时间正日益成为锁相环频率合成器最重要的指标之一[1]。PFD引入延时单元可以消除死区,不过其复位时间变长,导致在盲区时间内到来的时钟边沿不会响应而丢失[2]。而PFD的盲区对锁相环的锁定速度也有一定的影响[3]。为了降低锁定时间,文献[4-5]采用前馈补偿法,文献[6]采用分数分频法,文献[7-8]采用的方法是动态地调整带宽。前馈补偿法虽然加快锁定的效果最明显,但是实际操作中太复杂,很少被应用。分数分频法使得输入参考频率不受限于信道带宽,即可提高输入参考频率,增大带宽,缩短锁定时间,但电路结构较为复杂。动态调整带宽法在PLL环路达到锁定状态时,相位噪声和毛刺能被有效降低,同时系统锁定时间得到加快。

本文主要对锁相环的PFD和电荷泵两个电路模块进行研究,引入了一种新型动态PFD,消除了盲区和死区,加速了PLL的锁定。在动态调整带宽法基础上,引入了推入式电荷泵,同样加快了PLL锁定,减小了锁定时间。

1 电路设计

图1为传统的电荷泵锁相环结构框图,为了减小锁定时间,需要通过增大电荷泵电流来增大带宽,从而减小PLL锁定时间,不过这种方法增加了系统功耗和相位噪声,带宽过大PLL还可能失锁。

图1 传统的PLL结构框图

图2为本文设计的PLL结构框图,在传统电荷泵锁相环路中增加一个电荷泵回路,外加的电荷泵只在PLL锁定前工作,在PLL到达锁定前的某个设定时间时,CP2退出锁相环回路。这样可以大大减小电荷泵的锁定时间,同时,环路相位噪声和功耗也不会增加。

图2 本文PLL结构框图

1.1PFD

本文引入了一种新型PFD,可以消除盲区,加快PLL锁定,电路结构如图3所示。

图3 新型PFD

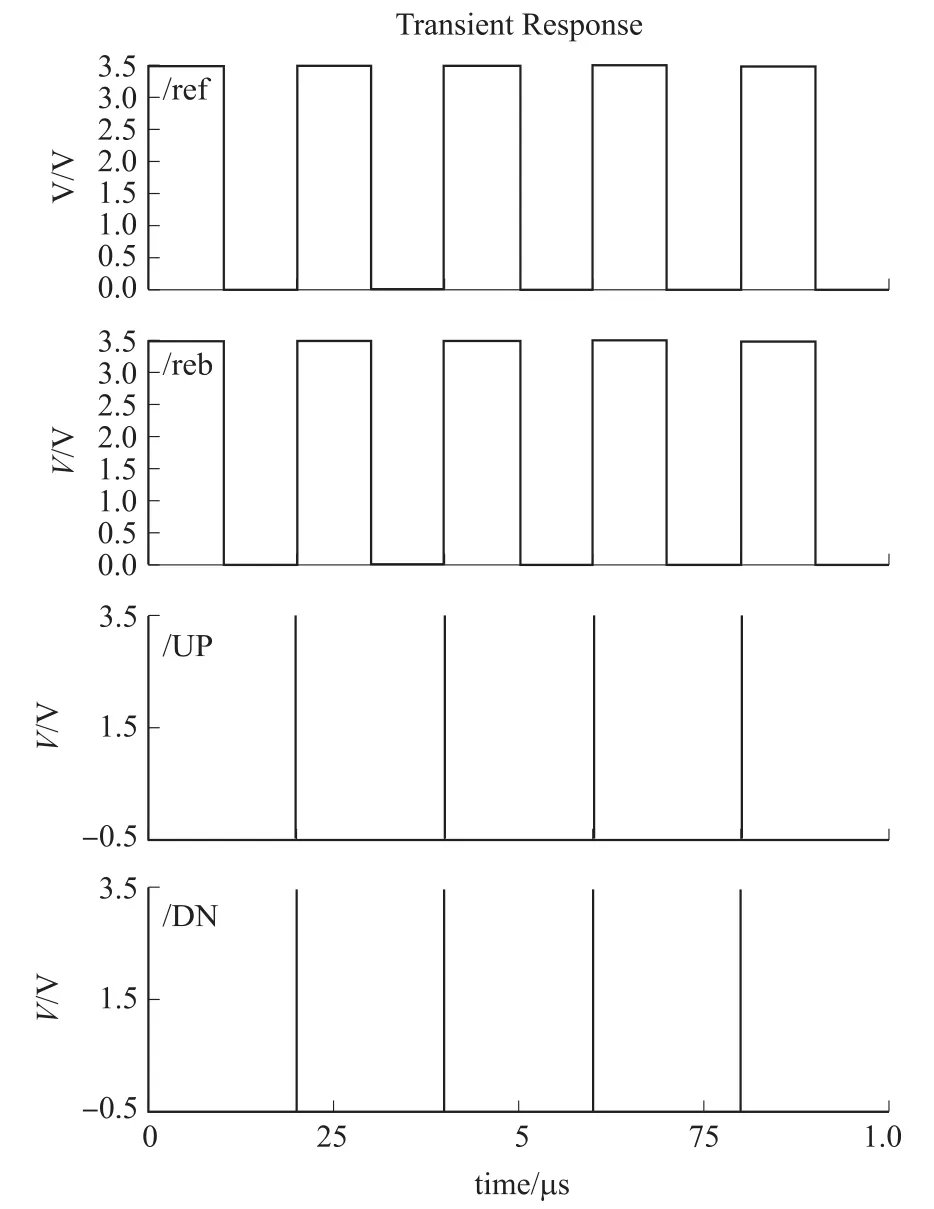

工作过程:起始时刻,REF=FEB=UP=DN=0,A= B=1,此时传输门T1和T2导通,E=F=0,C=D=1。若REF的上升沿先于FEB的上升沿,则M11导通,B点放电至低电平,UP=1。当FEB上升沿到来时,SW2= 0,T2关断,F保持低电平,DN=UP=1,PFD开始复位,M3和M9导通,M2和M8截止,C点和D点放电至低电平,M4和M10导通,A点和B点充电至高电平,UP= DN=0,经过与门,M2和M8导通,M3和M9截止,复位结束。当DN=UP=0时,G=1,T1导通,信号FEB传输至E,可见SW1和复位信号同时跳变。这样可以保证在复位过程中有FEB或上升沿到来的情况下,其高电平信号将在复位结束时传输至E点或F点,从而使得FEB信号和REF信号的上升沿没有丢失。

同时,在复位回路增加由反相器构成的延时单元消除了PFD的死区。当FEB信号和REF信号同频同相时,UP和DN仍有窄脉冲存在,FED输出情况如图4所示。那么即使当反馈信号和输入信号相位小于某一特定值Δθ时,UP和DN也有一定的脉冲宽度,使得电荷泵能够正常工作,从而消除传统PFD存在的盲区问题。

图4 PFD输出情况(fFEB=fREF,Δθ=0)

1.2电荷泵

本文设计了两个电荷泵,保持锁定电荷泵(CP1)和推入式电荷泵(CP2),其中CP1工作在未锁定状态和锁定状态,CP2只工作在未锁定状态。CP1在传统电路结构的基础上引入了两对电流镜,即图5中所示的M15、M16和M25、M26。以M15和M16电流镜为例,此电流镜可以迅速提高M13和M14的栅压,使得M13和M14断开,进而M12截止,电荷泵停止放电,从而实现开关的快速切换。

图6为增加电流镜M15和M16前后M13和M14栅压变化情况,相比之下,引入电流镜有利于MOS管栅电压的迅速提高。同样,引入电流镜M25、M26也有利于开关的快速切换,使得电荷泵快速停止充电。

图5 保持锁定电荷泵

图6 M 13和M 14管栅压变化

本文采用II型三阶锁相环,能够很好地抑制参考信号的噪声[12]。式(1)、式(2)中f1为PLL锁定时的频率容限,f2为输出频率跳变值,ωc表示环路带宽,可见当其它条件确定时,ωc和Ip成正比。若只用电荷泵CP1,则需要增大Ip来缩短锁定时间,但是环路带宽会变大,PLL可能会失锁。

图7 推入式电荷泵

这里引入推入式电荷泵,如图7所示。CP2只在PLL锁定前工作,电荷泵充放电电流为(ICP1+ ICP2),锁定后为ICP1,可见CP2的引入并没有改变PLL环路带宽。CP2由控制单元和充放电电路组成。控制单元中的D触发器用来比较延时单元的延时Δθ和PFD产生的相位差θe。以充电过程为例,当UP=1,M4和M5导通时,若Δθ<θe,D触发器输出Q=0,即M3导通,开启CP2的充电电路,锁相环的总充电电流增加,由于这个时候的电流是最大的,将最大程度地推进PLL入锁;若Δθ>θe,D触发器输出Q=1,M3关断,CP2停止工作。放电电路的工作过程与充电电路类似,在此不再赘述。

1.3环路滤波器

环路滤波器影响PLL系统的带宽和稳定性。由于一阶滤波器的输出纹波较大,会导致PLL输出信号发生较大抖动,因此本文采用结构相对简单的二阶无源滤波器。

1.4压控振荡器

图8为压控振荡器(VCO)框图,包括6个模块,分别为偏置,运放,复制偏置电路,延迟单元,整形电路和启动电路。其中整形电路的作用一方面提高了带负载能力,同时将正弦波信号转化成占空比为50%的方波信号,避免PLL输出信号的抖动;复制偏置电路与子延时单元结构完全相同,同时添加了一个放大器构成的负反馈系统,从而稳定VCO输出周期信号共模电压的变化。

图8 VCO框图

2 电路性能

测试芯片采用台积电公司提供的0.35μm单阱、多晶硅4层金属的CMOS工艺制作实现。图9为本文设计的CP-PLL芯片显微照片,芯片面积为0.44mm2。

图9 CP-PLL芯片显微照片

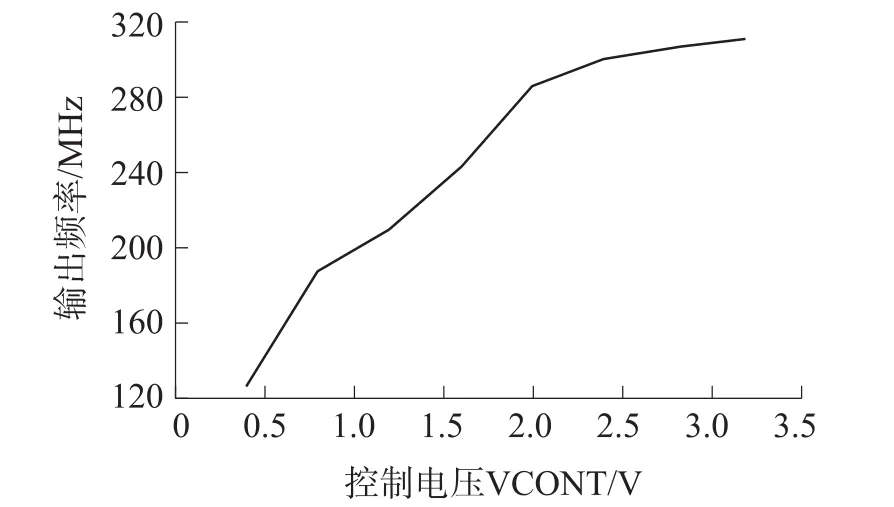

这里MPW的整个芯片共有6个子芯片,40个引脚,其中图示8个为PLL测试引脚。以下分别对PLL相位噪声,锁定时间,功耗以及VCO压频特性进行了测试。图10显示在1MHz处PLL相位噪声为-107.75 dBc/Hz。设置参考频率6 MHz~9 MHz,将PLL输出信号的频率和VCO输入端电压进行拟合,得到图11所示VCO压频曲线,VCO灵敏度为83.17 MHz/V。表明 PLL锁定信号频率范围在203.4MHz~286.6MHz之间,锁定时间小于60个时钟周期,系统的整体功耗为13.15mW。

图10 PLL相位噪声

表1将本文提出的快速锁定电荷泵锁相环和其它3种已发表的快速锁定锁相环进行性能对比。从表1可以看出虽然文献[9-10]提出的锁相环面积小,但是本文提出的锁相环具有更快的锁定速度。此外本文锁相环锁定时间与文献[8]接近,但面积小,同时消耗更低地功耗。

图11 VCO的压频特性

表1 性能比较

3 总结

本文在传统锁相环加快锁定的基础上进行了研究,优化了PLL的各个模块。新型的PFD结构消除了PLL在锁定过程中的盲区,减小了锁定时间;保持锁定电荷泵引入两对电流镜,实现了开关的快速切换;基于动态带宽调整的方法,在PLL环路中增加了推入式电荷泵,该电荷泵只在锁定前工作,在不增加系统相位噪声和功耗的前提下,加快了PLL入锁。对于PLL的核心模块压控振荡器也做了较为细致地设计,其灵敏度和调频范围都满足设计需要。测试结果表明,本文设计的锁相环能够实现输出频率从203.4MHz~286.6MHz范围内变化的锁定,并且能够快速入锁。本文设计的快速锁定锁相环可应用于中高速传感网无线通信收发系统中,从而提高通信系统信道的快速切换。

[1] 邝小飞.快速锁定射频锁相环频率合成器研究[D].北京:中国科学院半导体研究所,2006.

[2] Kun Seok Lee,Byeong Ha Park,Han il Lee,etal.Phase Frequency Detectors for Fast Frequency Acquisition in Zero-Dead-Zone CP-PLLs forMobileCommunication Systems[C]//Proc 29th Europ-SolStaCircConfEstoril,Portugal.2003:525-528.

[3] 但慧明,柴旭朝,于宗光,等.一种用于锁相环快速锁定的动态鉴频鉴相器[J].微电子学,2010,40(5):653-656.

[4] Zhang BY,Allen PE.Feed-Forward CompensatedHigh Switching Speed Digital Phase-Locked Loops[M].Proceedings ISCAS,Jun.1999(4):371-374.

[5] Sidiropoulos S,Liu D,Kim J,etal.Adaptive Bandwidth DLLs and PLLs Using Regulated Supply CMOS Buffers[J].Symp on VLSI CircuitsDigest Technical Papers,Honolulu,HI,2000:124-127.

[6] Hsieh P H,Maxey J,Yang C K K.A Phase-Selecting Digital Phase-Locked Loop with Bandwidth Tracking in 65-Nm CMOS Technology[J].IEEE Journal of Solid-State Circuits,2010,45 (4):781-792.

[7] 方立军,马骏,王元庆.现代频率合成中的分数分频与锁相环[J].现代雷达,2002,24(3):68-72.

[8] 黄水龙,王志华.快速建立时间的自适应锁相环[J].电子与信息学报,2007,29(6):1492-1495.

[9] Chung Chingche,Lee Chenyi.An All-Digital Phase-Locked Loop for High-Speed Clock Generation[J].IEEE Journal of Solid-State Circuits,2003,38(2):347-351.

[10]杨枫.CMOS快速锁定电荷泵锁相环的研究与设计[D].华中科技大学,2009.

[11]Chen Paolung,Chung Chingche,Yang Jyhneng.A Clock Generator with Cascaded Dynamic Frequency Counting Loops for Wide Multiplication Range Application[J].IEEE Journal of Solid-State Circuits,2006,41(6):1275-1285.

[12]李仲秋,胡锦,陈迪平.三阶电荷泵锁相环的稳定性分析[J].电子器件,2006,29(2):483-485.

陈海波(1988-),男,汉族,江苏宿迁人,现就读于东南大学射频与光电集成路研究所,硕士研究生,主要从事超高速数模混合集成电路方面的研究,chb_seu@126.com;

孟桥(1965-),男,博士,教授,博士生导师,主要从事超高速信号处理及IC设计,人工神经网络IC实现技术研究,超高速ADC设计,深空探测及射电天文接收与信号处理,mengqiao@seu.edu.cn。

Research of PLL App lied in theW ireless Comm unication Transceiver System*

CHEN Haibo1,2,MEN GQiao2*,LI Dong2,ZHANG Kunlun1,2,WANG Linfeng2

(1.School of Integrated Circuits,Southeast Uniυersity,Nanjing 210096,China;2.RF and Optical Institute,Southeast Uniυersity,Nanjing 210096,China)

PLL applied in thewireless transceiver system needs lower locked time in order to improve data transfer. The PFD(Phase Frequency Detector)and CPof the PLLweremainly researched.The blind area ofPFDwaseliminated and the push-CPwasdrawn into to speed up the PLL.On thebasisof the two circuits,a fast locking CP-PLLwasdesigned.Based on the process of TSMC 0.35μm CMOS,the performance of PLL was verified by the tool of Cadence Spectre/Virtuoso.Itwas tested thatthe locked timewas60 clock cycles,thephasenoisewas-107.75 dBc/Hzat1MHz,the power consumption was less than 13.15mW and the PLL could be fast locked when the signal frequency ranged from 203.4MHz to286.6MHz.

wireless communication transceiver system;blind area;CP-PLL;quick locked;phase noise

TN911.8

A

1005-9490(2016)04-0874-05

项目来源:中央高校基本科研业务费专项项目(3227005710);江苏省普通高校研究生科研创新计划项目(3227005710);江苏高校品牌专业建设工程项目

2015-08-12修改日期:2015-09-10

EEACC:129010.3969/j.issn.1005-9490.2016.04.024