脉冲电容试验装置控制系统电磁兼容设计

2016-09-12李小亮董雪峰

李小亮,董雪峰

(黄河科技学院 信息工程学院,河南 郑州 450063)

脉冲电容试验装置控制系统电磁兼容设计

李小亮,董雪峰

(黄河科技学院 信息工程学院,河南 郑州 450063)

在脉冲电容试验装置研制工程中,电磁兼容是必须考虑的因素。设计中通过采用电磁滤波、信号隔离、去噪、阀值调节电路等措施,并根据FPGA特性,从芯片的内部和外部设计两方面提高了整个控制系统的抗干扰能力,实现了电磁兼容设计,确保了试验平台的安全、可靠和稳定工作。

脉冲电容FPGA;电磁兼容;抗干扰

电磁兼容性是指一般电气、电子设备在共同的电磁环境中能执行各自功能的并存状态,既要求都能正常工作又要求互不干扰,达到“兼容”的状态,任何电子电子设备或电子系统的设计都应包括电磁兼容设计。

脉冲电容试验装置主要完成质量试验和耐压试验[1]。控制系统工作环境恶劣、电路复杂,主要包括电源电路、信号处理电路、控制电路、接口电路、显示电路等模数混合电路等。为提高控制系统的可靠性,必须采取必要的措施来抑制电磁干扰及优化电路硬件和软件设计,保证系统稳定工作。

1 电磁干扰成因

电磁干扰的形成必须同时具备3个要素:即电磁干扰源、传输路径及敏感设备。干扰源是指产生的干扰的元件、设备或信号;传播路径指干扰从干扰源传播到敏感器件的通路或媒介;敏感设备是指容易被干扰的对象,如微处理器、A/D转换器、D/A转换器、比较器等。

1.1 电网干扰及系统放电干扰

脉冲电容试验控制系统中采用市电供电,电网质量直接影响系统工作的稳定性。试验中设备的启停造成交流电源电压的短1时跌落,以及继电器和试验控制系统中开关柜的动作引起的快速脉冲群等都会影响到电源电压的稳定性,从而对控制系统造成干扰;另外,试验系统主要包括质量试验和耐压实验,质量实验要求对 0.33 μF脉冲电容恒流充电至8 000 V,放电电流达到8 000 A,测试频率为6~8次/1 min,进行连续测量;耐压实验要求脉冲电容充电至12 000 V,保持1 min后,进行短路放电,放电电流接近12 000 A[1]。因此,试验过程中接近短路放电会产生上千伏的浪涌电压及伴随火花干扰。

1.2 传输路径

电磁干扰传输路径有两种方式:一种是传导传输方式;另一种是辐射传输方式。对于脉冲电容试验系统,主要包括短路放电构成的磁场耦合干扰及经过传导线对控制电路形成的干扰。

1.3 敏感设备

试验控制系统主要以FPGA为核心,实现对高压电源、AD采样控制器、开关柜、峰值检波电路、罗氏线圈及各接口、显示电路的控制。芯片采用CYCLONEⅡ系列的EP2C5T144,其电源模块采用5 V供电,I/O端口供电电压为3.3 V,而内核供电仅为1.2 V,因此电源电压的起伏、噪声的引入都可能会使得FPGA配置信息出错而导致系统失效,产生严重后果[2]。另外,控制系统中A/D转换器引入的共模干扰信号、电容短路放电时峰值采样引入的噪声信号同样会引起FPGA产生误判,影响系统的稳定性。

2 采用的抗干扰措施

我们一般采取的抗干扰基本原则是:抑制干扰源、切断干扰传播路径,提高敏感器件的抗干扰性能。

2.1 电源滤波

试验装置的频繁启停、短路放电产的上千伏浪涌电压会严重影响电网质量,从而影响控制系统的可靠性,因此需在电网输入端采用变压比为1:1的隔离变压器,降低电源杂讯干扰及提高电源信噪比。

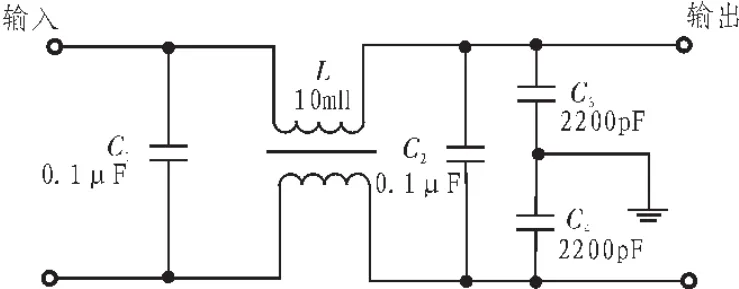

1)电磁干扰属于射频干扰,其传导噪声频谱大致为10 k~30 MHz,从形成特点分析分为串摸干扰和共模干扰。电源设计中,220 V交流电首先经过图1电磁干扰滤波电路后再经DC/DC转换为控制电路提供稳定的直流电源。

图1 电磁干扰滤波电路Fig.1 Circuit of EMI filter

L为共模扼流圈,将两个线圈分别绕在低损耗、高导磁率的铁氧体磁环上,当出现共模干扰时,由于两个线圈磁通方向相同,经过耦合总电感量迅速增大,因此对共模信号呈现很大的感抗,图1中L的电感量与EMI滤波电路的额定电流关系如表1所示。C1、C2为差模抑制抑制电容,主要用来滤除串膜干扰;C3、C4为共模抑制电容,跨接在输出端,中间接地,可有效抑制共模干扰信号[3]。

表1 电磁滤波电路电感量与电流关系表Tab.1 Diagram of relationship of inductance and current to EMI circuit

2)在控制电路电源端并联一个10 μF/50 V钽电容和一个0.1 μF的高频、地分布电感陶瓷电容进行电源退耦,同时在每个芯片电源端口和信号输入端口并联一个瞬态抑制二极管,可吸收高达数千瓦的浪涌功率,使两级间电压嵌位于设定值,有效保护控制电路免受浪涌电压和电磁干扰。

2.2 罗氏线圈的抗干扰设计

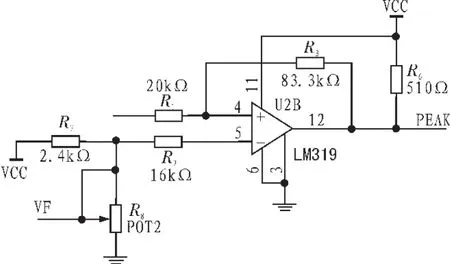

质量试验中,为满足参数设计要求,需使用具有响应速度快、频带宽、灵敏度高、测量范围大、抗电磁干扰能力强等特点的电流传感器进行电流采样。为此,我们特意设计了小型大电流罗氏线圈[4]。线圈制作过程中,很难保证积分阻和线圈的波阻抗匹配,所以在线圈中传播的电磁波通过积分电阻必然产生反射,反射时间为电磁波的渡越时间Td的两倍。反射会造成输出信号的振荡,周期为:

其中C为光速,N为线圈匝数,b为骨架外经,l为线圈等效周长。应要求2Td小于被测信号上升时间。另外,感应线圈工作时相当于信号源,产生的电压信号经电缆输入示波器,它的负载就是积分电阻与同轴电缆,在阻抗不匹配情况下会造成波的反射,而产生一个欠阻尼振荡。因此,设计时,使α= 0.5R<<Zr。

2.3 峰值检波消噪电路设计

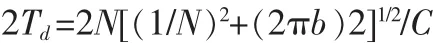

峰值检波电路中,罗氏线圈将放电电流转换成电压信号和8 000 A对应的阀值电压比较,判断放电电流达到8 000 A。而感应到的模拟信号中夹杂的噪声和干扰易使比较器在阀值附近出现重复翻转,造成系统不稳定,因此,电路中采用迟滞比较器设计大大提高了电路的抗干扰能力。图2中,峰值检波电路LF398的输出经电阻R1加到具有低输入失调电压和偏置电流、高电压增益、共模抑制好并具有输入保护二极管的高速比较器LM319同相输入端,和反馈电压一起构成比较器的外部滞回电压,在VF端可根据需要调节阀值电压值。

图2 阀值电压调节电路Fig.2 Circuit of threshold voltage regulation

2.4 FPGA内部设计中的抗干扰措施

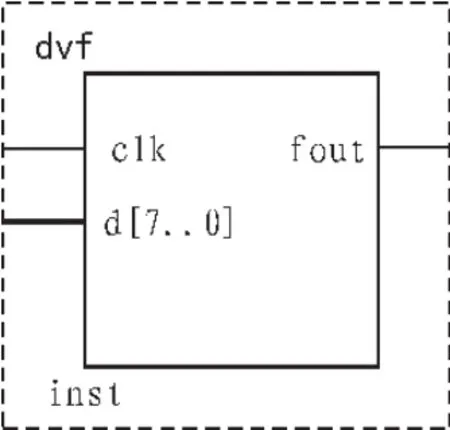

1)在FPGA的控制系统设计中,电容的短路放电、手动控制按钮的启动、停止,在瞬间都会产生电压的突跳,使得输入信号中存在噪声,从而导致系统的误动作。为避免尖峰干扰信号及机械开关电压抖动,采用计数器作为数字滤波电路。方法是将输入信号加到计数器输入端,当开关启动或者输入信号为高电平时,对采样脉冲开始计数,只有在采样时间内连续计数到达足够次数时认为信号有效,否则视为无效。针对不同的输入信号和尖峰干扰,可以设置不同的采样时间,如图3所示,通过设置合适的预置数D,即可滤除机械开关中的电压波动和消除不稳定的干扰信号。

图3 可预置数数字滤波电路Fig.3 Digital filter circuit of preset data

2)由于信号在FPGA内部经过不同的连线和逻辑单元时产生的延时不同,同时信号的高低电平转换也需要一定的过渡时间,因此当芯片内部多路信号同时变化时会出现毛刺信号[5]。而这些毛刺信号可能直接作用到控制电路的时钟输入端、清零端、置位端及质量试验计数端口,导致系统出错,为避免毛刺信号产生及减小其对控制电路的影响,可利用D触发器锁存法、冗余项消除法、采样法、吸收法[6]、VHDL语言描述法、单进程Moore状态机等方法消除毛刺信号。

图4 改进前电流放电波形Fig.4 Waveform of discharge current before improving circuit

图5 改进后电流放电波形Fig.5 Waveform of discharge current after improving circuit

3 结 论

电磁兼容设计是保证是保证试验系统安全、稳定工作的重要因素。参照实际的电磁环境,采用了隔离、滤波、退耦、建立迟滞回路和FPGA内部滤波电路等多种方式,并经过多次测试和改进,实现了试验系统的长期稳定可靠工作,图4和图5分别为改进前后脉冲电容放电波形,比照其结果,从图中可明显看到改进后放电电流更大(放电电流变比为1000A: 1V),且波形更为平滑。

[1]李小亮,董雪峰.脉冲电容器质量试验及其电路中元件参数的确定[J].电子设计工程,2011(3):172-175.

[2]张惠国,王晓玲,唐玉兰,等.一种用于FPGA配置的抗干扰维持电路[J].电子学报,2011(5):1169-1173.

[3]李鹏,何文忠.开关电源电磁干扰滤波器设计[J].激光与红外,2007(1):79-81.

[4]卫兵,卿燕玲,关永超,等.测量低频大电流的自积分罗氏线圈设计[J].强激光与粒子束,2010(9):2227-2231.

[5]李涛,高杨英,韩力.FPGA在恶劣电磁环境下的抗干扰设计[J].电子工程师,2004(6):38-40.

[6]马利,马技,牛斌.基于FPGA的光电编码器电路抗干扰设计[J].辽宁大学学报:自然科学版,2010(3):244-247.

EMC design of control system of test device of impulse capacitor

LI Xiao-liang,DONG Xue-feng

(Huanghe Science&Techonology College,Zhengzhou 450063,China)

EMC is a necessary factor to be considered in the design&development phase of the test device of impulse capacitor.By using the electromagnetic design of filter,signal isolation,denoising,a threshold adjustment circuit,and according to the characteristics of FPGA,from the internal and external of FPGA chip to improve the anti-interference ability of the whole control system,we realizes the electromagnetic compatibility design,and ensure that the platform is stable and reliable work.

impulse capacitor;FPGA;EMC;anti-interference

TN97

A

1674-6236(2016)04-0134-03

2015-04-16 稿件编号:201504168

郑州市光电信息技术及应用重点实验室项目(114PYFZX505)。

李小亮(1983—),男,河南济源人,硕士,讲师。研究方向:电子通信系统。