基于SERDES的同步光纤环网设计与实现

2016-07-04赵晓宇江可扬

赵晓宇,江可扬

(武汉船用电力装置研究所,武汉 430064)

基于SERDES的同步光纤环网设计与实现

赵晓宇,江可扬

(武汉船用电力装置研究所,武汉 430064)

摘要:本文介绍了一种基于SERDES的同步光纤环网的设计以及实现方法,其实现方法简单,同步效果好。通过采用FPGA中的SERDES收发器可使得信息传输速度达到1.25 Gbps,并通过链路协议有效的控制了信息在每个节点的传输延时,使得网络传输周期大大的减小,从而实现对高频率控制的支持。本文的通信协议还实现了信号采集的同步,从而提高控制精度。最终通过在硬件系统上的实验,验证了设计的正确性和可靠性。

关键字:SERDEFPGA实现同步光纤环网信号同步采集实时通信Verilog编程

0 引言

近年来随着经济的发展,电力的应用领域越来越广泛,对电力变换的需求也大幅提高,对大功率变换器的需求也越来越高。由于受限于器件的功率水平,目前大功率变换器大多采用功率模块级联或变流器并联的方式实现,而这都对控制器造成更多的外部接口要求、更大的数据传输量、更快的运算能力等。

为解决复杂系统所面临的这些问题,美国海军部于1995年提出了PEBB标准电力电子模块的概念,以求能够对这些问题提供一种解决方案。这种设计思想自其提出便受到了广泛的关注,许多科研机构开始对大功率电力电子系统的分布式控制、模块化设计以及相关通信方案进行了大量的研究,并提供了一些解决方案[5]。光纤环网便是其中一种可靠的解决方案。

由于环形结构每通过一个节点都会造成延时,且会随着节点数增加而逐渐积累,所以要采用环形拓扑就必须解决环形通信的同步性问题。目前在工业以太网中,基本都采用1588协议来实现各个节点的同步,但1588协议实现复杂,编程难度很大。在众多的工业以太网解决方案中比较有特点的是EtherCAT,其所采用的FMMU技术使得串行数据以数据列车的形式在环网中传输[4],在各节点实现边收边发,同时将要上传的数据装入数据列车中。因此大大的减少了传输延时,实现了较高的同步精度,但其技术细节并未对外披露。

目前国内也在这方面有了一定的研究如文献[2]和[3]所提出的软件可控的环形高速光纤网络拓扑的控制结构,以及论文[1]所提出的智能的改进的FDDI标准的通讯网络拓扑。

本文光纤环网中存在的节点延时、节点间同步、节点间采样同步、传输协议等问题进行了进一步的研究。提出了一种简单的基于SERDES的同步光纤环网实现方法提高了通信速率、降低了节点延时,并得到了更好的同步性能。并通过实验验证了其正确性。

1 SERDES协议原理

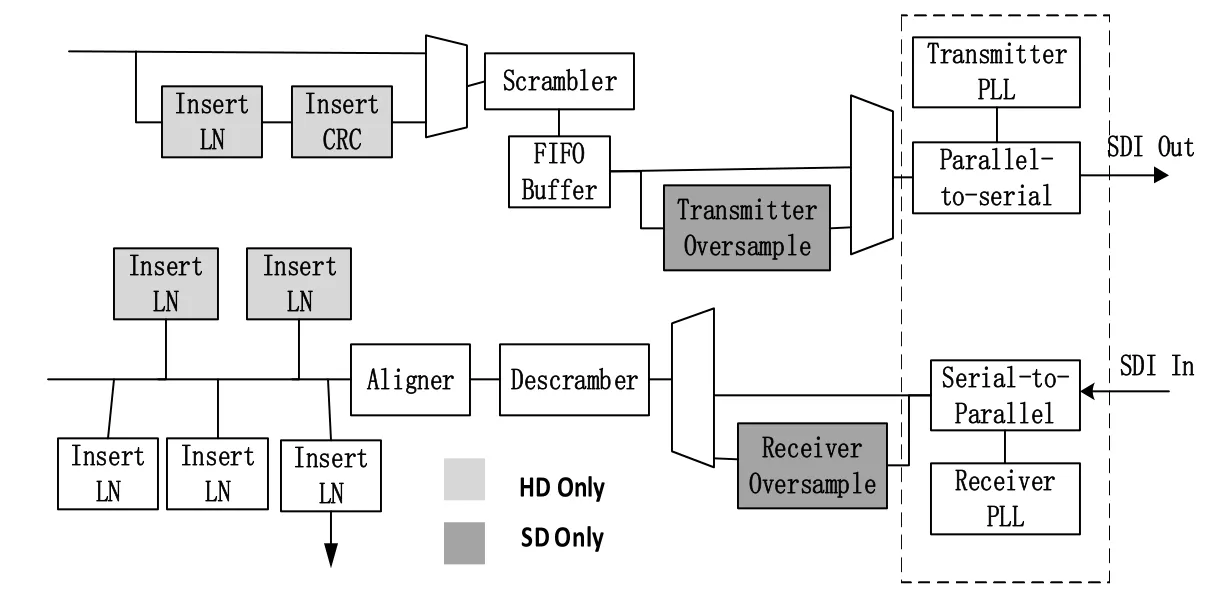

SREDES是SERializer和DESerializer的英文缩写,即串行收发器。它主要有接收单元和发送单元两部分组成,能够支持数G甚至几十G的传输速率,具体根据不同的器件而不同,且不同器件的实现机理也不尽相同。本文就以Altra的Stratix GX芯片内部收发器为例进行分析。其收发器结构如图1所述。

收发器发送部分主要是将要发送的并行数据转化为串行数据并对外发送。为保证数据能够在接收端正确的恢复,在发送端还对数据进行了一定的处理如:加入校验信息、进行8B10B编码、设置FIFO缓冲器等。

收发器的接收部分负责将发送来的串行数据进行恢复,并将串行数据转换为并行数据。接收端要实现数据的正确解析是有难度的,由于数据在高速传输时会产生严重偏移和抖动,在接收端很难进行捕捉和识别,特别对于这种跨时钟域的异步传输。所以在SERDES的接收端有特殊的机制来保证数据的可靠恢复。

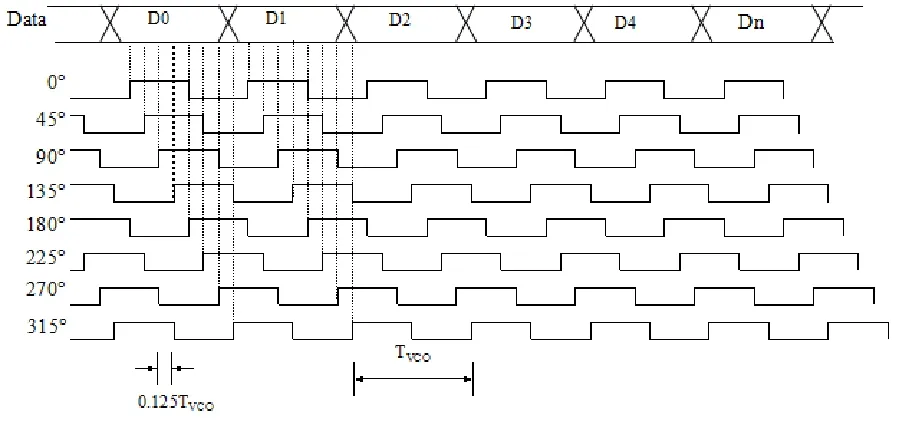

其数据恢复原理如图2和图3所示。

图1 SERDES收发器原理图

图2 数据恢复时钟产生电路

接收端的PLL通过如图2所示的电路产生依次相差45°的8个时钟,然后分别用这些时钟对输入的串行数据进行采样,根据采样结果从8个时钟中选取最优采样时钟,然后依据这个最优时钟进行串行数据的恢复。

2 同步光纤环形实现原理

同步光纤环网中节点间的同步是整个拓扑结构的关键,本节就从数据同步和采样同步两个方面对其原理进行研究。

图3 最优时钟选择原理

2.1节点间同步原理

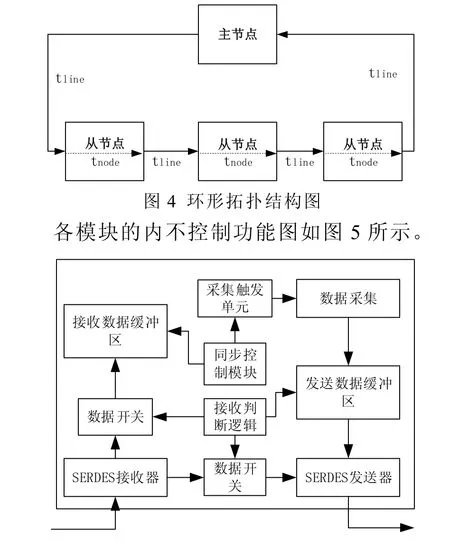

主节点将数据和指令封装后,向下传输依次通过各个节点,各个节点取下自己对应的数据并将状态数据插入到帧的尾部,最后返回主节点,主节点根据返回的状态来判断各个节点是否正确接收到了数据。本文采用的环形拓扑结构如图4所示。

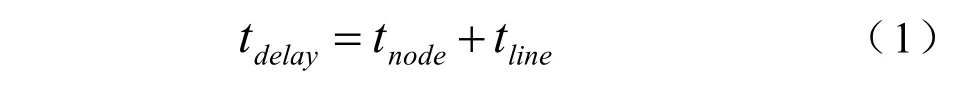

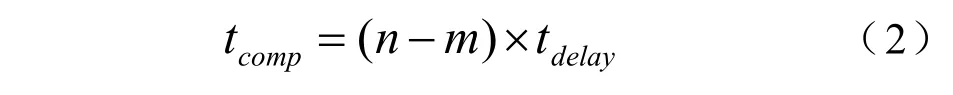

在数据传输环节延时主要由节点延时tnode和传输线延时tline,其中tnode为固定延时与传输协议和器件有关;tline为可变延时与光纤长度相关,一般为3~5 ns/m。本文中忽略tline造成的影响,以等长应用为背景进行分析。所以单个节点造成的延时tdelay可表示为:

所以对于有n个节点的系统,第m个节点所需补偿的延时tcomp为:

补偿延时由同步控制模块来实现。

图5 节点内部传输控制功能图

2.2数据同步过程

数据流向控制:接收端收到数据首先解析帧头来定位自己的数据段,并根据数据校验结果修改帧头。接收判断逻辑用于控制数据流向,若为本单元的数据则将其存储至数据同步模块,若不是则向下转发,若为上传字节段则将发送数据缓冲区的数据接至发送端。

同步控制:当接收数据缓冲区完成接收后,便启动同步控制模块工作,同步控制模块根据公式(2)的延时后触发数据更新,并同时启动采样,从而实现数据传输和采样的同步。

3 光纤环网同步协议实现

本文中光纤环网的同步控制采用FPGA芯片来实现,收发器采用FPGA内部标准的SEDRES内核来实现,其它控制协议采用Verilog语言编程实现。

协议实现过程为,主节点开机发送初始化帧,确定各节点位置,同时各节点上传各自的ID信息供主节点识别设备。接着主节点发送延时测量帧和延时设定帧,完成各节点的同步设定工作。接着进入工作状态发送正常的工作帧。其协议格式如图6所示,虚线部分为各节点插入数据。

协议帧配合图5所示的各功能单元来实现节点延时测量、节点延时控制、上传数据的插入队列、节点数据接收、非节点数据的转发等控制,最终实现环形内各节点数据接收和采样的同步。

图6 协议帧格式

4 仿真及试验结果分析

试验硬件平台如图7所示,包括一个主节点和两个从节点。

图7 光纤环网硬件测试平台

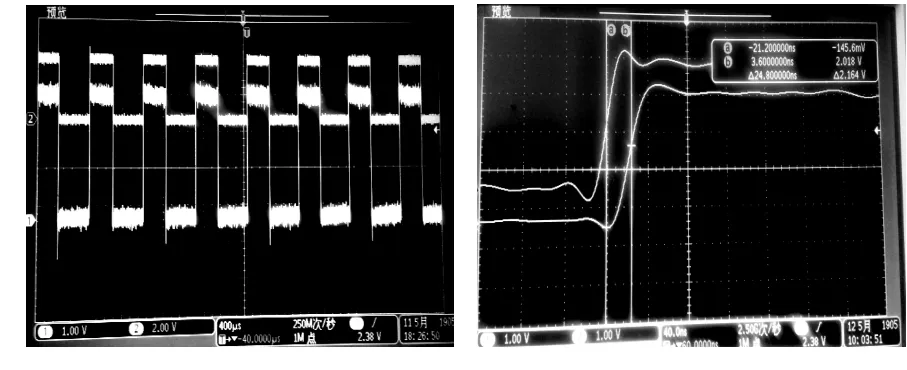

图8是节点间同步性测试波形,当从节点完成一次接收后便控制FPGA的IO引脚翻转波形,从而输出一个方波,从实验中可看出其同步精度达到25 ns。

图8 节点同步性测试

从试验结果可以看出,节点间达到了很高的同步性,从而验证了原理的可行性和正确性。对于实际应用有较强的指导意义。

参考文献:

[1]杭丽君,胡海兵,吕征宇,等.基于电力电子标准模

块的高速智能通讯网络拓扑[J].中国电机工程学报,2006,26(20):50-56.

[2]孙驰,张成,艾胜.一种实用的大容量电力电子系统高速光纤环网拓扑及其协议[J].中国电机工程学报,2012,(15):63-73.

[3]张成.大容量电力电子分布式控制系统关键技术研究[D].华中科技大学,2014.

[4]Orfanus D,Indergaard R,Prytz G,et al.EtherCAT-based platform for distributed control in high-performance industrial applications[C]//Emerging Technologies & Factory Automation (ETFA),2013 IEEE 18th Conference on.IEEE,2013:1-8.

[5]钱照明,张军明,谢小高,等.电力电子系统集成研究进展与现状[J].电工技术学报,2006,21(3):1-14.

Design and Realization of SERDES-based Synchronous Ring Fiber Net

Zhao Xiaoyu,Jiang Keyang

(Wuhan Institute of Marine Electric Propulsion,Wuhan 430064,China)

Abstract:This paper introduces a design and realization method for synchronous ring fiber net with SERDES,which very easy to realize and can reach very high synchronization.By using the SERDES core in FPGA,the communication speed can reach as fast as 1.25Gbps,and the delay caused by each node in the ring can be significantly reduced by link protocol,which make the cycle time very short and can support high speed control.Also the paper brings up a synchronous signal acquisition method,which is very helpful in improving control accuracy.Finally,it gives the test results on hardware platform,which verify the correction and reliability of the design.

Keywords:SERDES; FPGA implementation; synchronous ring fiber net; synchronous signal acquisition; Real-time communication; Verilog programming

中图分类号:TP791

文献标识码:A

文章编号:1003-4862(2016)06-0006-03

收稿日期:2015-12-23

作者简介:赵晓宇(1987-),男,工程师。研究方向:电力电子与电力传动。