基于FPGA的多相结构波形合成器

2016-07-04王志红

袁 彭,王志红

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室,陕西 西安 710071)

基于FPGA的多相结构波形合成器

袁彭,王志红

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室,陕西 西安 710071)

摘要针对FPGA在做普通DDS波形合成时带宽会受到工作时钟限制的问题,介绍了可以合成高速率、大带宽的多相结构波形合成方法。给出了该方法的工作原理和具体实现方式。通过仿真分析证明,该波形合成方法能够合成频谱质量较好的正弦波形和调频波。

关键词多相结构波形合成;信号模拟器;大带宽

在工程测试及实验中,经常需要使用一个信号模拟器来激励一个系统,以便完成对系统的调试[1]。由于通用的信号发生器难以满足一些特定系统的测试要求,这就需要设计专用的信号模拟器。而常用的DDS波形合成方法受FPGA工作时钟的限制,模拟出信号的带宽难以达到理想的期望值[1]。

本文所描述的多相结构波形合成方法在DDS方法的基础上对相位计算和相位波形转换两方面进行改进,能输出常规波形和调频波形[2]等多种模式的信号,可使输出信号及其采样频率达到一个新的高度。

1多相结构波形合成原理

多相结构波形合成系统总原理图如图1所示,每个通道的输出(K表示通道序号)均由8路合成。除第0通道结构略有不同,其他通道的原理结构均一致。下面将对多相结构波形合成的工作原理进行详细介绍。

1.1相位计算

第k通道第n路信号Sk,n(t)的表达式为

k=0,1,2,3;n=0,…,7

(1)

式(1)中,ω0是输出波形的初始角速度;t是时间;n表示每通道中路数的序号;μ表示调频斜率;TS是采样周期;τk表示第k通道与第0通道的时间差。

第k通道第n路信号的相位φk,n(t)可作如下变换

φk,n(t)=ω0(t+τk+nTs)+1/2μ[t2+2t(τk+nTs)+

(τk+nTs)2]=

ω0(t+τk+nTs)+1/2μt[t+2(τk+nTs)]+

1/2μ(τk+nTs)2=

(ω0+1/2μt)t+tμ(τk+nTs)+ω0(τk+nTs)+

1/2μ(τk+nTs)2

(2)

令φ0.0(t)=(ω0+1/2μt)、P1.k.n=μ(τk+nTs)、P2.k.n=ω0(τk+nTs)+1/2μ(τk+nTs)2,则式(2)可化为

φk.n(t)=φ0.0(t)+tP1.k.n+P2.k.n=φ0.0(t)+Δφk.n(t)

(3)

其中,φ0.0(t)为基准相位,当信号属性参数固定时;P1.k.n和P2.k.n也为定值,因此也可以作为参数输入。其他路的波形输出均可以看作在基准相位的基础上增加一个增量Δφk.n(t)得到。

图1 多相合成器原理图

1.2相位波形转换

sin(φA+φB)cosφc+(cosφAcosφB-sinφAsinφBsinφc)≈

sin(φA+φB)+(cosφAsinφc-sinφAφBsinφc)=

sin(φA+φB)+(cosφAsinφc+sinφAcosφc-

sinφAcosφc-sinφAsinφBsinφc)≈

sin(φA+φB)+sin(φA+φc)-sinφA

(4)

根据式(4)分析,将1/4周期波形分为26个[φA,φA+π/2·2-6)区间,每个区间又分为25段,相同区间中每个分段的幅值上升速度可以认为近似相等。P0点为P所在分段的起始点,其幅值为sin(φA+φB),sin(φA+φC)-sinφA表示所在区间第一段中,相位差为φC的两点之间的幅值差[4]。

令yp0=sin(φA+φB),Δypp0=sin(φA+φC)-sinφA,则P点的幅值可近似为P0的幅值yp,可简化为

yp=yp0+Δypp0

(5)

2硬件实现

本方案已经在FPGA中实现,所使用的芯片型号为Xilinx的XC5VLX30。总体实现模块的框图如图1所示,相位产生器负责根据相应的参数,计算出相位;相位波形转换器则负责根据相位通过ROM查找出对应的幅值;波形混合器负责将波形幅值进行整合输出。以下是对每个模块的介绍。

2.1相位计算的实现

由式(2)可知,第0通道第0路的相位为φ0.0(t),其他通道其他路的相位都可以在基础相位上增加Δφk.n(t)的量求得。因此,在实现相位计算时,可以先计算出一个基相位,然后通过累加得到其他路的相位。

根据式(2),计算基相位需要2个乘法器和1个加法器,比较容易实现。但在计算增量Δφk.n(t)+tP1.k.n+P2.n.n时,每路需要1个乘法器和1个加法器。由于每路有8路,所以多路就需要数量较多的Δφk.n(t)增量,因而需要很多乘法器和加法器,消耗很多片内资源[4]。Xilinx Vritex-5芯片中提供的DSP48E slices资源具有不再消耗其他资源及计算速度快的优点,而且每个DSP48E slices中包含2个25×18的乘法器和1个48位的加法器[5],满足增量计算的位宽要求,因此在实现过程中采用DSP48E slices资源完成计算。

FPGA内部的相位计算结构如图2所示,在基准相位的基础上加一个增量[6],就可以得到其他路的相位。为保证计算出的相位数据的时序对齐,需要对中间的计算结果进行适当的延迟。

图2 相位计算结构图

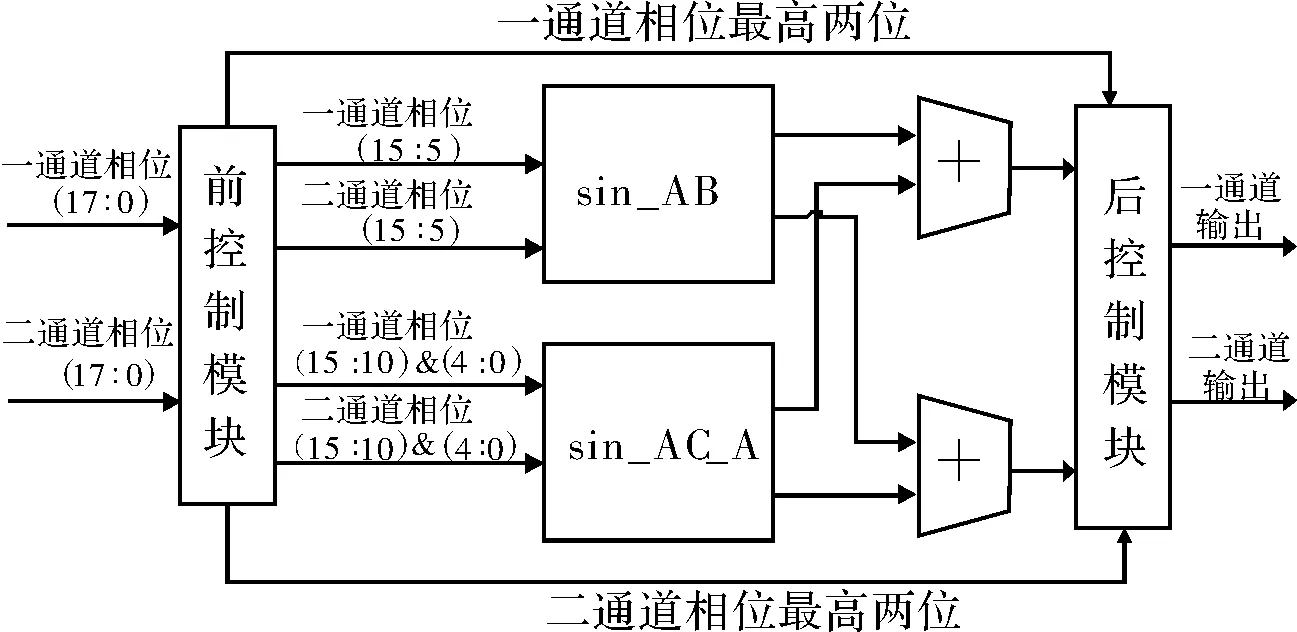

2.2相位波形转换的实现

如上节所述,相位波形转换主要应用的是查找表的方式,将计算出的相位映射成相应的波形幅度值输出[6],具体实现方式如图4所示。由图3可以看出:FPGA内部采用两种双口ROM进行查找,因此每个模块可以进行两路信号的相位波形转换,节省了一定的资源。对应上述内容,Sin_AB为主ROM,存放1/4周期(0°~90°)的yp0;sin_AB_C为校正ROM,存放相邻两个Sin_AB值之间的修正增量Δypp0。查找地址的位宽为18 bit,将其中的低16 bit送入ROM查询1/4周期数据。再对最高两位进行合理的逻辑运算,就可以从1/4周期的数据中得到整个周期的波形幅值数据。

根据式(5),因为yp0=sin(φA+φB),所以yp0为查找地址的第15位到第5位对应的幅值;而Δypp0=sin(φA+φC)-sinφA,所以Δypp0对应查找地址的第15位~第10位和第4位~第0位,具体如图4所示。

这种查找方式,在节省查资源的基础上,保证了更高输出信号的精确度。但对时序的控制要求较高[7],需谨慎设计前后控制模块的时序。

图3 波形合成部分查找表结构

2.3混合器的实现

每通道的8路信号幅值经过相位波形转换输出后,需要进行并串转换将并行信号转换成串行信号才能输出。Xilinx Vritex-5芯片中的SERDES资源可以实现最高10:1的串并转换效果[8],完全可以满足设计要求。因此,经过OSERDES将并行的8路信号转化为串行输出,就得到最终需要输出到DAC的信号。

3仿真验证

3.1常规正弦波形

在使用Modelsim进行仿真后,导出数据,用Matlab对信号的质量尤其是信号的频域信息进行更直观的分析验证[9]。

本系统的采样频率为1.25 GHz,由于本系统使用的DAC为双输入端口,所以FPGA分为奇偶两路输出,每路的数据速率为1.25 GHz/2。令输入频率为100 MHz,奇路信号的时域波形图即为图4,其中横坐标代表时间,采样点间隔为 1.6 ns;纵坐标代表信号幅值。可以看出周期为 10 ns,频率为 100 MHz。

用Matlab将奇、偶两路信号按顺序重新排列,得到完整的信号时域波形,如图5所示。其中横坐标代表时间,采样点之间的间隔为0.8 ns;纵坐标代表信号幅值。可以看出周期为10 ns,频率为100 MHz。将图4和图5对比可以看出,完整的信号时域波形比奇路信号的时域波形质量更好。

对图5中的信号进行傅里叶变换,得到其对应的频谱,如图6所示。信号的频率为100 MHz,并且信号在频域的质量良好。

图4 奇路信号时域波形图

图5 完整信号时域波形图

图6 常规波形信号频域图

3.2调频波形

令输入频率为100 MHz,调频斜率μ为5 MHz/μs,信号脉宽为10 μs,得到调频信号的频谱如图7所示。

图7 调频信号频谱图

由图7可以看出,线性调频信号的起始频率为100 MHz,调频带宽为50 MHz,终止频率为150 MHz,各项特性均符合理论分析。

6结束语

介绍了一种基于串口服务器的船载卫通站调制解调器监控单元的设计,运用软硬件结合的方法,在不改变现有船载卫通站连接关系基础上,利用串口服务器实现对调制解调器的监控,弥补了现有倒换开关的不足,优化了调制解调器操作菜单,监控单元具有良好的人机交互界面,大幅提升了用户操作设备的便捷性。该设备具有较强的可扩展性,可以应用在卫通链路其它射频设备里,硬件设备无需任何改动,只需更改单片机程序即可。此外,监控单元还具有一机多控的特点,可以同时控制同一机房里的多套调制解调器,只需添加相应的倒换同步开关模块即可,因此具有较大的推广价值。

参考文献

[1]ComtechEFDataCompany.CDM-625Aadvancedsatellitemodem(18kbit·s-1~25Mbit·s-1)installationandoperationmanual[M].Arizona:ComtechEFDataCompany, 2014.

[2]RobertM,Gagliardi.Satellitecommunications[M].Berlin:SpringerPress, 2012.

[3]MOXA公司. 串口转以太网解决方案[J].现代制造, 2004,(3):52-52.

[4]李江全,聂晶,梁习卉子,等. 单片机串口通信及测控应用实战详解[M].北京: 人民邮电出版社, 2014.

[5]周伟,刘易. 单片微机原理及应用[M].北京:机械工业出版社, 2014.

[6]ComtechEFDataCompany.CRS-170Al-band1:1redundancyswitchinstallationandoperationmanual[M].Arizona:ComtechEFDataCompany, 2014.

[7]余晶晶,叶力群,刘长军. 基于嵌入式以太网多频综监控系统设计及实现[J].太赫兹科学与电子信息学报, 2013,11(4):557-560.

[8]赵月静,张永弟,翟卫贺.Proteus和KeilC在开发单片机控制系统中的应用[J].实验科学与技术,2013,11(2):102-104.

Multiphase Structure Waveform SynthesizerBased on FPGA

PENG Yuan,WANG Zhihong

(Key Laboratory of Electronic Information Countermeasure and Simulation Technology Ministry of Education,Xidian University, Xi’an 710071,China)

AbstractTo solve the problem of the constraint on the bandwidth of DDS based on FPGA, this paper introduces a high-speed, wide-bandwidth multiphase structure waveform synthesis method. The working principle of the system and realization method are described in detail, the simulation and analysis of this method is given. Sine wave and FM synthesized by this waveform synthesis method preform well in requency domain.

Keywordsmultiphase waveform synthesis; signal simulator; high bandwidth

收稿日期:2015-10-14

作者简介:袁彭(1992-),男,硕士研究生。研究方向:嵌入式技术应用。王志红(1990-),男,硕士研究生。研究方向:非合作信号处理。

doi:10.16180/j.cnki.issn1007-7820.2016.06.039

中图分类号TN955

文献标识码A

文章编号1007-7820(2016)06-135-04