一种高精度低温漂振荡器设计

2016-07-04王雪艳

王雪艳

(无锡华润上华科技有限公司 上海分公司,上海 201103)

一种高精度低温漂振荡器设计

王雪艳

(无锡华润上华科技有限公司 上海分公司,上海 201103)

摘要针对无线通信和微机械传感器系统对时钟相位噪声的要求,设计了一种高精度低温漂的振荡器电路设计。利用Leeson线形相位噪声模型分析相位噪声,降低了主要噪声源,达到优化相位噪声的目的。该电路在华润上华0.18 μm工艺平台上流片验证。测试结果显示,电源电压在2.2~3.6 V变化,温度在-35~85 ℃变化,频率变化为-2%~+0.5%;相位噪声-116 dBc@1 kHz;4 000个周期的抖动在-1.2%~+1.2%。该电路已成功集成到微机械陀螺仪控制芯片中。

关键词振荡器;相位噪声;高精度;低温漂

振荡器结构包括环形振荡器、LC谐振、张弛振荡器。环形振荡器结构简单、面积小且易集成,但相位噪声和抖动性能差,且振荡频率随电源电压和温度变化较大。LC谐振虽可产生精准的时钟,但集成困难。张弛振荡器电路具有环形振荡器的简单易于集成,同时又具有低的相位噪声和周期抖动。频率随电源电压基本不变,温漂较小,适用于对时钟性能要求严格的系统。

由于噪声的存在,时钟的相位和频率随时间波动,即相位噪声和抖动,这两个指标是衡量时钟精准的主要指标,在多种文献中有研究和分析[1-3],Leeson提出的线性时不变相位噪声模型得到广泛应用[4-6]。

1理论分析

1.1原理分析

张弛振荡器的电路如图1所示,M1和M2为耗尽型晶体管。通常工艺中耗尽型晶体管较增强型晶体管具有更小的1/f噪声。同时由于耗尽型晶体管的衬底可与源端短接,避免了衬偏效应。M3,M4和M5提供偏置电流。

图1 张弛振荡器主体电路

(1)

为便于分析,张弛振荡器的主体电路简化为图2形式。电路中M1~M5宽长比应满足以下要求

图2 振荡器主体电路的简化

本设计输出时钟信号接近正弦波,即M1和M2的源端和漏端信号为正弦,因此电路分析适用线性模型。电路简化成图2,两级环形结构。C1和C2电容值为原来的两倍。电路的开环传递函数为

(2)

(3)

式中,gm代表M1和M2的跨导。电路振荡频率为ω0,H(jω0)=1,单级相移为180°,零点提供90°相移,两个极点分别为1/2R2aC2和1/2R1C1提供剩余的90°相移,得到振荡频率

(4)

当电阻R2比较大时,跨导相当于1/R2[7]。 振荡频率只由电阻和电容值决定,与电流大小无关,不随电源电压变化

(5)

1.2电源电压和温度的影响

电容值和电阻值随温度变化而变化,电容的温度系数一般为 的数量级,较小可忽略。而电阻的温度系数远大于电容的温度系数[8],所以设计中主要考虑电阻的温度系数。工艺中提供多种类型的电阻,这些电阻除了单位方块电阻值不同外,温度系数也不同。通过选择温度系数相反的两种电阻串联,实现串联电阻的低温度系数。本设计选择了P 类型的Poly电阻和P 类型的掺杂电阻。Poly电阻的温度系数为负值,而掺杂电阻的温度系数为正值。正负温度系数可相互抵消

C=C0×[1+TC1×t+TC2×t2]

(6)

R=R0×[1+PTC1×t+PTC2×t2]

(7)

1.3相位噪声的分析

相位噪声由各种随机噪声造成瞬时振荡频率或是相位的变化,该指标反映了频率的稳定度[9]。相位噪声定义为,偏移载波频率fm处,每赫兹带宽内的噪声功率和载波功率的比值,单位dBc/Hz。目前有效的振荡器相位噪声模型由Leeson提出,一般称为Leeson模型,也称为Leeson公式,振荡器由放大和反馈电路组成,以此描述振荡器的相位噪声性能。

图3 Leeson 相位噪声

(8)

式中,F为放大器的噪声系数;K为波尔兹曼常数;T为等效噪声温度;Pavg为放大器的有效输出功率。F因数是经验拟合参数,因此由测量结果决定。Δω1/f3点对应频率是1/Δω2区域和1/Δω3的交点,为器件的1/f噪声拐点。但实际测试结果显示,Δω1/f3点对应频率不是器件的1/f噪声拐点,而是接近1/f噪声拐点的经验拟合值。显然不只有1/f噪声,还有其他噪声,但1/f是主要噪声。振荡器电路中M1和M2的1/f噪声和热噪声的计算公式如下[10]

(9)

(10)

为降低1/f噪声需要增加M1和M2的W和L的乘积,同时W/L减小可降低M1和M2的跨导,减小M1和M2的跨导可降低热噪声。

2仿真结果

采用相位噪声的分析软件得到仿真结果如图4所示。

图4 相位噪声仿真结果

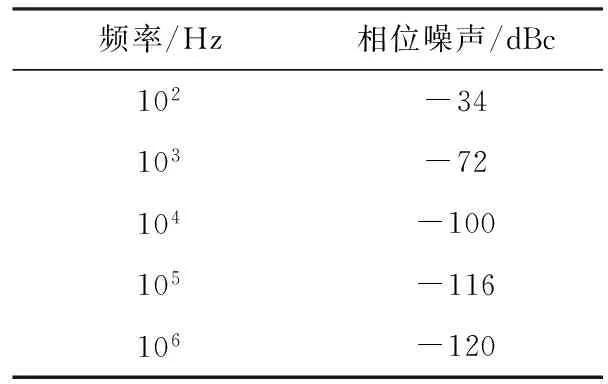

图4横轴是频率,单位Hz。纵轴是相位噪声,单位是dBc/Hz。本文所设计的振荡器相位噪声仿真数据如表1所示。

表1 相位噪声仿真数据

3实验室测试结果

电路在CSMC0.18 μm 1P6M工艺平台上进行了流片,芯片面积为0.02 mm2。图5 是Agilent Signal Analyzer N9020A 测试的相位噪声。

图5 相位噪声测试结果

实验室用LeCrey Wave Pro 735Zi测试抖动。由于抖动本身是个统计数据,需要测试大量输入然后得到统计值。

表2 相位噪声测试数据

图6是振荡器输出频率随温度变化的测试结果,3条曲线分别对应电源电压VDD为2.2 V,3 V和3.6 V输出频率。

图6 振荡频率与温度关系

指标典型值面积0.02mm2电源电压2.2~3.6V功耗100μA4000cycles抖动-1.2%~+1.2%相位噪声-116dB@100HzK温度系数-2%~+0.5%

4结束语

本文介绍了一种高精度低温漂的张弛型振荡器设计。通过简化电路图得到振荡器的函数,利用电阻本身的温度系数来抵消温度对频率的影响。分析主要噪声源和相位噪声的关系,降低器件的 噪声和热噪声,提高振荡器相位噪声和抖动性能。芯片在无锡华润上华0.18 μm 工艺平台上流片成功,封装后在实验室测试,测试结果与设计目标一致。时钟频率随温度变化小,相位噪声低,长时间和短时间抖动小。电路性能达到微机械陀螺仪控制芯片的要求,成功集成在微机械陀螺仪的控制芯片中。

参考文献

[1]Lesson D B. A simple model of feedback oscillator noise spectrum[J].Proceeding of IEEE,1966,54(4):329-330.

[2]Abidi A A, Meyer R G. Noise in relaxation oscillators[J].Solid-State Circuits,1983(18):794-802.

[3]Asad A Abidi. Phase noise and jitter in CMOS ring oscillators[J].IEEE Solid -State Circuits,2006, 41(8):1803-1815.

[4]Thomas H Lee,Ali hajimiri. oscillator phase noise: a tuorial[J].IEEE Solid-State Circuits,2000,35(3):326-336.

[5]Ali Hajimiri,Thomas H Lee.A general theory of phase noise in electrical oscillators[J].IEEE Solid-State Circuits,1998,33(2):179-194.

[6]Margarit M A, Tham J I, Meyer R G, et al.A low-noise, low-p0ower VCO with automatic amplitude control for wireless applications[J].IEEE Solid-State Circuits,1999(34):761-771.

[7]David A,Johns,Ken Martin.Analog integrated circuit design[M].MR,USA: John Wiley &Sons Inc,1997.

[8]Phillip E Allen,Douglas R.Holberg.CMOS analog circuit design second edition[M].Oxford,UK: Oxford University Press, Inc, 2002.

[9]Cutler L S,Searle C L, Some aspects of the theory and measurement of frequency fluctuation in frequency standards[J].Proceeding of IEEE,1966,54(4):136-154.

[10]Willy M C Sansen.模拟集成电路设计精粹[M].陈莹梅,译.北京:清华大学出版社,2008.

Design of a High-precise and Low-temperature-drift Oscillator

WANG Xueyan

(Shanghai Branch, CSMC Technologies Corporation, Shanghai 201103, China)

AbstractAccording to the requirement of clock phase noise of wireless communication and micro mechanical sensor system design, the design of a high precision low temperature drift oscillator circuit. Analysis of phase noise using Leeson linear phase noise model, reduce the main noise source, to optimize the phase noise of the objective. The circuit is taped out in Huarun China 0.18 μm technology platform. Test results show that the power supply voltage from 3.6 V changes and temperature from the change of -35~85 ℃, the frequency change -2% ~ 0.5%; phase noise -116 dBc@1 kHz; 4 000 cycle jitter at -1.2% ~ + 1.2%. The circuit is successfully integrated into the micro mechanical gyroscope control chip.

Keywordsoscillator;phase noise;high precise;low-temperature-drift

收稿日期:2015-10-22

作者简介:王雪艳(1977-),女,硕士,工程师。研究方向:模拟电路设计和模拟数字混合电路设计。

doi:10.16180/j.cnki.issn1007-7820.2016.06.033

中图分类号TN752

文献标识码A

文章编号1007-7820(2016)06-114-03