UART微控制器设计方法及其FPGA实现

2016-07-04戚秀真

杨 澜,戚秀真

(长安大学 信息工程学院,陕西 西安 710064)

UART微控制器设计方法及其FPGA实现

杨澜,戚秀真

(长安大学 信息工程学院,陕西 西安 710064)

摘要为满足FPGA与PC之间的通信需求,提出了一种FPGA的通用异步收发器设计实现方法。在Xilinx ISE 11开发平台上采用Verilog HDL硬件描述语言及其自带的IP CORE,实现了UART精确波特率时钟模块、UART发送模块和UART接收模块。并在ISE环境下进行综合建模仿真,给出各模块的仿真时序图以及综合生成的RTL图。实验通过Xilinx公司的XC2VP30 FPGA开发板对程序进行下载运行调试,与PC进行实时通信,结果表明,UART控制器工作稳定可靠,较好地实现了数据串行通信,达到预期设计要求。

关键词UART;FPGA;Verilog HDL

通用异步收发器 (Universal Asynchronous Receiver Transmitter,UART)是一种通用串行异步通信数据总线,由于其可靠性高、传输距离远、相对成本较低等优点被广泛应用,尤其是在嵌入式微处理器设计中,UART接口已成为不可缺少的一部分[1-3]。其工作原理是UART发送器将接收到的并行数据帧转换成串行数据帧进行传输。如表1所示,串行数据帧包括1个低位1,7~8个数据位,1个可选的奇偶校验位和1个或多个高位停止位[4-5]。UART接收器发现低位起始位后与发送器时钟同步,然后接收整个串行数据帧,最后去掉低位起始位和高位停止位进行相应的奇偶校验生成并行数据帧[6]。目前,FPGA(Field Programmable Gate Array)芯片以其集成度、设计周期短、性价比高可满足时序复杂的大规模设计等诸多优点,被广泛应用于工程中[7-10]。由于大部分FPGA芯片内部并没有集成UART通信功能模块,给FPGA与CPU或其他设备间的数据传输造成不便[11-12]。针对以上问题,并顺应硬件逐渐软件化的发展趋势,本文提出并设计实现了一种基于FPGA的UART驱动程序,不但可省去复杂的UART芯片接口,简化电路,并可增加系统的可靠性和稳定性。

表1 UART帧格式

1基于Verilog HDL的UART模块化设计

设计采用模块化开发方式,根据UART的功能可划分为3个模块:精确波特率时钟模块、发送模块和接收模块。这3模块统一由顶层原理图文件驱动。UART异步传输方式没有传输同步时钟,因此为了保证数据传输质量,UART采用16倍数据波特率的时钟进行采样。每个数据由16个时钟采样,取中间采样值,以保证采样不会滑码或误码。系统时钟为100 MHz,精确波特率时钟模块进行651分频后,得到16倍的波特率(初始波特率为9 600)。发送模块和接收模块由精确波特率时钟模块提供的频率进行数据帧的打包、解析。如需更改波特率,则PC需要与FPGA建立通信协议:选择波特率如2 400、4 800、11 920、115 300时,PC同时向FPGA器件发送特殊字符(如,@#¥%&),同时FPGA在波特率为9 600的情况下进行接收,并根据字符更改分频器的分频数,从而到达同时更改波特率和传输数据。

1.1UART精确波特率时钟模块设计

精确波特率时钟模块是为发送模块和接收模块提供采样所需的频率,并与PC同步波特率。假设UART初始波特率为115 200,则所需时钟频率为16×115 200=1 843 200。UART帧格式为:1位起始位、8位数据位、1位停止位、无校验位。因此数据的最大传输速率为

115 200/N=11 520 B·s-1

(1)

其中,N为数据位10 bit;分频系数为100 000 000/(16×115 200)=54。程序中设置两种计数器,以采样时钟频率的上升沿,并当计数器到达53时信号翻转。

1.2UART发送模块设计

当发送模块接收到发送命令后,会按照约定的通信速率与通信协议输出帧数据,即一个低电平的起始位,然后从低到高输出8个数据位,可选的奇偶校验位,高电平停止位。

1.3UART接收模块设计

接收模块负责将接收的数据进行解析,得到裸数据。即空闲状态时线路处于高电位,当检测数据传输线路的下降沿时说明线路有数据传输,按照约定的波特率从低到高位接收数据。最后接收并比较奇偶校验位是否正确,若正确则通知后续设备准备接收数据或存入缓存。UART接收数据时序为:当检测到数据的下降沿时,表明线路上有数据进行传输,此时计数器CNT开始计数,当计数器为24=16+8时,采样值为第0位数据;当计数器的值为40时,采样值为第1位数据,依此类推进行后续6个数据的采样。若需要进行奇偶校验,则当计数器值为152时,采样值即为奇偶位;当计数器值为168时,采样值为“1”表示停止位,1帧数据接收完成。

2基于PC的串口监视软件设计

基于PC的串口监视软件采用MSComm控件设计,由程序主控模块、串口通信模块和接收显示模块组成,其流程如图1所示。

图1 基于PC的串口监视软件程序流程图

串口初始化设置为波特率9 600,无奇偶校验位,1位停止位。此时与PC波特率相同,进行实时通信。程序还添加了更改波特率功能,以便于高速或低速传输。上位机程序验证实现“自发自收”,将PC机串口RXD和TXD相连接,程序接收框显示发送的数据。

3系统仿真验证

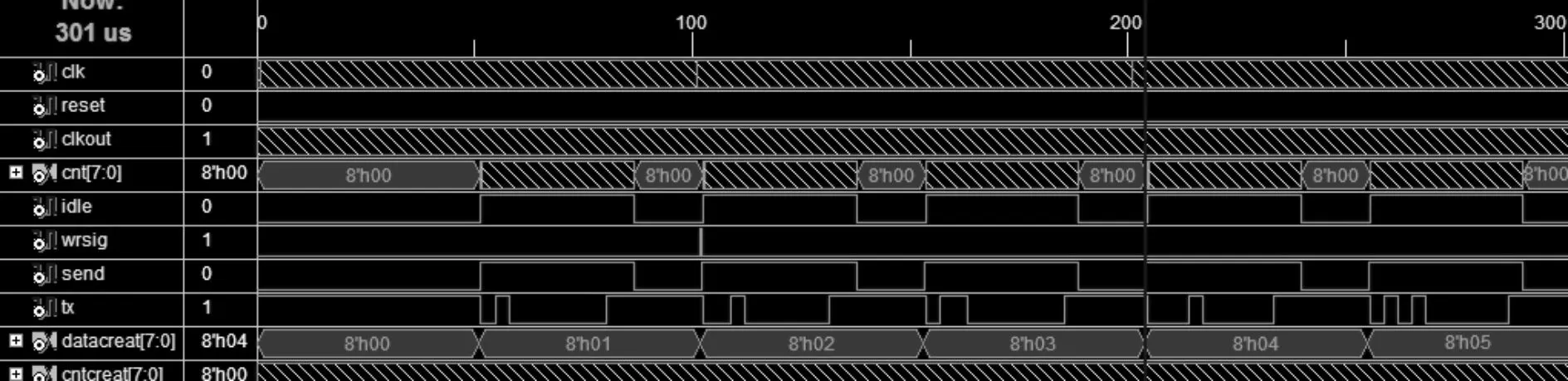

为实现所提出的硬件模块设计,采用硬件描述语言Verilog HDL对各模块功能进行描述,写出RTL级代码,在Xilinx 11.1开发环境下对所有代码进行综合,并在Modelsim下对每一个模块单独均进行了软件仿真。仿真中各加入100 MHz的时钟激励,结果如图2~图4所示。图2中,当计数器为53时进行信号翻转,达到设定波特率。图3中,datacreat的输出与dataout输出相一致,表示发送模块功能实现。图4中,接收模块的输出端数据与数据生成模块的数据相一致,表明接收模块设计正确。

图3 发送端仿真原理图

图4 接收端仿真原理图

图2精确波特率时钟模块仿真结果

如图5所示,建立顶层文件原理图,添加精确波特率模块,数据生成模块,发送模块,接收模块的symbol,借助ISE开发工具对工程进行设计综合、设计实现、芯片配置、在线调试。根据PC的串口调试工具的设置,决定代码是否需要奇偶校验位,以及分频系数。在IPACT软件将测试信息随设计文件下载于Virtex-II PRO XC2VP30开发板中用以捕获目标芯片内部系统信号节点处的信息或总线上的数据流,而又不影响原硬件系统的正常工作。测试信息通过器件的JTAG端口传出,并送入计算机进行显示和分析。如图6所示,通过本文所提串口监视软件将数据从计算机送出,并利用FPGA器件中的UART模块接收,并发送回PC显示。经多次测试,收发数据完全相同。结果表明,PC与FPGA可正常进行串口通信,并可更改波特率,数据传输正确。

图5 顶层文件原理图

图6 更改波特率后进行串口通信

4结束语

本文提出并设计实现了PC与FPGA通信的UART微控制器驱动程序,同时开发了基于PC的上位机测试程序以论证该UART微控制器设计的正确性。基于FPGA的UART与传统方法相比可简化系统PCB电路,降低系统能耗,提高系统的可靠性和芯片的专用性。该UART模块可作为完整的IP核移植进各种FPGA中,在实际应用时可嵌入到其他系统中。

参考文献

[1]胡立坤,王庆超.基于UART的可靠通信与性能分析[J].计算机工程,2006,32(10):15-17,21.

[2]张松,董玲,于宗光,等.一种适合于SoC集成的UART核的设计实现[J].微电子学与计算机,2005, 22(9):10-13.

[3]刘先博.基于FPGA与MCU的多串口通信接口设计与实现[D].南京:南京理工大学,2014.

[4]杨晶.基于FPGA的UART接口协议转换模块设计[D].哈尔滨:哈尔滨工业大学,2014.

[5]段素蓉,庄圣贤.一种内置FIFO全双工UART的设计与实现[J].通信技术,2010,43(2):46-47.

[6]何健标,王宏远,林静宜,等.基于最佳接收的UART的设计与实现[J].电子技术应用,2006,32(8):55-58.

[7]张兴军,丁彦飞,黄一元,等.基于FPGA的动态部分可重构高性能计算实现[J].华中科技大学学报:自然科学版,2010,38(S1):82-86.

[8]Kuon I,Rose J.Measuring the gap between FPGAs and ASICs[J].IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems,2007,17(6):152-160.

[9]杨海钢,孙嘉斌,王慰. FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-727.

[10]杨莉莉,郭亮.基于FPGA的磁悬浮微驱动器控制系统研究[J].机电工程,2015,32(11):1483-1488.

[11]魏丽玲,朱平,石永亮.基于FPGA的图像采集与存储系统设计[J].电子技术应用,2015,41(11): 67-69.

[12]宋宇飞,张俊杰,王凯,等.基于IP协议的FPGA万兆可靠互联通信设计与实现[J].上海大学学报:自然科学版,2015,21(5): 570-578.

Design and Implementation of UART Controller Using FPGA

YANG Lan,QI Xiuzhen

(College of Information Engineering,Chang’an University,Xi’an 710064, China)

AbstractIn order to realize the communication between FPGA and PC, we design and implement a UART controller based on the Field Programmable Gates Array (FPGA). In the Xilinx ISE 11 development platform, we use the Verilog HDL language and its own IP CORE to implement the receiving module, sending module and precise baud rate clock module. Finally we use XC2VP30 device to verify the function of the UART. The results show that the UART module is stable and reliable.

KeywordsUART; FPGA; Verilog HDL

收稿日期:2015-12-23

基金项目:国家自然科学基金资助项目(51278058);中央高校基本科研业务费专项基金资助项目(2013G5240009,310824151035)

作者简介:杨澜(1985-),女,博士。研究方向:数字信号处理与多源信息融合技术。

doi:10.16180/j.cnki.issn1007-7820.2016.06.021

中图分类号TN79;TP391

文献标识码A

文章编号1007-7820(2016)06-072-03