高精度帧时延测量装置的设计与实现

2016-05-31王伟鲁海威王圣达石珏陈鹤中兴通讯股份有限公司南京00国网吉林供电公司吉林吉林0国网吉林省电力有限公司信息通信公司长春00国网长春供电公司长春005

王伟,鲁海威,王圣达,石珏,陈鹤(.中兴通讯股份有限公司,南京00;.国网吉林供电公司,吉林吉林0;.国网吉林省电力有限公司信息通信公司,长春00;.国网长春供电公司,长春005)

高精度帧时延测量装置的设计与实现

王伟1,鲁海威2,王圣达3,石珏4,陈鹤3

(1.中兴通讯股份有限公司,南京210012;2.国网吉林供电公司,吉林吉林132011;3.国网吉林省电力有限公司信息通信公司,长春130021;4.国网长春供电公司,长春130051)

摘要:为解决传统时延测量装置测量精度不高的问题,设计了一款基于FPGA的高精度帧时延测量装置,描述了Y. 1731帧时延测量的原理,并着重介绍了装置通过FPGA辅助进行高精度帧时延测量的设计流程。

关键词:Y. 1731;帧时延; FPGA

0 引言

随着电信级以太网技术的发展和标准日益完善,以太网操作、管理和维护(OAM)凭借其在监控网络性能,检测、定位网络故障方面发挥的重要作用,得到了更多运营商的重视。ITU Y.1731对基于虚拟局域网(VLAN)的以太网定义了一套协议和协议实体[1],它是一种二层链路上基于VLAN的端到端OAM机制,可用于检测二层网络中链路的连通性,确认故障和故障发生的位置。Y.1731定义了管理实体组(MEG),并在此基础上定义了管理实体群端点(MEP)和管理实体群中间节点(MIP),根据功能划分为故障管理和性能监控两个部分。故障管理部分的功能有连续性检测(CCM)、环回检测(LB)、链路跟踪(LT)、以太网告警指示信号(AIS)和以太网锁定信号(LOCK)。性能监控有帧丢失率测量(LM)和帧时延测量(DM)[2]两种,本文主要讨论其中的帧时延测量功能。传统的时延测量方法存在时钟误差和位置误差,导致测量精度较低。因此,本文介绍一种高精度的帧时延测量方法。

1 Y.1731帧时延测量原理

在配置了正确的MEG和MEP后,帧时延测量装置开始进行Y.1731中定义的两种帧时延测量,即单向时延测量(1DM)和双向时延测量(DMM)。

1.11DM原理

每个MEP在点到点管理实体(ME)中向与其对等的MEP发送带有单向以太网帧时延测量(ETH-DM)信息的帧(1DM帧),以便在对等MEP上进行单向帧时延和(或)单向帧时延变化的测量[3]。对端根据收到的1DM报文中的接收时间戳(RxTimeStampf)和发送时间戳(TxTimeStampf)进行时延计算,根据Y.1731中定义的时间戳格式,时间戳精确到纳秒级。由于TxTime-Stampf由发送方填充,RxTimeStampf由接收方填充,因此,要求收发两端时钟保持高度同步,否则误差很大。

1.2DMM原理

MEP向其对等的MEP发送有ETH-DM请求信息的帧(DMM帧),并从其对等的MEP接收有ETHDM回复信息的帧(DMR帧),以进行双向帧时延和(或)双向帧时延变化的测量[3]。双向帧时延测量由发送DMM帧一方发起并负责时延计算,对端收到DMM帧后立即回应DMR帧。发起一方收到回应的DMR帧后,根据DMR帧中的DMR接收时间戳(RxTimeStampb)、DMM发送时间戳(TxTimeStampf)、DMR发送时间戳(TxTimeStampb)和DMM接收时间戳(RxTimeStampf)字段计算时延,根据Y.1731中定义的时间戳格式,时间戳精确到纳秒级。双向时延测量虽然不要求两端时钟高度同步,但要求双方本地时钟精确度较高,否则误差较大。

从以上分析可知,帧时延测量对系统时钟精确度要求很高,而传统的软件帧时延测量方法依赖于操作系统的时钟精度,帧时延测量结果不够理想,不能反映真实的网络传输质量。

2 装置设计方案

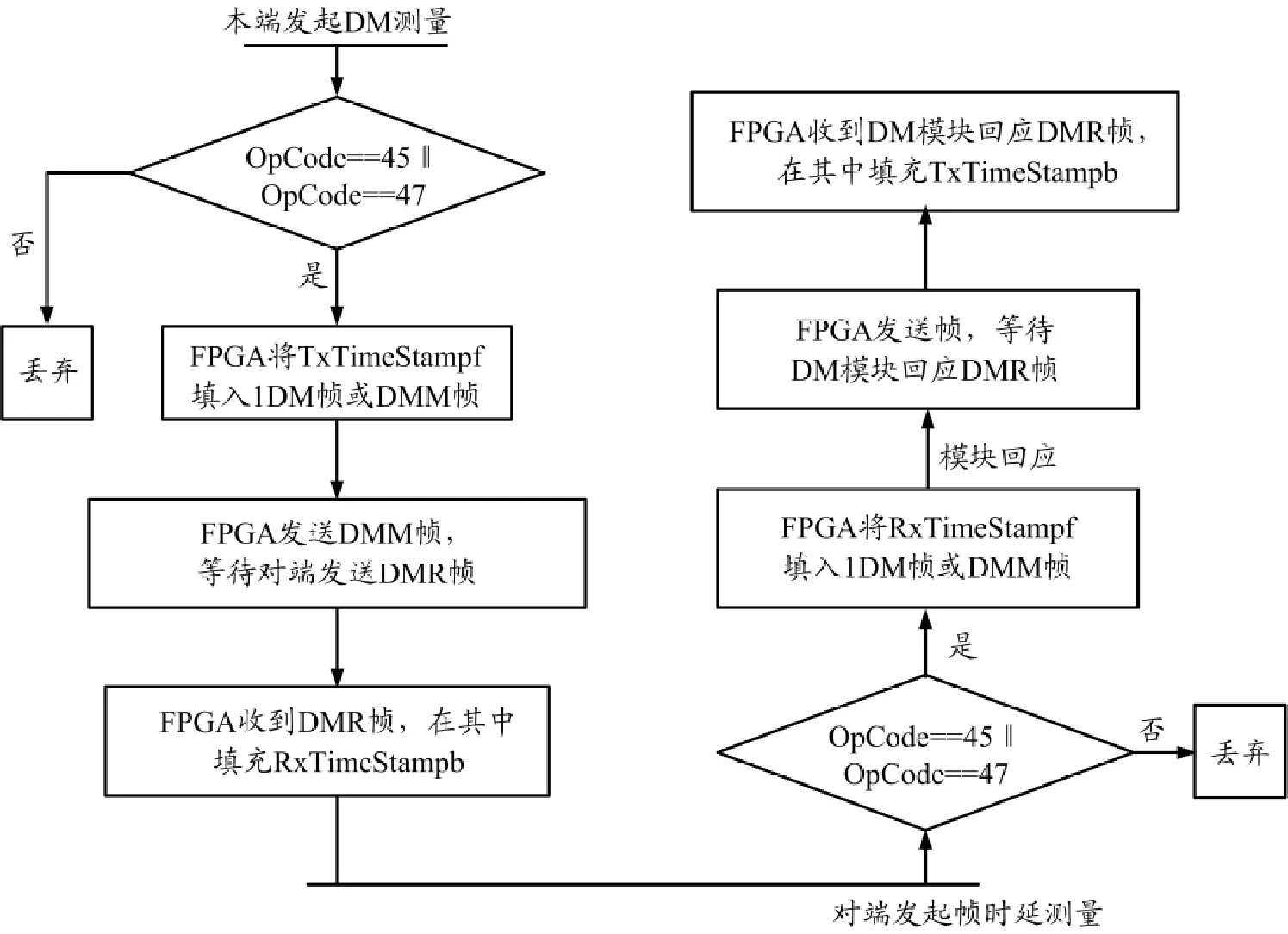

基于FPGA模块实现的高精度帧时延装置主要由FPGA模块、帧时延测量模块和驱动模块3部分组成。其中FPGA模块为帧时延测量相关帧填充时间戳。帧时延测量模块用于处理FPGA接收的帧时延测量相关帧,完成单向或双向帧时延测量功能。驱动模块的功能是关联FPGA模块和帧时延测量模块,将帧时延测量模块的配置信息转换为FPGA对应表项,对FPGA接收到的报文通过中断通知帧时延测量模块进行处理;提供接口,完成FPGA初始化和时钟同步。高精度帧时延装置的设计流程如下,具体流程图如图1和图2所示。

①帧时延测量模块按需发送帧时延测量帧:1DM帧或DMM帧。帧时延测量模块组装正确的二层报文发送给驱动模块,驱动模块查询FPGA 中FIFO状态标志位是否为1:为1则通过PCI总线向FPGA下发报文;为0则提示帧时延测量模块重新发送报文。发送完成后,驱动模块置状态标志位为0,通知FPGA从FIFO中提取报文,FPGA提取完毕后,将状态标志位复位为1。

②FPGA模块先判断提取出的报文是否是正确的以太网报文,再判断报文中的OpCode字段数值。OpCode字段等于45或47时,FPGA继续处理;否则丢弃。

图1 装置设计流程1

图2 装置设计流程2

③FPGA提供寄存器,帧时延测量模块负责初始化时钟,由FPGA自行时钟计数。驱动模块提供接口,供外部模块进行时钟同步。FPGA接收到由帧时延测量模块发送的1DM帧或DMM帧后,获取当前FPGA时钟滴答数,按Y.1731规定的时间戳格式进行转换并将TxTime-Stampf字段填入1DM帧或DMM帧。

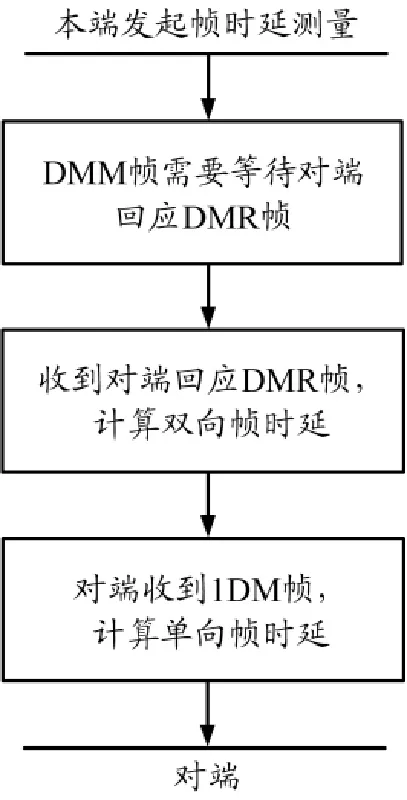

④FPGA发送1DM帧或DMM帧,对端帧时延测量模块可以测量单向帧时延,具体方法如步骤11○。双向帧时延测量需要等待对端回应DMR报文。

⑤FPGA接收从网络侧传送的DMR帧,获取当前FPGA时钟滴答数,按Y.1731中规定的时间戳格式进行转换并将RxTimeStampb字段填入DMR帧中,通过驱动模块将填充后的DMR帧传给帧时延测量模块进行处理,帧时延测量模块可以计算出双向帧时延,具体方法如步骤(12)。

⑥对端主动发起帧时延测量,FPGA负责接收帧,通过PCI总线传递给帧时延测量模块计算时延。

⑦FPGA模块判断报文中的OpCode字段,当Op-Code等于45或47时,FPGA继续处理;否则丢弃。

⑧FPGA接收到从网络侧传送的1DM帧或DMM帧后,获取当前FPGA时钟滴答数,按照Y.1731中规定的时间戳格式进行转换并将RxTimeStampf字段填入帧中。

⑨FPGA通过PCI总线将帧透传给帧时延测量模块进行处理,双端的帧时延测量需要帧时延测量模块回应DMR帧。

⑩FPGA收到帧时延测量模块回应的DMR帧,获取当前FPGA时钟滴答数,按照Y.1731中规定的时间戳格式进行转换并将TxTimeStampb字段填入帧中,发送给对端测量节点,对端可以计算双向帧时延。

(11)对端收到本端发出的1DM帧后,提取1DM报文中的RxTimeStampf、TxTimeStampf字段计算单向帧时延。时间戳TxTimeStampf处理如步骤③,RxTimeS-tampf处理如步骤⑧。单向帧时延=RxTimeStampf-Tx-TimeStampf。

(12)帧时延测量模块收到对端回应的DMR帧,根据DMR帧的管理实体组等级(MEG LEVEL)和以太网报文头部的VLAN判断收到的DMR帧是否是本端发出的DMM帧对应的DMR帧。若不是,帧时延测量模块丢弃DMR帧,不进行处理;若是,则提取DMR帧中的RxTimeStampb、TxTimeStampf、TxTimeStampb、RxTimeStampf字段计算时延,时间戳TxTimeStampf处理如步骤③,RxTimeStampb处理如步骤⑤,RxTimeStampf处理如步骤⑧,TxTimeStampb处理如步骤⑩。双向帧时延=(RxTimeStampb-TxTimeStampf)-(TxTimeStampb-RxTimeStampf)。

3 结束语

随着Internet的规模指数级膨胀,网络的分布化、异质性和不协作性正逐渐增强,控制和管理网络变得越来越困难,对网络性能的整体把握也更复杂,时延测量是了解网络运营状态并对其进行优化的重要手段[4]。本文设计的基于FPGA的高精度帧时延测量装置解决了纯软件帧时延测量系统测量精度较低和可靠性不高的问题,监控网络时延可以达到纳秒级别,具有很大的实际应用价值。采用本装置的无源光网路(XPON)多用户接入单元可广泛应用于FTTB/FTTC业务,提供宽带、E1/T1和IPTV业务,特别是移动通讯基站回传等对时延要求较高的场景。

参考文献:

[1]陶映旭. ITU-T Y.1731的软件实现与优化分析[D].杭州:杭州电子科技大学,2010.

[2]黄志忠.基于测量的网络管理技术研究[D].成都:电子科技大学,2011.

[3] SHANEEL N, PAULA R L. Impact on network performanc of jumbo-frames on IPv4/IPv6 network in frastructure:an empiricaltest-bed analysis[C]. Bangalore, Karnataka: IEEE4th International Conference on Internet Multimedia Services Architecture and Application, 2010.

[4]路启銮.网络链路时延测量技术的研究[D].曲阜:曲阜师范大学,2010.

Design and implement of high-precision frame delay measure device

WANGWei1, LUHai-wei2, WANGSheng-da3, SHIYu4, CHENHe3

(1. ZTE Corporation, Nanjing 210012, China; 2. Jilin SGCC, Jilin Jilin 132011, China; 3. Jilin State Grid Information & Telecommunication Company,Changchun 130021, China; 4. Changchun SGCC, Changchun 130051, China)

Abstract:In order to solve the problem that the traditional time delay measurement device measuring precision is not good enough, the paper introduces a high-precision frame delay measurement device based on FPGA, describes the measure principle of Y.1731 frame delay, and emphatically introduces the design process of the device how to measure high-precision frame delay through FPGA.

Key words:Y.1731,frame delay, FPGA

中图分类号:TP274.2

文献标识码:A

文章编号:1002-5561(2016)01-0029-03

DOI:10.13921/j.cnki.issn1002-5561.2016.01.009

收稿日期:2015-10-08。

作者简介:王伟(1982-),男,硕士研究生,主要研究方向为XPON终端研究和开发。