GNSS射频芯片中小数分频技术研究

2016-05-14李鑫黄海生

李鑫 黄海生

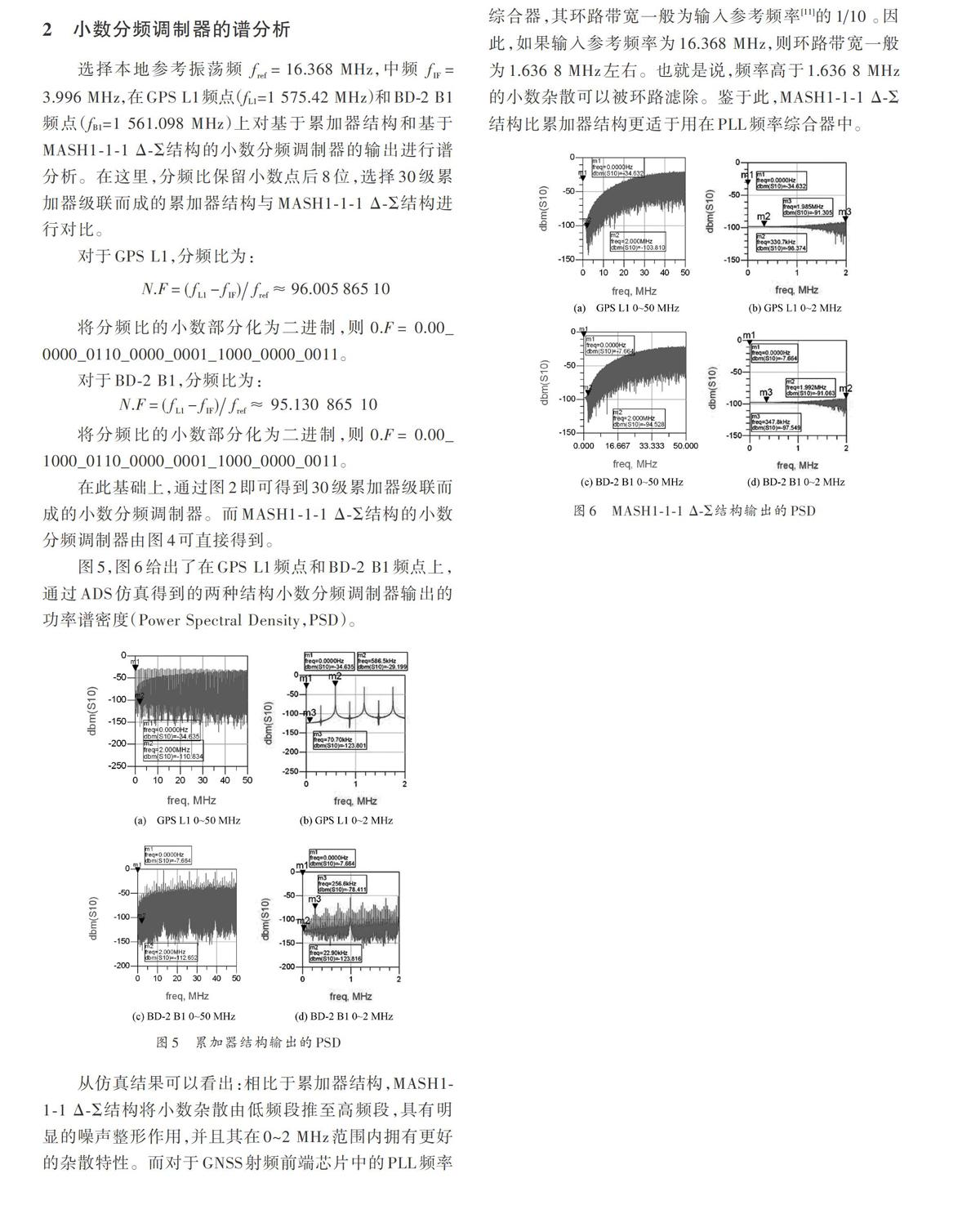

摘 要: 针对GNSS射频前端PLL频率综合器中的低杂散小数分频问题,提出了分别基于累加器结构和MASH1?1?1 Δ?∑结构的两种小数分频调制器实现方案。进而选取3.996 MHz为GNSS射频前端模拟中频频率,16.368 MHz为PLL频率综合器参考频率,在GPS L1和BD?2 B1频点上对30级累加器级联结构和MASH1?1?1 Δ?∑结构的输出功率谱进行分析,并在此基础上对它们的小数杂散特性进行了对比研究。结果表明,MASH1?1?1 Δ?∑结构具有噪声整形功能,可将小数杂散由低频段推至高频段,从而在低频段获得更优的杂散特性。由于高频段的杂散可被PLL环路滤波器滤除,故MASH1?1?1 Δ?∑结构更适合用在基于PLL的频率综合器中。

关键词: 小数分频; 累加器; MASH1?1?1 Δ?Σ调制器; 小数杂散

中图分类号: TN402?34 文献标识码: A 文章编号: 1004?373X(2016)05?0055?03

0 引 言

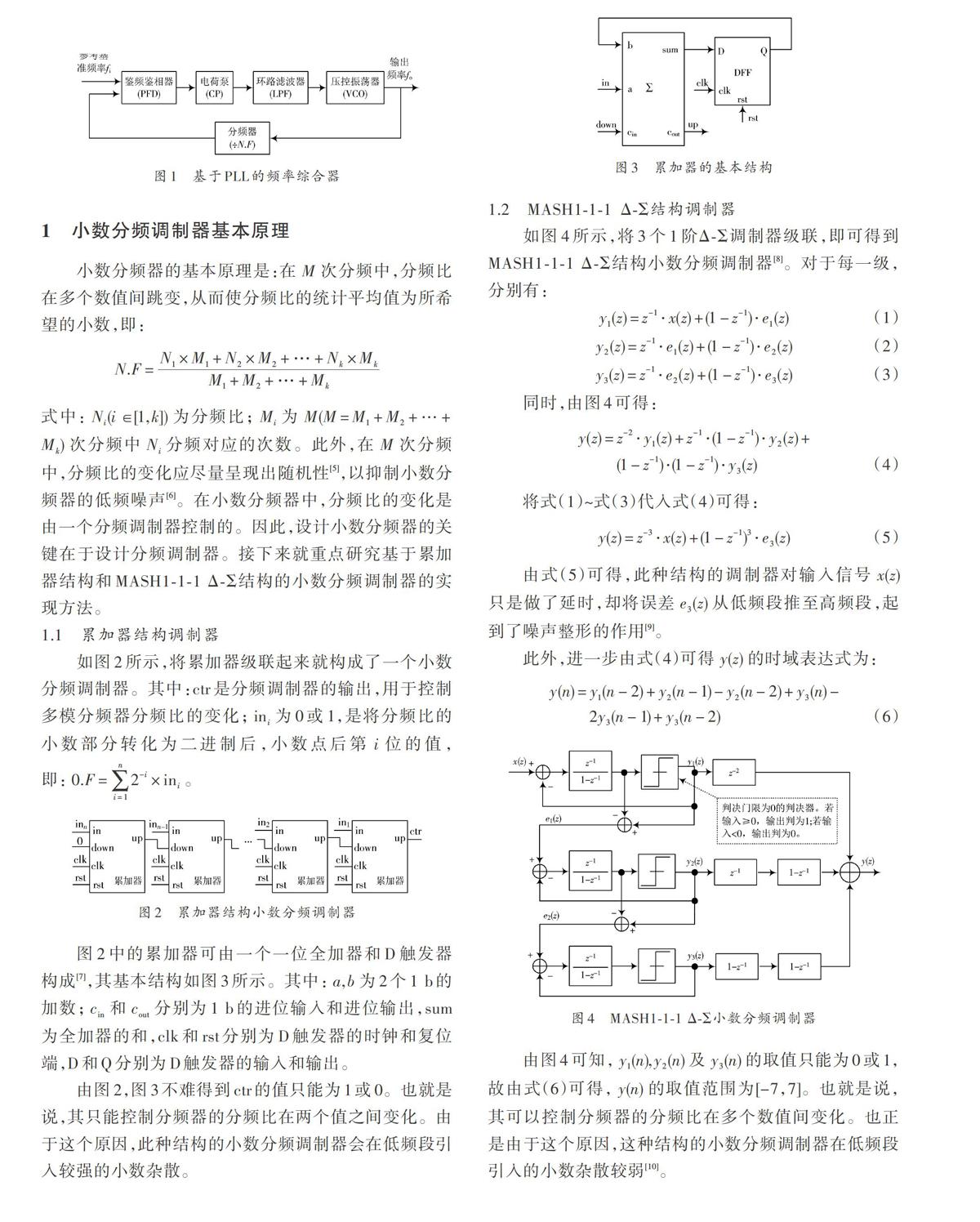

射频芯片是全球导航卫星系统(Global Navigation Satellite System,GNSS)接收终端的核心部件,其需要将天线接收到的极微弱的卫星信号进行滤波、放大、下变频,进而对下变频得到的模拟中频信号进行A/D转换,从而生成数字信号供基带电路处理[1]。通常用于下变频的本振频率是由频率综合器对参考基准频率倍频得到的,倍频后的本振信号与接收到的GNSS射频信号作用于混频器即可得到模拟中频信号。如图1所示,频率综合器实际上可由一个锁相环(Phase Locked Loop,PLL)实现[2]。在环路锁定状态下,[fo=N.F×fi,]即频率综合器的倍频系数等于分频器的分频比。在很多情况下,由于所期望的本振频率与参考基准频率并非整倍数关系,因此分频器的分频比通常为小数[N.F,]这就在环路中引入了小数杂散[3]。由于小数杂散通常在环路带宽内,无法通过环路滤波器滤除,因此会导致输出的本振信号出现杂散频率,并最终使混频后得到的模拟中频信号频谱纯度变差[4?5]。鉴于此,就要求用于频率综合器中的小数分频器在环路带宽范围内引入的小数杂散尽可能小。本文重点研究了基于累加器结构和基于MASH1?1?1 Δ?Σ结构小数分频调制器的输出功率谱特性,结果表明,后者在低频段抑制小数杂散的效果更为理想。

3 结 语

累加器结构的小数分频调制器可控制分频比在两个值(N和N+1)之间跳变;而MASH1?1?1 Δ?Σ结构则可控制分频比在多个数值之间跳变[7]。因此,后者可将小数分频器产生的噪声由低频段推至高频段,其具有噪声整形功能。而高频段的噪声可被PLL环路滤波器滤除,从而较好地抑制小数杂散,故MASH1?1?1 Δ?Σ结构更适于用在PLL频率综合器中。而累加器结构的小数分频调制器结构简单,设计实现更容易,并且仅通过提高参考频率就可以在时域将抖动降得很低,因此将其更多用于通信中的时钟数据恢复电路中[7]。

参考文献

[1] TSUI J B Y. Fundamentals of global positioning system receivers: a software approach [M]. Hoboken: John Wiley & Sons, 2000.

[2] RAZAVI Behzad.模拟CMOS集成电路设计[M].陈贵灿,译.西安:西安交通大学出版社,2003.

[3] 吴恩德,王志华,张利,等.分数N频率综合器的杂散分析[J].清华大学学报(自然科学版),2004(7):958?961.

[4] LAUER A, FOLLMANN R, QUIBELDEY M, et al. A fractio?nal?N PLL spur and phase noise simulator [C]// Proceedings of 6th European Microwave Integrated Circuit Conference. Manchester: IEEE, 2011: 418?421.

[5] XU Z L, GYU L J, MASUI S. Self?dithered digital Δ?Σ modulators for fractional?N PLL [J]. IEICE transactions on electro?nics, 2011, 94(6): 1065?1068.

[6] 杨辰光.应用于GPS中的Σ?Δ小数分频电路的研究[D].西安:西安电子科技大学,2012.

[7] 李鑫,黄海生,惠楠,等.一种E1时钟数据恢复电路的设计[J].西安邮电学院学报,2012,17(3):67?72.

[8] 晏敏,徐欢,乔树山,等.小数分频频率合成器中Σ?Δ调制器设计与实现[J].湖南大学学报(自然科学版),2014(10):91?95.

[9] ZHANG Yuanyuan, JIANG Yanfeng. Noise shaping Σ?Δ modulation techniques and models simulation [C]// Proceedings of 2006 8th International Conference on Solid?State and Integrated Circuit Technology. Shanghai, China: IEEE, 2007: 1471?1473.

[10] VENGATTARAMANE K, CRANINCKX J, STEYAERT M. Analysis of fractional spur reduction using Σ?Δ noise cancellation in digital?PLL [C]// Proceedings of 2009 IEEE International Symposium on Circuits and Systems. Taipei, China: IEEE, 2009: 2397?2400.

[11] GARDNER F M. Phase lock techniques [M]. 3rd ed. Hoboken: John Wiley & Sons, 2007.