基于北斗授时的雷达接口时序设计方法

2016-01-20江良剑熊善泉焦海松周志全

江良剑,熊善泉,焦海松,周志全

(中国洛阳电子装备试验中心,河南 洛阳 471003)

基于北斗授时的雷达接口时序设计方法

江良剑,熊善泉,焦海松,周志全

(中国洛阳电子装备试验中心,河南 洛阳 471003)

摘要:为解决某雷达数据接口系统工作不稳定、故障率高的问题,利用北斗导航模块的授时功能,通过FPGA读取北斗时间,为雷达数据提供准确的时间信息。在北斗模块1 PPS的同步下,生成雷达测距系统和角编码系统数据输出所需的时序信号,确保雷达按正确的时序将数据放置在总线上。设计中解决了时间信息与1 PPS不同步和原系统时序信号抖动较大的问题,在某雷达数据接口系统改造中得到成功应用。

关键词:北斗授时;1 PPS;时序信号

doi:10.13442/j.gnss.1008-9268.2015.02.010

中图分类号:P228.4

文献标志码:: A

文章编号:: 1008-9268(2015)02-0043-05

收稿日期:2014-12-11

作者简介

Abstract:A radar data interface system works unstably, and the rate of failure is high, in order to solve these problems, the interface circuit has to be redesigned. Using Beidou navigation module timing function, the FPGA reads the Beidou time, and provide accurate time information to radar data. In the synchronous of 1 PPS output by Beidou module, timing signals are generated, which is required by radar ranging system and angle code system when data output, it can ensure that the radar puts the data on the bus in the correct time series. The design solves the problem of time information and 1 PPS not synchronized and the old system timing signal instability, it has been successfully applied in the reconstruction of a radar data interface system.

0引言

某型雷达的数据输出依赖于外部时统终端的“20 Hz采样信号”和数据输出“位同步”信号,雷达数据接口板接收到20 Hz的数据请求信号后,将目标数据准备好并放在120位数据寄存器上,当位同步信号到来时,寄存器便以“位同步”的速率将数据移位输出。由于数据接口终端和雷达数据接口板工作数千小时,电路稳定性降低,故障时有发生,数据产生不规律跳点,影响数据有效性,为此提出对雷达数据接口系统进行改造。

改造的关键在于时序电路设计,产生相关的时序信号代替雷达数据接口板,驱使雷达测距和角编码系统按照时序将距离、俯仰、方位数据依次放在12位数据总线上。项目采用我国自主研制的北斗系统作为授时源,具有精度高、稳定性好的特点,同时可与其他采用卫星导航时统的参试装备协同统一工作, 为得到某时间点上准确可信的数据信息提供很好的时统标准。

北斗模块选用和芯星通的UM220北斗/GPS双模芯片,控制电路采用FPGA器件,设计一套集北斗时统和时序信号生成的模块,为雷达数据接口改造提供基础。

1时统电路设计

和芯星通的UM220北斗/GPS双模芯片,能够同时支持BD2 B1、GPS L1两个频点,可通过设置使选择双系统同时工作或单系统工作,1 PPS精度(RMS)为20 ns,该芯片外形尺寸紧凑,采用SMT 焊盘,适用于低成本、低功耗领域,满足系统开发要求[1]。

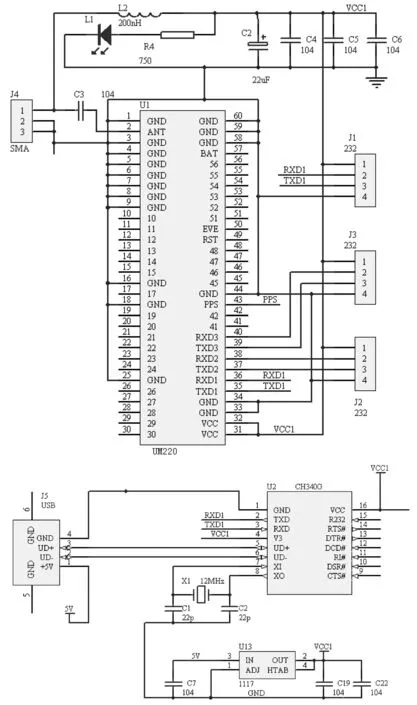

1.1 时统电路设计

UM220输入电压范围为+3.0~3.6 VDC,系统采用5V供电,通过AM1117 3.3进行电压转换。天线采用SMA孔座接口,提供1 个输出脉宽和极性可调的1 PPS 信号。设计3 个串口,串口1 支持NMEA 数据输出及命令控制,串口2 仅支持数据输出,串口3 支持固件升级、NMEA 数据输出及命令控制。输入/输出信号类型为LVTTL 电平。目前的计算机已逐渐取消串口,为方便对UM220进行设置与控制,将串口1并联至CH340G芯片的TXD、RXD引脚,实现串口USB转换功能。时统电路设计如图1所示。

图1 时统电路原理图

1.2 北斗模块设置

为满足系统开发要求,确保接口时序电路正常工作,在开发前需要对北斗模块进行初始化设置。在Unicore 协议中,输入和输出的语句被统称为消息。每条消息均为全ASCII 字符组成的字符串。消息的基本格式为[2]

联系人: 江良剑 E-mail: fjdajian@tom.com

$MSGNAME,data1,data2,data3,…[*CC]

所有的消息都以'$'(0x24)开始,后面紧跟着的是消息名。之后跟有不定数目的参数或数据。消息名与数据之间均以逗号(0x2C)进行分隔。最后一个参数之后是可选的校验和,以'*'(0x2A)与前面的数据分割。输出的消息以" "结束。

根据系统要求,对UM220进行设置。首先设置串口1输出波特率为9 600 bps,设置命令为

$CFGPRT,1,0,9600,3,3

然后配置授时脉冲,设定授时脉冲为1 PPS,脉宽500 ms,上升沿与整秒对齐:

$CFGTP,1000000,500000,1,0,0,0

接着设定只输出GGA消息,速率为1 Hz:

$CFGMSG,0,0,1

最后设定卫星系统配置,选择北斗卫星定位:

$CFGSYS,h01

也可以设置成GPS卫星定位或北斗/GPS双系统定位,设置命令分别为

$CFGSYS,h10或$CFGSYS,h11.

通过以上设置,UM220只输出$BDGGA信息,该信息中包含系统需要的时间信息和定位状态信息。

2时间信息解码

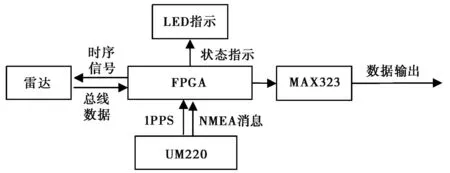

雷达接口电路改造选用FPGA器件具有高度灵活、可定制化的特点,它融入微处理器技术、数字信号处理技术、可编程系统级芯片设计和软硬件协同设计技术,在QuartusII集成开发环境下采用VerilogHDL语言实现系统的模块化设计开发,效率较高。图2示出了雷达接口系统设计框架。FPGA芯片采用Altera公司生产的EP4CE15F17C8作为控制核心[3],配置芯片采用EPCS64.FPGA芯片采用JTAG方式进行配置。在电路设计过程中,考虑工作状态的可视性,增加LED指示灯。

图2 系统的总体框图

根据前面北斗模块的设置可知,图2中UM220输出给FPGA的NMEA消息为$BDGGA,它是在NMEA 3.0 基础上扩展BD2 相关语句的版本,其消息格式为

$BDGGA, time, Lat, N, Lon, E, FS, NoSV, HDOP, msl, M, Altref, M, DiffAge, DiffStation*cs.

项目中用到的字段为time和FS,其中: time:UTC 时间,格式为hhmmss.sss,hh为小时,mm 为分钟,ss.sss为秒; FS:定位状态标识,0 表示无效,1 表示单点定位。

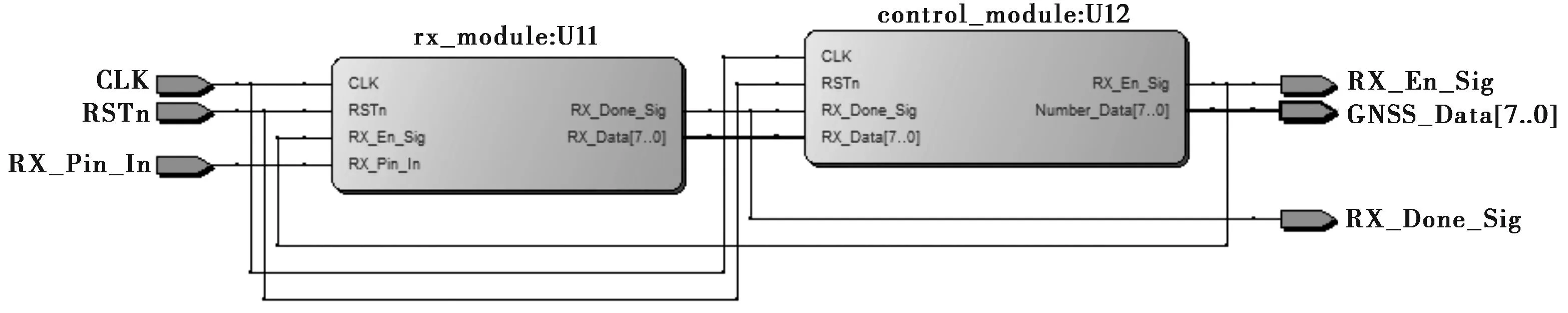

时间信息解码功能在FPGA中通过两个子模块实现,分别是串口数据接收模块GNSS_data_receive_module和时间解算模块time_module.

串口数据接收模块原理图如图3所示,主要完成北斗导航信息接收,信息为RS232数据帧格式,包含1位起始位(保持一个传输位周期的低电平),8位数据,无校验位,1位停止位。

图3 串口接收原理图

以下是一段接收一个字节数据的VerilogHDL程序,FPGA实时监测RS232_RX引脚信号,当出现下降沿时,表示有数据到达,程序将RX_En_Sig 置1,进入数据接收状态,同时H2L_Sig置1,启动数据接收过程,当接收完一个字节后,把接收到的数据送到时间解算模块进行处理。

if(RX_En_Sig)

case (i)

4'd0:

if(H2L_Sig) begin i <=i+1'b1; isCount <=1'b1; end

4'd1:

if(BPS_CLK) begin i <=i+1'b1; end

4'd2, 4'd3, 4'd4, 4'd5, 4'd6, 4'd7, 4'd8, 4'd9:

if(BPS_CLK) begin i <=i+1'b1; rData[i-2] <=RX_Pin_In; end

4'd10:

begin i <=i+1'b1; isDone <=1'b1; isCount <=1'b0; end

4'd11:

begin i <=4'd0; isDone <=1'b0; end

endcase

时间解算模块处理串口数据接收模块发来的数据,提取导航信息中的时分秒数据,并生成毫秒数据,按照预定格式交给雷达数据控制模块。程序捕获$BDGGA消息的开始标志符“$”,提取第8~13字节的时间数据和第七字段状态定位标识FS.为了兼容GPS模式和北斗/GPS双系统模式,程序中将不判断其定位系统标识符。需要注意的是读取到的时间为UTC时间,需要加上8小时时差转换为北京时间。此时得到的是滞后大约几十毫秒的时间信号,还需通过精确的1 PPS信号进行同步处理,得到一个与北斗时同步的时间信号。

时间解算出来后,将其按照5位时、6位分、6位秒、5位毫秒(权重为50毫秒)的二进制格式编码,放在寄存器中等待雷达数据读取后打包输出。以下是获取时分秒信息并进行二进制编码的Verilog程序。

if(RX_Done_Sig)

begin

//rData=GNSS_Data; $--GGA,time,Lat,N,Lon,E,FS,…

if (GNSS_Data==8'h24) i=6'd1;//8'h24为信息起始’$’

case (i)

6'd1,6'd2,6'd3,6'd4,6'd5,6'd6,6'd7://忽略 “$--GGA,” 兼容其他定位系统模式

i <=i+1'b1;

6'd 8://时,十位

begin i <=i+1'b1; rData <=(GNSS_Data-8'h30)*10; end

6'd 9://时,个位,修正8小时时差

begin i <=i+1'b1; rData=rData+GNSS_Data-8'h30+8'd8;

rData=rData % 8'd24;hh=rData[4:0]; end

6'd1 0://分,十位

begin i <=i+1'b1; rData<=(GNSS_Data-8'h30)*10;end

6'd1 1://分,个位

begin i <=i+1'b1; rData=rData+GNSS_Data-8'h30;

mm=rData[5:0]; end

6'd1 2://秒,十位

begin i <=i+1'b1; rData<=(GNSS_Data-8'h30)*10;end

6'd1 3://秒,个位

begin i <=i+1'b1; rData=rData+GNSS_Data-8'h30;ss=rData[5:0]; end

6'd48://FS定位状态标识

begin bFS=GNSS_Data[0]; i <=i+1'b1;end

default:

if ((i>6'd13) && (i<6'd48)) i <=i+1'b1;else i <=1'b0;

endcase

end

3时序信号生成

时序信号是雷达数据输出时与其他系统(如时基、编码、测距、引导等)交互时所需的时序信号,其他系统在时序信号的统一协调下将数据准备好,并按次序放在总线上,时序产生正确与否直接影响到接口系统能否正确读取雷达数据。

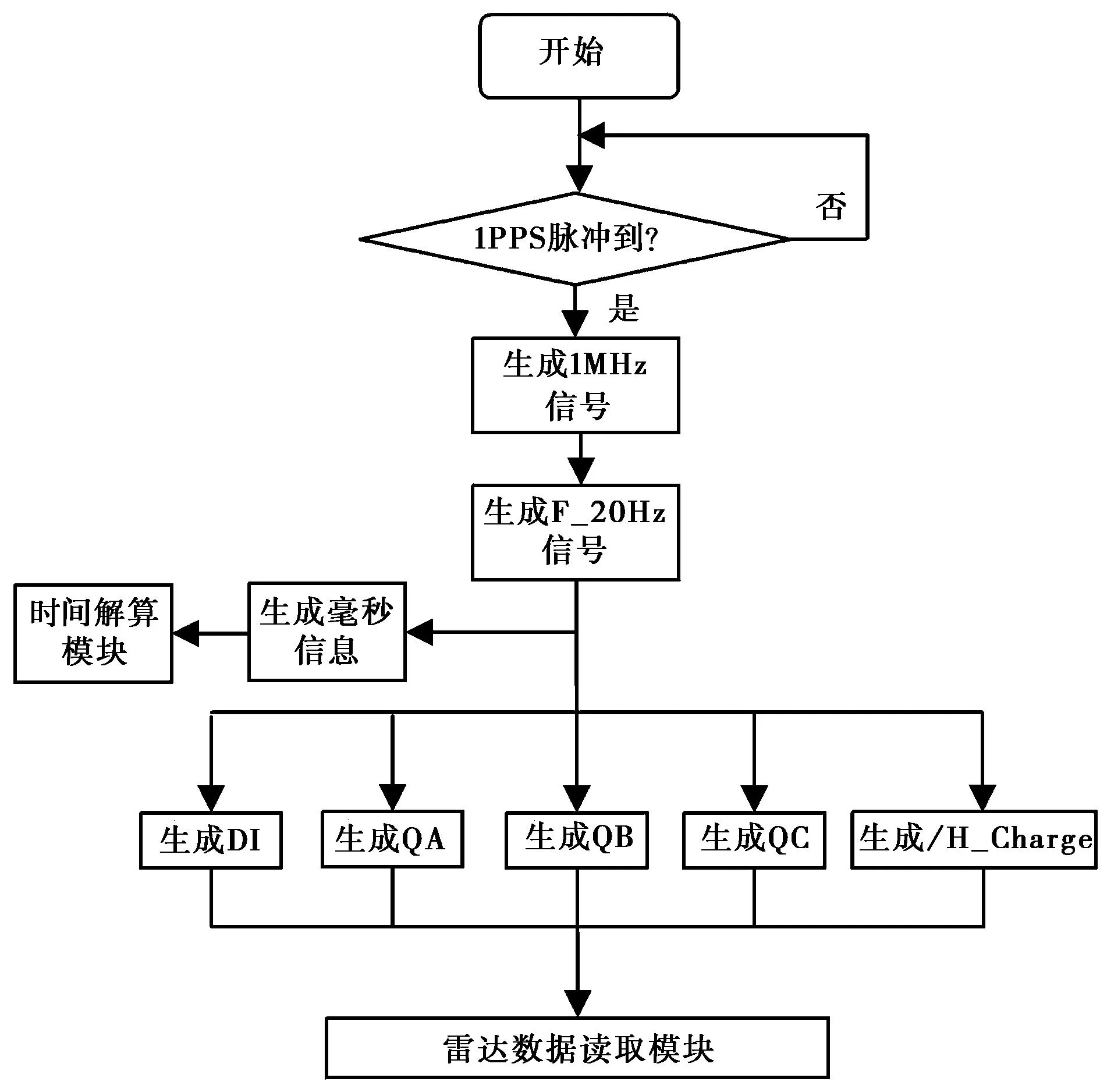

时序信号生成由timeing_generator_module模块负责,图2所示中UM220输出的1 PPS信号的同步下产生雷达系统工作所需的时序信号,如1 MHz、信息请求DI、信息性质码QBQCQD、加载脉冲/H_Charge等,测距系统、角编码系统在这些信号的控制下将数据准备好,并放置在12位总线上,雷达工作状态标志信息放在专用线上。接下来在加载脉冲/H_Charge的下降沿时刻,FPGA数据控制模块读取总线和专线上的数据,完成一个采样周期数据读取工作。

各时序信号的时间间隔有严格要求,以保证其他系统的电路有足够时间进行处理,北斗模块输出的1 PPS是所有信号的时间基准,依靠UM220高精度的1 PPS信号,可以将时序信号精度控制在1 μs以内。时序信号生成模块工作流程图如图4所示。

图4 时序信号模块工作流程图

在对各模块进行设计编译之后采用 Quartus II 自带的仿真器对各模块进行仿真验证,确认输出满足要求后,再将各模块进行组合,实现仿真输出结果验证。最终输出的时序信号,满足雷达时序信号要求。

正确实现时序信号后,就可以进行后续的模块开发了。我们在此基础上开发了雷达数据读取模块、模拟数据生成模块和数据发送模块,实现了项目预定目标。

4关键技术

设计的关键技术有两点,一是时间信息与1 PPS脉冲对齐,UM220输出的$BDGGA消息要滞后于1 PPS信号约60 ms至90 ms不等,如果以收到$BDGGA并解算出时分秒信息的时刻为当前秒的起点,将导致数据与北斗时误差数十毫秒,反之,如果以1 PPS作为当前秒的起点,由此产生的0 ms与1 PPS沿对齐,但在接下来的数十毫秒内,新的$BDGGA消息还没到来,造成每个0 ms和50 ms时刻的时间都是错误的,因此,必须进行修正。方法是1) 1 PPS信号为整数秒起点,修正1 PPS与$BDGGA到达时刻之间的秒信息。2) 确保时序关系正确,如果直接按照原系统的时序关系进行设计,无法正确读取雷达数据,经过测试,原系统采用分立元器件设计,时序信号存在比较大的抖动,解决办法是先通过1 PPS同步产生1 MHz信号,再用1 MHz信号去同步产生其他时序信号,调整信号的延迟和脉宽,有效解决了上述问题。

5结束语

本设计采用北斗导航模块提供的时间信息和1 PPS信息,在FPGA的控制下实现了时间信息读取和时序信号设计,解决了时间对齐、时序不稳定的问题,通过时序仿真和分析验证,表明此方法满足系统对较高时间精度的要求,最终应用在雷达接口改造中。基于FPGA的设计也使系统实现了小型化的目标,提高了系统稳定性,并使维护和升级更加方便。

参考文献

[1] 和芯星通.Unicore protocol specification UM220-HB_Ed10.1[S].2013.

[2] 和芯星通.UM220数据接口协议[OL]http://www.unicorecomm.com.

[3] Altera Corporation. Cyclone IV device handbook, volume 1[R].2011.

江良剑(1978-),男,福建永定人,工程师,主要从事导航定位系统、雷达测量研究。

熊善泉(1980-),男,湖北公安人,工程师,主要从事导航定位系统研究。

焦海松(1973-),男,河南林州人,高级工程师,主要从事导航定位系统研究。

周志全(1978-),男,河南安阳人,工程师,主要从事雷达测量研究。

The Method of Radar Interface Time Sequence

Design Based on Beidou Timing

JIANG Liangjian,XIONG Shanquan,JIAO Haisong,ZHOU Zhiquan

(LuoyangElectronicEquipmentTestCenterofChina,Luoyang471003,China)

Key words: Beidou timing; 1 PPS; timing signal