CMOS运算放大器失调电压消除设计

2015-12-20肖本,肖明

肖 本,肖 明

(1.广东机电职业技术学院电气学院,广东广州 510051;2.深圳芯卓微科技有限公司,广东深圳 518100)

高精度ADC、DAC以及滤波电路中运算放大器的电压失调问题已经成为了一个处理的难点。一方面失调电压直接影响数模或者模数转换器的精度,另一方面失调电压通常又无法避免。运算放大器电压失调包括系统失调电压和随机性失调电压。通常采用Bipolar工艺设计的运算放大器,其失调电压都够达到比较理想的效果,但是采用Bipolar工艺成本高、功耗大,在实际应用中很少采用。当今主流CMOS工艺集成度高、版图面积小、成本低、而且功耗也低,但CMOS工艺设计出的运算放大器,如果不进行特殊处理,其失调电压通常达到10 mV以上。本文提出了一种新颖的CMOS运算放大器失调电压降低技术,对电路进行了仿真验证,并进行流片测试。

1 工作原理和电路设计

1.1 运算放大器失调电压产生机理

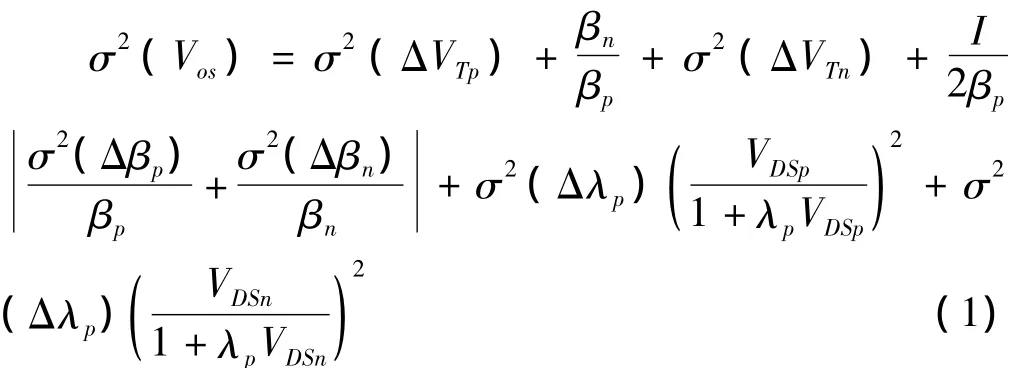

放大器的失调电压主要由两部分组成:随机失调电压与系统失调电压。随机失调电压主要由本应匹配的器件在制造过程中的工艺的缺陷造成不匹配,或由本应匹配的器件在工作过程中受到不同影响而引起;系统失调电压主要由输入级或有源负载M O S管的漏极电压的不同造成。低失调电压放大器通常使用大尺寸输入管和大尺寸有源负载管,其目的是为了得到更好的匹配性,从而降低放大器的随机失调。而系统的失调则需要从电路结构上进行解决。式(1)为放大器的失调电压的定量分析公式,参照图1可知:βp与βn分别是PMOS与NMOS的跨导参数,I是偏置电流,σ2(ΔVTp)为 PMOS的阈值电压的方差,σ2(ΔVTn)是NMOS的阈值电压的方差

式中,σ2(Δβp)是 PMOS的跨导方差;σ2(Δβn)是NMOS镜像电流源的跨导方差;σ2(Δλp)是PMOS的沟道长度调制系数的方差;σ2(Δλn)是NMOS的沟道长度调制系数的方差;VDSp是输入PMOS的VDS;VDSn是电流镜的NMOS的VDS。从式(1)中可看出,若降低偏置电流I,第3项将减小,但降低偏置电流在提供足够的开环增益和降低功耗的情况下,运算放大器的转换速率将受到影响。对于第2项,通过增大电流镜NMOS的沟道长度以降低λ的影响,对于σ2(ΔVTp),通过版图Layout的对称可有效降低其大小,所以系统失调电压主要原因产生在输入级PMOS的ΔVDS。

1.2 传统运算放大器抑制失调

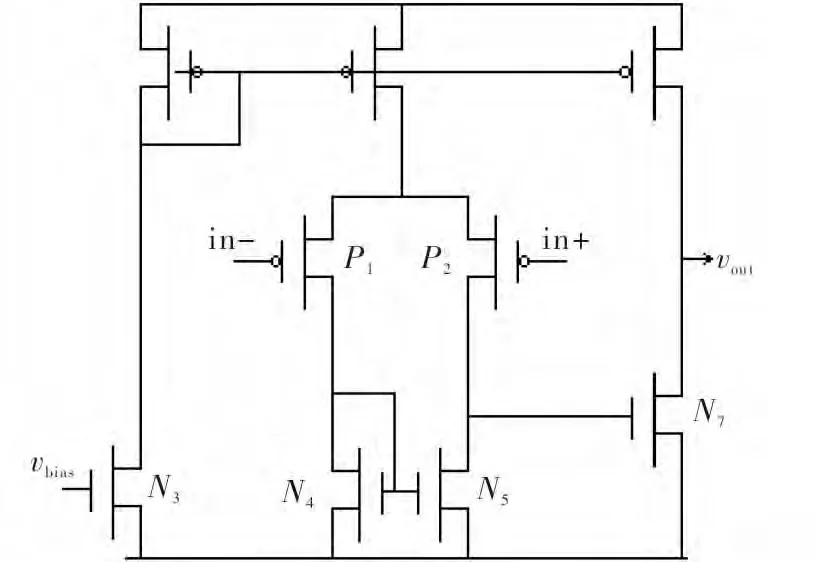

图1为基本CMOS两级放大器,尽管输入的差分对(P1,P2)与有源负载(N1,N2)可做到较大的尺寸,以最大程度达到匹配,从而减小随机失调,但该结构放大器的失调电压仍然较大,因为OP的有源负载N1、N2接法的不同造成OP在正常的工作的情况下,Vds(N1)≠Vds(N2),从而产生较大的系统失调,但此电路的好处是增益较大。

图1 CMOS两级放大器

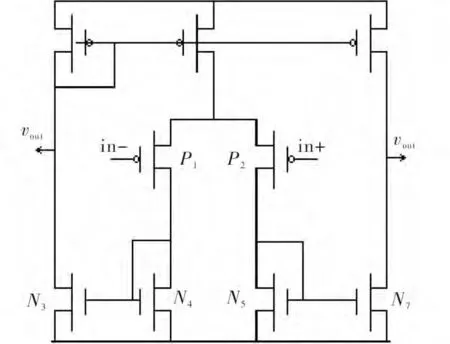

图2为全差分输入结构的放大器,此结构比两极放大器能更有效地抑制电路的系统失调。因为N4与N5均为二极管的接法,在电路工作在放大区时,Vds(N1)≈Vds(N2),从而有效避免了系统失调。但该结构的最大弊端是电路的开环增益相对较小。因此,该结构放大器的应用范围受到较大局限。

图2 全差分输入结构的放大器

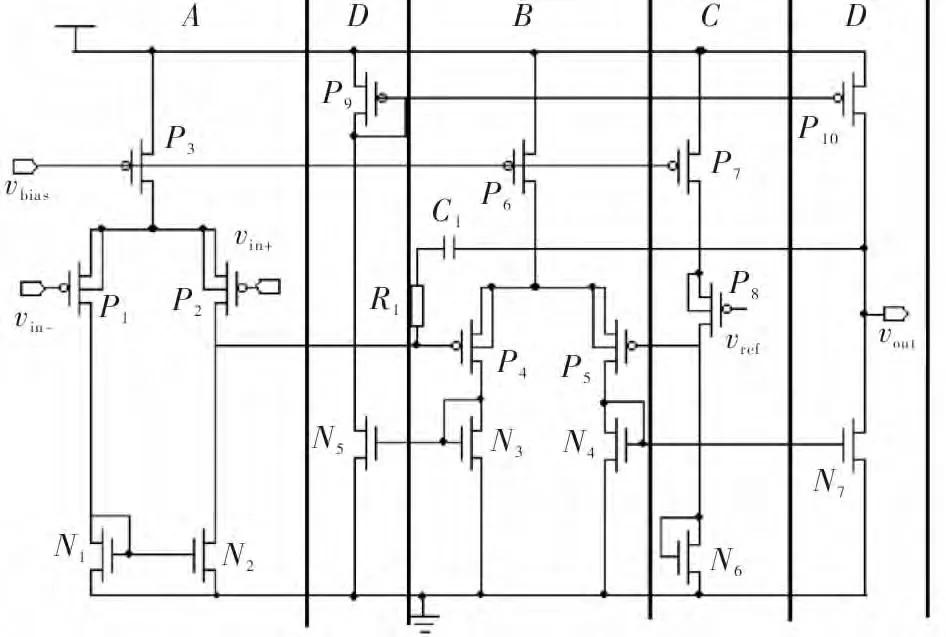

根据上述的两种结构的优缺点,提出新的电路结构,应用第一种结构的较大增益、用第二种结构减小失调来构成一种结构,可以达到较大的增益与较小的失调。电路结构如图3所示。

图3 低失调运算放大器

2 电路原理

2.1 电路结构

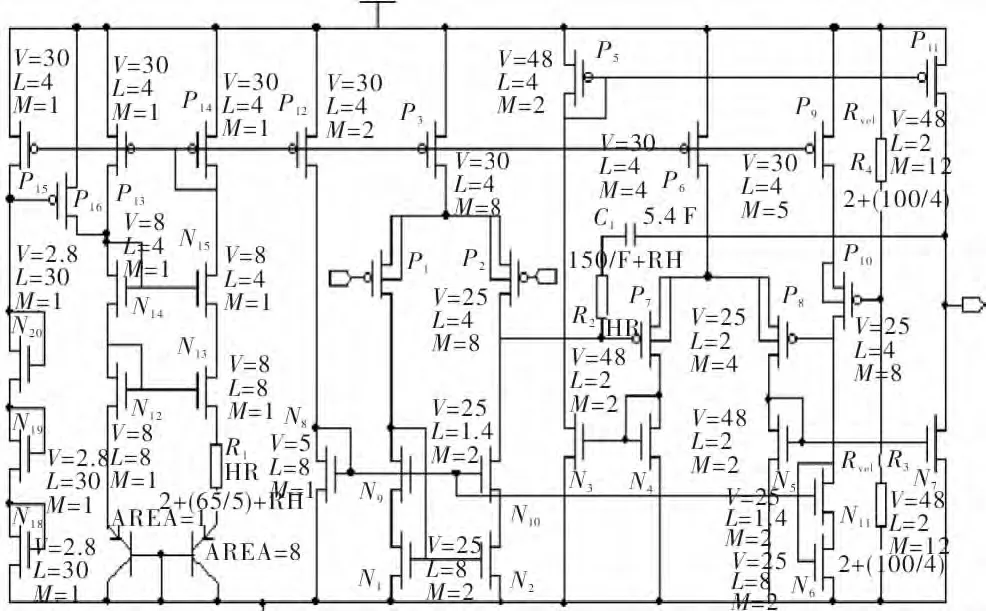

由图3可知,放大器电路可以划分为:差分输入级、对称放大级和CLASS—AB输出级3部分。图3的A 部分由 P1、P2、P3、N1、N2组成电路输入级,其中 P2、P1分别为放大器的正负极输入管,N1、N2为差分对的有源负载,P3为尾电流源,此部分的输出信号送入第二级的对称放大级。电路的B,C部分与第一级OP输出的信号构成对称放大级,目的用PMOS(P4、P5、P6、P7、P8)与 NMOS(N3、N4、N6)产生一个信号与第一级的输出对称。与第一级的输出对称的信号产生由C部分(P7、P8、N6)产生,为达到对称,C部分各管尺寸和结构与第一级基本放大器的左侧相同(P7=1/2P3),P8的栅极接入vref,可根据放大器的用途接入不同的电压,以达到对称。B部分为全差分结构,输入的信号分别为第一级的输出与用来对称的信号。电路中D 部分为 CLASS—AB 输出级,由 N5、N7、P9、P10构成,其中P10、N7为输出管子,其尺寸大小由典型应用中输出负载的大小决定。此外电阻R1与电容C1串联为放大器的补偿电路,采用传统的密勒补偿。

2.2 电路参数设计

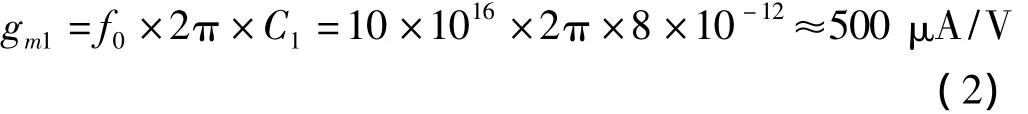

输入晶体管尺寸确定。根据设计要求,单位增益带宽为8 MHz,同时在计算过程当中应留有余量,取10 MHz,设定补偿电容C1的大小为8 pF,则

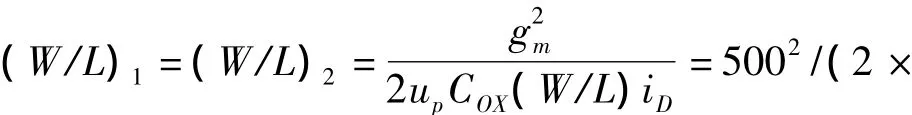

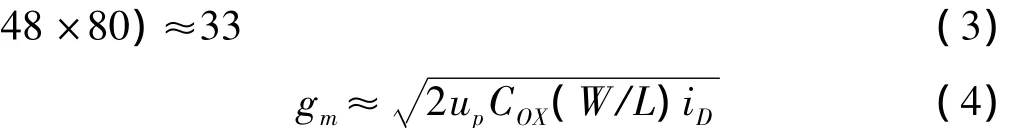

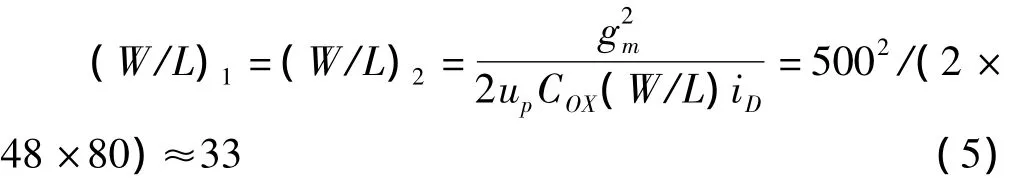

输出晶体管尺寸确定

因此

2.3 整体电路参数和版图布局

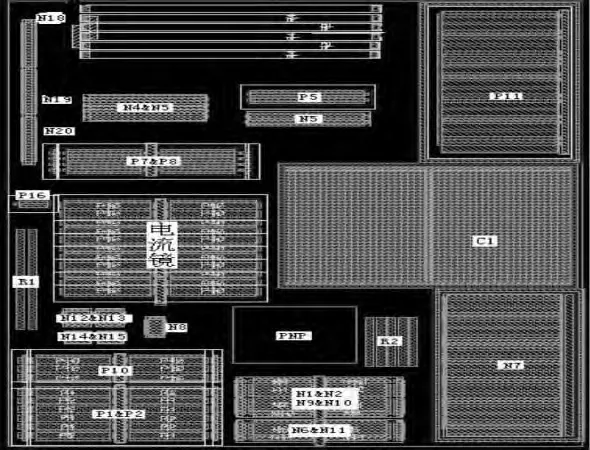

考虑偏置电路后的完整低失调运算放大器电路如图4所示。由于从电路的结构来说,电路只能抑制系统失调的产生,而不能抑制电路的随机失调的产生。通过对失调产生原理的分析,电路的随机失调主要由本应该对称匹配的器件,但是在工艺实施的过程中,因为工艺的偏差,引起不匹配,造成较大失调电压的产生。还有一种失调就是版图的不合理的布局,造成了在实际当中电路相互之间的干扰较大,从而产生了电路的失调电压。由于此次设计的特殊性决定了Layout的特殊性。作为电路的输入差分对P1、P2,其对称性直接影响到电路的失调电压,应采取特殊处理:P1、P2采用交叉画法,为进一步减小输入的随机失调,在每个管子的边缘加Dummy管,减小在制作过程中边缘受光刻的影响。在Layout时,边缘Dummy管的源漏接所在井的井电位。由失调电压的产生机理分析可知,有源负载 N1、N2、N9、N10对失调的影响较大,所以同样采用特殊处理。电路整体版图如图5所示。

图4 整体电路

图5 版图

3 仿真与测试结果

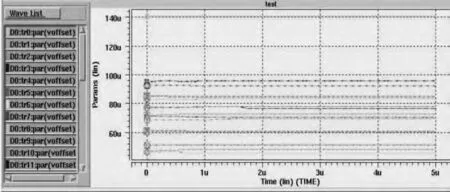

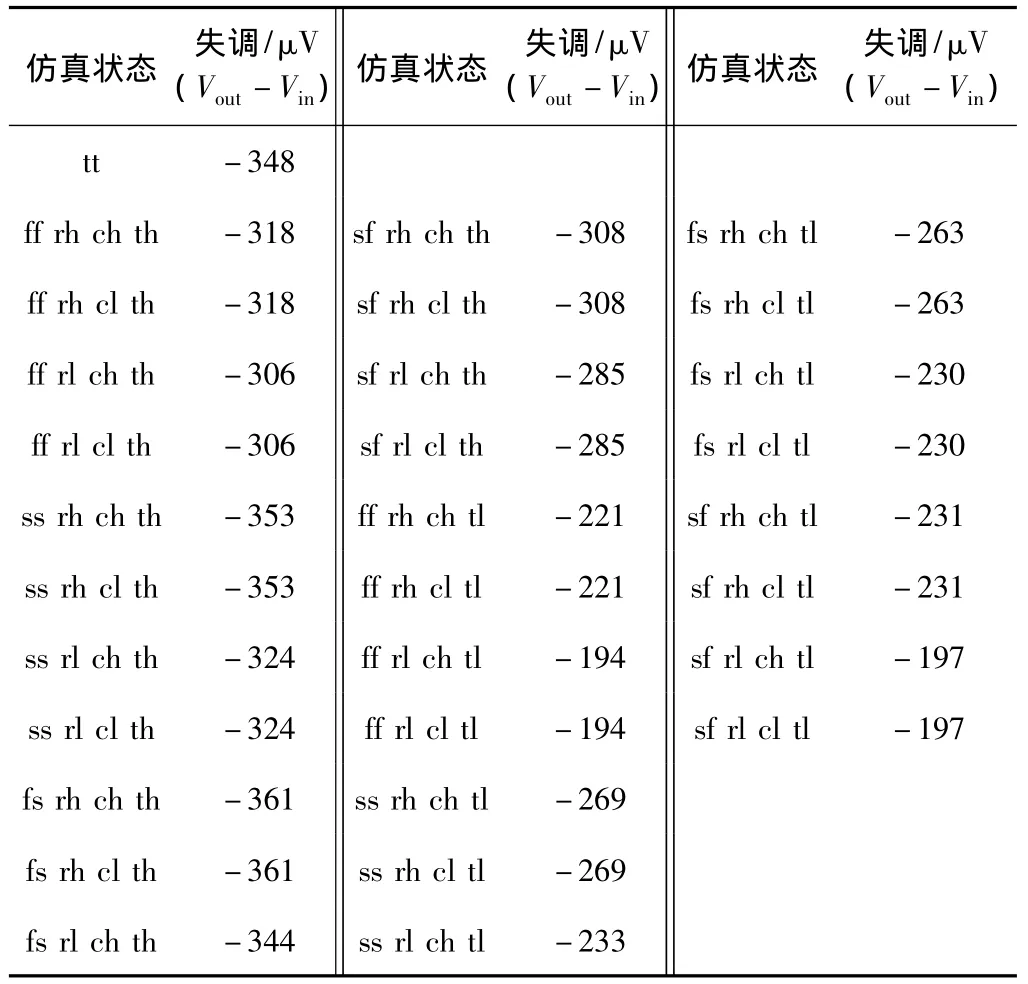

输入失调电压仿真,计算机只能仿真系统失调电压,而随机性失调电压则无法有效模拟。通常情况下,高性能运算放大器系统失调电压占芯片实际总失调电压约10%。系统失调电压仿真条件为电源电压9 V,测试输入电压为4.5 V,空载,温度-20~120℃。仿真结果如图6所示。从统计结果来看,最大失调电压为140μV,最小失调电压为20μV。负载为100 pF电容和10 kΩ电阻,不同工艺情况下系统失调电压的仿真结果如表1所示。

图6 仿真结果

表1 不同工艺情况下系统失调电压仿真结果

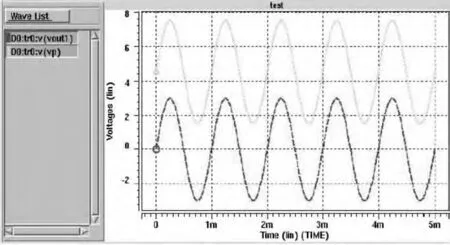

输入输出测试动态测试,图7为输入为1 kHz,3 V正弦波的输出波形。从结果可知,输出可较好地跟随输入,无输出失真。

图7 1 kHz,3 V的正弦波输出波形

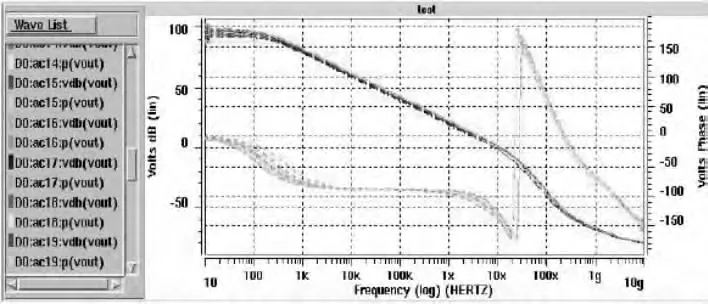

图8为电源电压9 V,负载为100 pF电容和10 kΩ电阻,温度为-20~80℃时,电路的增益、带宽和相位裕度的仿真结果波形。电路的平均增益97.4 dB,平均带宽10.4 MHz,相位裕度为50°。

图8 电路的增益、带宽和相位裕度的仿真波形

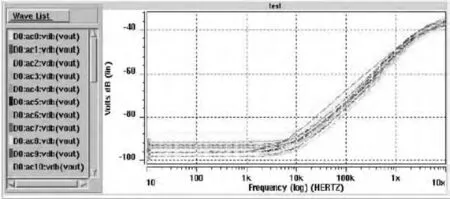

图9为电路在-20~80℃温度下的PSRR的仿真结果波形,电路的PSRR较高,全部超过-87 dB。

图9 不同温度下的PSRR的仿真波形

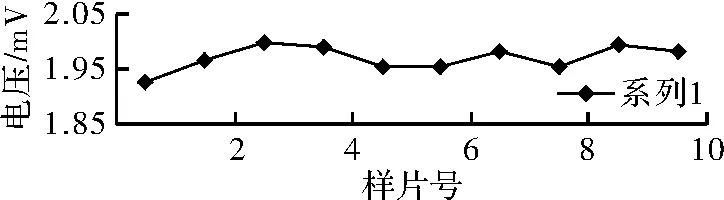

随机抽取10颗样片进行测试,编号为1~10,分别进行失调电压测试和直流开环增益测试。

测试1 电源电压9 V,测试输入电压为4.5 V。失调电压测试统计结果如图10所示。最大失调电压为2 mV。测试中失调电压为实际失调电压,其包括两部分:一部分为系统失调电压;另一部分为随机失调电压。对比前文图6仿真的系统失调电压结果,系统失调电压只占到芯片总失调电压约10%,符合经验情况。

图10 失调电压统计

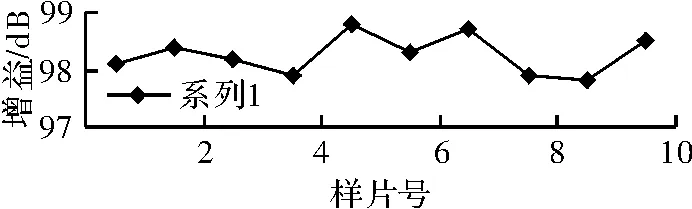

测试2 对10颗样片分别进行开环增益测试,负载为100 pF电容和10 kΩ电阻,测试统计结果如图11所示,平均增益达98 dB以上。对比图8系统仿真的平均增益97.4 dB,二者结果吻合。

图11 增益统计

4 结束语

基于直流对称偏置技术,采用CMOS工艺技术设计了一种低失调电压的高性能运算放大器。系统开环增益达98 dB,单位增益带宽为10.4 MHz,相位裕度为50°,电源抑制比<-87 dB。通过样片随机测试,平均失调电压<2 mV。测试结果表明,设计的运算放大器失调电压小、一致性高,能较好地满足各种高性能电路的需求。

[1]Chan P K,Siek L,Tay H C,et al.A low - offset class-abcmos operational amplifier[C].IEEE International Symposium onCircuits and Systems,2000.

[2]Plant Science Innovation Center.United states patrnt application publication pub,US2004/0145413[P].USA:Plant Science Innovation Center,2004.

[3]Grayp R,Meyer R G.MOSoperational amplifier design -atutorial overview[J].IEEE Journal of Solid - state Circuits,1982,17(6):969 -982.

[4]Roubik Gregorian.Introduction of CMOSop amp and comparator[J].IEEE Transactions on Circuits,2009(6):113 -119.

[5]Gabriel A.Voltage references from diodes to precision high -order bandgap circuits[M].New York:Wiley - Interscience,2002.

[6]Anton Pletersek.A compensated bandgap voltage reference with sub-1 - v supply voltage Springer[J].Analog Intergrated Circuit and Signal Processing,2005,44(1):5 -15.

[7]薛庆华,周玉梅.一种高性能CMOS能隙电压参考源的设计[J].微电子学与计算机,2003(10):38-40.

[8]薛超耀,韩志超,欧健,等.一种恒跨导轨对轨CMOS运算放大器的设计[J].电子科技,2013,26(9):121 -123,130.