基于FPGA的振动监测系统设计与实现

2015-12-14韩旗,蔡萍

韩 旗,蔡 萍

(1.海军驻上海七〇四所军事代表室,上海 200031;2.上海交通大学,上海 200240)

基于FPGA的振动监测系统设计与实现

韩 旗1,蔡 萍2

(1.海军驻上海七〇四所军事代表室,上海 200031;2.上海交通大学,上海 200240)

针对长时间持续监控设备或结构振动的需求,基于FPGA技术构建了一个多通道振动监测系统,论文详细介绍了监测系统的硬件构成,FPGA的固件设计及基于USB接口的数据传输的实现。系统已在实际工况下运行,可靠性良好,并具有良好的可扩展性。

振动监测;FPGA;flash存储;USB传输

0 引言

振动和噪声对仪器设备和人体生理或心理产生的影响愈来愈受到重视。船舶航行时产生的噪声和振动会给船上设备仪器的正常运行和乘员的舒适性带来影响;大型工业设备的振动噪声不仅影响操作工人的听力,严重时甚至导致心血管系统和消化系统的疾病;铁/轻轨/高架公路等设施的振动则会严重影响周围居民的日常生活。

为了对结构进行减振设计或进行客观定量的环境振动噪声评估,需要对振动进行长期的数据采集。对于长期监测、无人值守且电磁环境恶劣的使用环境,需要设计一种具有高可靠性的振动监测系统进行数据采集和数据保存。普遍采用的单片机或其它基于程序运行机制工作的控制器抗电磁干扰较差、长期稳定性不能保证。为此,本文提出了一种基于FPGA的三轴振动监测系统方案,并进行了实现。

1 系统构成

环境振动测量通常需要实现多点或多轴的振动数据采集[1],要求系统能够在无人监守的情况下长期稳定工作。长时间监测要求系统具有较大的数据存储容量,并提供时间指针。FPGA通过硬件实现所需功能,具有各模块独立运行、并行处理数据、方便扩展、无中断等待,以及进程互相干扰等特性,非常适合于电磁环境恶劣、需要长期稳定运行的场合。

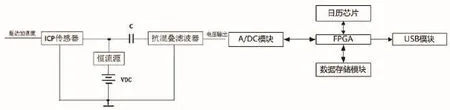

本设计兼顾成本和速度,选用了Altera公司的EP3C16芯片作为控制器。作为cyclone系列的中端产品,EP3C16的运行速度最高可达50M/s,片内RAM 516Kbits,逻辑单元15K,满足多路振动数据采集系统数据缓存和对模数转换芯片、时钟芯片和数据存储芯片等的操作要求,系统构成如图1所示。

图1 通用振动监测系统构成

ICP(Integrated Circuit Piezoelectric)传感器为内置集成电路的压电式振动加速度传感器。内置的集成电路将原来的高阻抗输出转换为低阻抗输出,从而大大提高了系统的抗干扰能力。ICP传感器由恒流源供电,其输出电压的交流分量与振动加速度成正比,通过隔直电容C输出到抗混叠滤波器。抗混叠滤波器用于滤除高于 1/2采样频率的频谱成分,以避免采样信号混叠[2]。通过FPGA控制对振动信号进行多通道高速采样,并读取时间信息,保存于NAND flash芯片中。定期将保存的数据通过USB协议进行数据转存。

A/DC芯片AD7656具有高达250K/s的采样率,16bit分辨力,能够同时对6路输入信号进行采样;数据存储模块H27UBG8T2BTR具有复用的8位数据总线和地址总线,存储容量4GB,FPGA通过I2C与日历芯片 PCF8563接口,获得时间指针。通过USB接口芯片CY7C68013A将数据传输到上位机进行数据分析。

2 固件设计

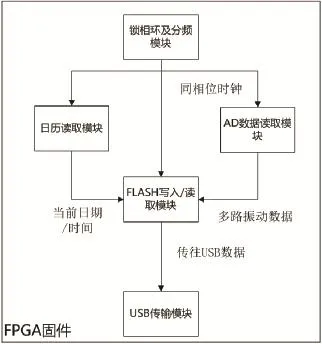

FPGA内部的程序以VHDL语言进行编写,通过模块化设计,使各项任务并行、独立运行。固件设计各模块如图2所示。

系统使用50M的外部时钟,通过FPGA内部锁相环电路保证时钟信号相位一致,通过分频获得各个模块需要的时钟频率;日历读取模块通过普通IO口模拟100KHz的I2C协议,实现对日期的读取;A/DC数据读取模块在振动数据采集时驱动AD7656芯片采样于10KHz下工作,而在休眠及数据传输模式时自动休眠,等待时钟唤醒。flash写入/读取模块根据工作模式的设定[4],分别启动对应模块,获得数据后存储入flash或者读取flash数据后传输到USB传输模块。以下按照模块分别进行介绍。

1)日历读取模块

PCF8563在 I2C总线上的器件写入从地址为0xA2 H,读取从地址为0xA3 H,其02h至08h子寄存器分别存储从秒到年7段BCD码时间信息,在系统掉电情况下通过电池供电,正常上电时则由电源供电以保证时间信息的完整。

图2 FPGA固件模块

该模块以正常IO口模拟I2c接口,由定时器触发后从子寄存器中依序读回秒/分钟/小时/日/月/年信息,传递到存储模块中,用于标识此次数据测量开始的时间。

2)A/DC数据读取模块

系统使用的AD7656由管脚Convert上升沿触发采样,经过转换时间Tconv后芯片busy管脚由高电平拉低,而后读取模块选中AD芯片片选信号,对读取管脚(rd)输入下降沿时AD芯片的数据输出口逐通道输出采样通道1~6的信号。该模块的仿真时序输出如图3所示。

图3 AD数据读取模块输出仿真

3)flash写入/读取模块

flash模块到FPGA的IO口定义及其到flash芯片的连接如图4所示。

flash芯片 H27UBG8T2BTR 通过管脚addr/data[7..0]复用 8位的地址总线/命令总线/数据总线,因此在读写过程中均需要较为严格的时序要求。在管脚的上升沿,根据ALE/CLE这两个管脚的高电平,8位总线上的数据写入flash芯片的地址寄存器/命令寄存器;在写入寄存器过程中管脚表明芯片当前是否处于可操作状态,在操作时需要检查其为低电平时方可进行下一步操作,避免命令字同地址/数据的混淆,这将导致后续数据出现大面积的失效。在寻址过程中,共需要5个数据周期来完成地址的输入。

在系统设计中,单次采集三路16位数据,合计48位,而日历数据经过处理后长度也为48位,为了数据地址的连续性,使用每个page中的前8190个字节,共计存储1365组数据(或日历),而芯片能够存储1365*256*2048组数据。

H27UBG8T2BTR芯片在上电过程中默认被设置为读取页面模式,以避免在上电时电压的波动造成不可预计的擦除和写入操作;因此在擦除和写入模式下,需要发送FF h重置命令字以重置运行模式。

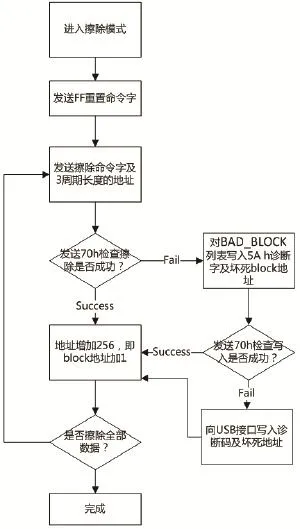

读写H27UBG8T2BTR的流程通过VHDL的状态机实现,该有限状态机的输出基于当前状态及当前输入情况确定。对FLASH芯片的操作有三种工作模式,在上电初始化时读取IO口信息确定,分别如下所示:

1)擦除flash:flash擦除页面原有数据后,使页面内所有数据位均为‘1’后方能进行写入,且一次写入后必须擦除后方能重写。擦除flash的状态机如图5所示,从block 0开始擦除,由于芯片存在坏死的存储块,这些存储块在擦除过程中无法被全部重置为‘1’状态,需要对坏死存储块进行检查并记录。芯片由硬件保证第一个存储块必定是完好的,故而在存储块0上建立坏死存储块列表。在擦除过程中设计了USB诊断功能,可以通过系统设计的USB接口获得芯片中的坏死存储块地址。

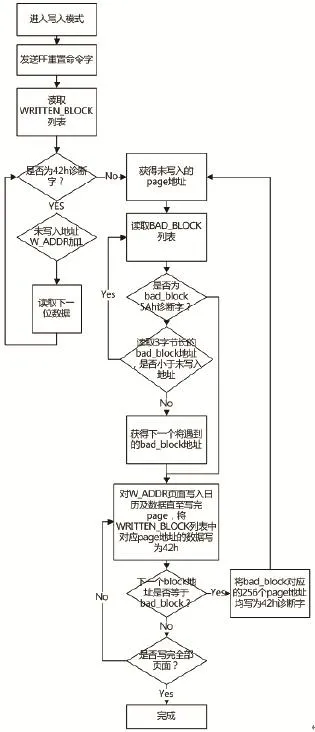

2)将日期信息和A/DC数据写入flash;写入flash状态机如图6所示,在上电后需要读取坏死存储块列表,避免在坏死存储块上写入引起的数据丢失问题,同时为避免重复写入已使用的存储块,在存储块0上建立已写存储块列表,存储写过的页面地址及存储块地址。在上电过程中,读取已写存储块列表直至数据为未写入状态,即可获知未使用页面地址。当写入地址达到坏死存储块时,将该存储块内的256个页面地址标记为已写存储块列表中,而后读取下一个坏死存储块地址,继续数据记录。

3)读取数据,并传输到USB传输模块读取数据及传输状态机,则读取已写存储块及坏死存储块列表,将有效页面内数据全部传输到USB模块的缓冲区内,经USB传输到电脑。

图5 擦除FLASH状态机图

图6 写入状态机

图7 USB模块仿真输出

4)USB传输模块

用于实现USB传输的CYTC68013芯片是一个带增强型MCS51内核和USB接口的单片机,完全遵从USB2.0协议,可提供高达480Mbps的传输率;内部集成锁相环,最高可使51内核工作在48MHz;对外提供两个串口,可以方便地与外部通信;片内拥有8KB的RAM,可完全满足系统每次传输数据的需要。本系统中,CY7C68013A芯片工作于异步时钟SLAVE FIFO模式[5],该芯片内部使用内嵌的FX2微处理器来实现USB协议层的配置,FPGA通过8位数据线与芯片内部的FIFO连接。本系统中,令芯片内部的4KB FIFO全部用于上传振动数据。USB传输模块仿真输出如图7所示,检查CY7C68013A片上FIFO未满的标志管脚后将需传输的数据传递到数据总线上,以上升沿触发SLWR管脚将数据写入FIFO,而后由FX2处理器将数据传输至上位机。

3 结束语

本研究实现的基于FPGA的三轴振动监测系统能够对六路信号以 10Ksamples/second进行同步采样,在偶发的掉电情况下能够正常恢复工作,继续记录振动信号。作为存储媒介的NAND FLASH能够保证数据有效性,采集完成后通过USB 2.0接口将数据传输到上位机,进行后续分析。使用结果表明本系统具有在电磁干扰环境下长期稳定工作的能力,适用于对各种结构和设备的振动进行长期监测的场合。

[1]阎洁.基于DSP和CPLD的船舶振动监测系统的研究[D].天津大学,2005.

[2]宗赤.基于加速度传感器的船舶振动检测系统设计[J].电子产品世界,2011(4):46-47.

[3]李海鸿,朱元清,陈蓓.实时时钟芯片 PCF8563及其应用[J].国外电子测量技术,2002(5):29-31.

[4]李庆诚,孙明达.基于NAND型闪存的嵌入式文件系统设计[J].计算机应用研究,2006(4):231-233+239.

[5]扈啸,张玘,张连超.USB2.0控制器CY7C68013特点与应用[J].单片机与嵌入式系统应用,2002(10):48-50+54.

Design and Realization of Vibration Monitoring System Based on FPGA

Han Qi1,Cai Ping2

(1.Navy Representation Office at No.704 Research Institute,Shanghai 200031,China; 2.Shanghai Jiao Tong University,Shanghai 200240,China)

In order to monitor the environment vibration in a long period of time,a vibration monitoring system with multi-channel based on FPGA technology is developed.The hardware implement is introduced in detail.The firmware design and the data transmission via USB are realized.The monitoring system has already been in use in the real field and has satisfied reliability as well as good expansibility.

vibration monitoring; FPGA; flash storing; USB transmitting

U665.13

A DOIⅹ10.14141/j.31-1981.2015.06.011

韩旗(1970-)男,硕士,高级工程师,研究方向:船舶机电设备。