基于FPGA的高标清数字光端机的研究

2015-12-02杨红军洪三其

杨红军,洪三其

YANG Hong-jun, HONG San-qi

(武汉轻工大学 机械工程学院,武汉 430023)

0 引言

随着社会的进步及科技的发展,人们对于安防监控的需求越来越高,传统的模拟标清视频技术由于图像质量差、分辨率低等缺陷已不能满足社会的需求,但由于该类设备还占有大量市场,因此,对原有设备进行改造,使同轴电缆中同时可传输模拟标清和高清视频信号成为当前研究的重点。本文从低成本的观念出发,设计了一种基于FPGA的数字光端机,可以将多路低速并行数字信号复用到一路高速串行数字信号中,并通过光纤实现千兆速率高速传输,在交通、治安管理,家庭、小区、学校安全防范,远程视频会议、远程教育等领域具有广泛的应用前景。

1 光端机的系统结构

根据视频信号的采集到最后视频信号的还原输出数据流的传输过程,光端机的硬件系统结构如图1所示。

视频信号先通过模拟缓冲模块对信号进行补偿、滤波,增强信号的驱动能力,然后通过模数转换后输入到FPGA构成的光端机信号发送模块,经过处理后,然后由通过光模块传输到光端机的接收端,其接收端同样由FGPA芯片构成,通过处理后的信号经过数模转换后经驱动输出给终端显示装置,还原成高清或标清视频。

2 硬件电路的设计及元件选型

图1 光端机的组成结构

2.1 模数转换(ADC)及数模转换(DAC)模块

本系统设计了的数字光端机可以同时采集及传输多路视频信号,这里以四路信号为例。通常安防领域的同轴技术类型标清视频信号及高清视频信号峰峰值最大为1Vp-p,模拟调制带宽标清最高20MHz,高清最高40MHz,本系统可同时处理高标清信号,因此模数转换装置ADC的输入模拟调制带宽应至少在40MHz以上,依据采样定理可知ADC的采样频率至少为80MHz及以上,为便于计算,设计ADC采样频率选择90MHz,根据经验设置采样精度8bit。那么每信道数据为720Mbps,四个信道数据为2880Mbps。通过主控芯片FPGA的串行化数据组装,则传输数据为2880Mbps,设置FPGA信道带宽为3G(因为其中包含帧头数据及串口通讯等数据)。在光端机接收端,信号分离后,每信道720Mbps数据不变,DAC转换速率为90MHz,精度8bit。

据此,ADC 选用ADI公司的AD9057BRS-60型号ADC,其采样率最高兼容60MSPS,内置2.5V电压参考,设有跟踪和保持电路,兼容TTL/CMOS输入,单一5V供电,精度为8bit[1]。每个信道采用两片ADC进行采样。设定每个ADC采样时钟45MHz,并以间隔180°的时钟相位差进行采样,以降低成本。DAC选用AD公司的AD9114数模转换器,分辨率8bit,输出形式为4mA~20mA的差分电流,因此需要在输出引脚之间接50Ω 的电阻,转为以电压信号输出。

2.2 FPGA模块硬件电路设计

本设计选择ALTERA公司的FPGA Cyclone IV系列EP4CGX30CF23I7NGX作为主处理器,完成整个系统的调度以及信号处理等。EP4CGX30提供高达八个3.125Gbps高速收发器,具有6K到150K的逻辑单元,6.3Mb的嵌入式存储器,小于1.5W的总功耗,工作温度为-40°C~100°C,484-BGA封装,具有Serdes模块及CDR单元,电源电压为1.16V~1.24V[2]。

2.2.1 发送端FPGA模块设计

选择FPGA的BANK7 I/O口作为输入口数据通道,接收ADC传输的数据,其模块接口设计如图2所示。

图2 FPGA ADC模块接口设计

发送端FPGA发射光信号接口设计如图3所示。

Serdes模块支持信号传输速率达3.15Gbps,输出信号电平为PCML电平。在输出端设计交流电容,使FPGA的差分PCML信号与光模块进行AC耦合。并在靠近发送方在两条差分传输线上并联电阻,实现信号链路的阻抗匹配,防止信号反射。

光端机接收端FPGA的DAC接口及光链路接口与发送端FPGA接口设计方法类似,这里不再描述。

2.2.2 FPGA的485控制数据模块

图3 发送端光模块信号输出接口

在FPGA的反向低速传输过程中,RS485控制数据量相对较少,设计传输速率为150Mbps。由于FPGA中的Serdes模块支持的最低信号输出速率为600Mbps。这里需通过对FPGA一个BANK进行编写,在信号接收处理后的输出转化为LVDS差分输出,并配置I/O电平为2.5V,如图4所示。

图4 FPGA 485信号传输接口设计

如图4所示,其中R1和R2为LVDS的输出匹配电阻,C1和C2为交流耦合电容,同时2.5V的电源及分压电阻给LVDS提供输出的电压偏置。

2.2.3 FPGA时钟域及同源时钟设计

FPGA对数据的处理过程如图5所示。

从图中可以看出,FPGA系统逻辑工作的时钟信号采用常用频点24.75MHz,由外部晶振直接提供。Serdes时钟信号为150MHz。ADC时钟信号为45MHz,这里的45MHz的时钟信号,一个是PLL2电路倍频的45MHz时钟信号提供给ADC1/2/3/4,另外一个相位差180°的时钟信号是通过PLL2内部电路进行设置后将反向的45MHz的时钟信号提供给ADC5/6/7/8。

图5 FPGA的工作过程

在光接收机接收数据时,利用FPGA器件Serdes模块中CDR单元,通过接收的数据流恢复数据的时钟信号,并通过锁相环电路后,发送给接收数据,解帧、解串。这就实现了整条数据链路上的同一时钟配置,解决数据传输中的数据的延迟、堵塞或者放空[3]。

2.3 其他硬件模块

2.3.1 光模块硬件设计

在本文的光端机视频信号传输中,正向视频信号数据传输3Gbps,反向控制数据传输为150Mbps,因此光模块选用奥雷光电公司的上下非对称速率光收发一体模块ATR-B41XX,发送速率可达3Gbps,接收速率为350Mbps,节省资源。ATR-B41XX采用单一3.3V电压供电,LVDS差分检测输出[6]。这里发送端选用传输距离为20km,工作温度-20℃~70℃的ATR-B4127,接收端光模块为配对使用的ATR-B4127[4]。

2.3.2 运放模块

选用Burr-Brown公司的OPA2345,OPA2345是一个具有双通道轨到轨输入与输出的CMOS型运算放大器,增益带宽5G,工作电压3.3V,工作温度-40℃~+85℃,单一2.5V~5.5V的输入共模电压300mV的范围,最大静态电流仅为250mA[5]。

3 FPGA的数据传输帧结构设计

从图5所示 FPGA的工作过程可以看出,FPGA对数据流信号的处理,在横向上要完成帧结构、帧头以及数据复用及解复用的处理。在纵向上要完成发送端与接收端的数据通道时钟设计。有关时针同源的设计已在硬件电路的设计中描述过了,在此还需要对帧头的结构进行设计,以实现数据的自适应传输。在过程工业的控制中存在着大量的通信协议,这些协议基本都是建立在数据帧的基础之上,其差别在于数据帧的格式[6]。通过特殊的帧头设计,在接收端只要检测出数据帧头就可以立即将要传输的视频信号等数据发送出去。帧头数据在数据帧的起始位置,帧头后依次是信道的数据、串口通讯数据。采用硬件电路嵌位以及软件编程数据嵌位的方法使数据帧头具有唯一特性。

由ADC9057输入信号范围通过运放的硬件电路嵌位为2.205V~2.925V。又ADC精度8bit,2~3V的输入,则输入2.925V对应的二进制为11101011,2.205V对应为00111100。为应对有效数据突变,在FPGA内部对输入信号进行软件编程嵌位,使ADC转换后的值最大嵌位在11101011,最小嵌位为00111100。最小值嵌位是防止长0出现,影响数据传输。根据排列组合,只要将帧头设置超过10个连续以上的1就保证了帧头唯一性。为方便计算及传输,帧头设置为0001111111111000,为16bit。

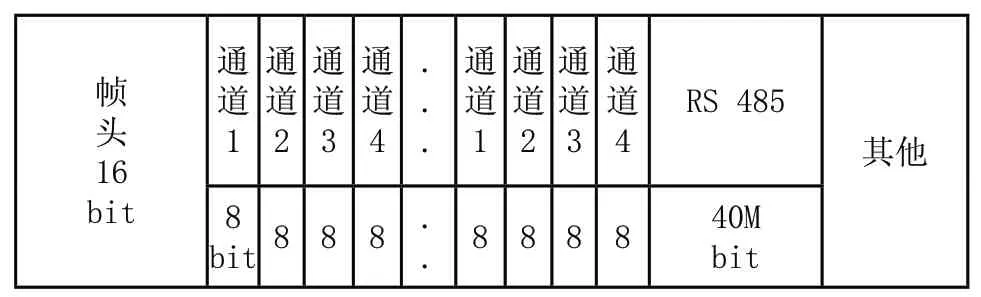

前面已经设计一周期数据为3 G,有效数据为2880M,规定0.5s为一帧,那么一帧数据就为1500Mbit,视频有效数据1440Mbit,RS485定义40Mbit,其他为预留空间。则帧结构如表1所示。

表1 帧结构表

4 系统测试

系统测试是检测系统传输过程中信号的时钟抖动、眼图优劣、设备的灵敏度、设备的动态范围以及系统的功耗等。

光端机信号测试眼图,如图6所示,可以看到眼图的轮廓明显,眼睛挣得很开,交叉点平衡,信号变换间没有大的抖动,完全没有压到眼图的模板,没有码间串扰现象,因此可以知道系统信号传输稳定,信号质量很高。

图6 信号测试眼图

将光端机视频信号的接收端分别接入标清及高清的不同格式视频信号,经测试表明当传输960H、720p每秒25帧、1080p每秒25帧等高清视频图像时,图像显示稳定,无噪点、画面平滑、连续、不卡帧,因此光端机具有自适应高标清视频信号传输的能力。

5 结束语

本文研究的四路高标清视频自适应传输数字光端机系统,设计基于FPGA平台,通过调试及测试,验证了高清标清视频自适应传输功能,实践检验光端机具有标清、高清信号传输能力,达到了设计技术指标。光端机在数据帧的设计中,有多的数据量传输富余,可以用于实现更多的其他业务数据传输需求。

[1]AD9057 [DB/OL].http://pdf1.alldatasheet.com/ datasheet-pdf/view/48514/AD/AD9057.html

[2]CycloneIVFPGA[DB/OL].https://www.altera.com/content/dam/ altera-www/global/en_US/pdfs/ literature/hb/cyclone-iv/cyclone4-handbook.pdf.

[3]潘波,朱伟.基于Serdes的千兆以太网设计与实现[J].微处理机.2014,(01),33-35.

[4]ART-B41XX [DB/OL].http://www.allrayinc.com/main/ProductParameter_om.asp?PParentID=72&ParentID=90&SortID=99&id=654.

[5]OPA2345 [DB/OL].http://pdf1.alldatasheet.com/datasheet-pdf/view/56774/BURR-BROWN/OPA2345.html.

[6]董立,尤枫,赵恒永.基于用户定制的数据帧处理技术[J].计算机工程与设计,2010,(12),3003-3005.