高性能处理器存储控制器分析与优化设计

2015-11-29孙也

孙也

(吉林广播电视大学,吉林 长春 130022)

高性能处理器存储控制器分析与优化设计

孙也

(吉林广播电视大学,吉林 长春 130022)

针对处理器访存延时问题,本文对X处理器和DDR3 SDRAM进行了深入分析。为提高访存过程的并行性,对存储控制器的结构进行了优化设计。设计了全异或地址映射方式和分层访存调度器,从而提高了存储器带宽利用率,具有一定的实际应用价值。

存储控制器;优化;处理器

一、引言

存储控制器决定了计算机的内存容量、内存类型与速度等重要参数,控制着存储器的访问速度,决定了处理器性能的发挥,尤其在多线程、多核心的处理器中更为突出。因此,存储控制器设计的好坏直接影响处理器性能的高低。

针对现有X处理器存储控制器中存在的访存延时问题,为提高访存过程的并行性,本文对存储控制器地址映射方式和访存调度模式进行了优化设计,通过对命令重排序,改变访存地址,减少延时,以此提高存储器带宽利用率和存储性能。

二、存储控制器基本结构

存储控制器连接存储器和L3 cache,用于接收来自L3 cache的访存请求,按照访存请求的优先级进行调度,将访存请求转换成存储器能够识别的语言后发送到存储器,完成数据读写任务。

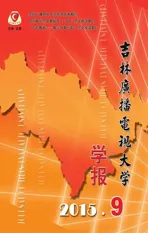

X处理器集成了4个宽度为64位的DDR3存储控制器,工作频率达1600MHz,从而满足其高性能运算的需求。具有限制功耗、错误检测、自动配置等功能,防止因功耗过大而影响处理器的性能,提高了存储控制器的可靠性及可维性,其结构如图1所示。

图1 存储控制器结构

可以看出,存储控制器主要包括传输层和物理层,前者主要用来接收来自用户层的存访请求,转化为物理层可识别的语言后发送到物理层,同时也承担接收物理层返回数据的功能。再按照上层逻辑所需要的时序发送给上层用户逻辑,后者则按规定的格式将传输层送来的信息发送到DDR3芯片上,同时也担负接收DDR3读出数据的作用。

三、存储控制器优化设计

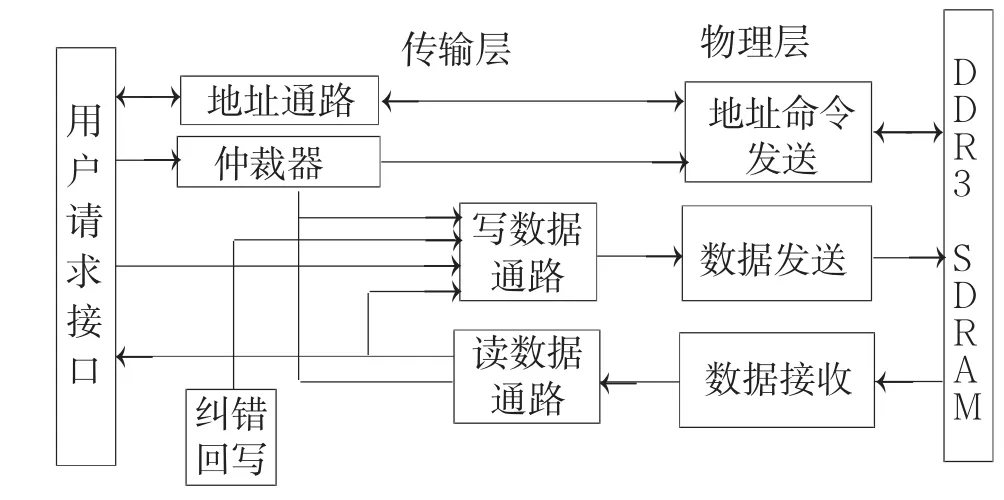

X处理器芯片集成了4个采用多体并行存储结构的存储控制器,每个存储控制器可以管理4个rank,共享一条外部总线,数据访问量很大,所以对映射方式和存储调度过程都有很高的要求。基于此,本文在原有存储控制器结构的基础上,对存储控制器中进行优化设计:一是增加了访存调度器模块;二是对用户请求接口映射逻辑进行改进;三是增加了虚拟缓冲行模块,如图2所示。

图2 存储控制器优化结构

1、地址映射设计

用户请求接口是上层用户与DRAM控制器之间的接口,包括地址映射逻辑、控制逻辑以及请求队列三个组成部分,用于接收L3 Cache发送的访存请求、请求信号的读、写与传输,以及完成物理地址到存储器实际地址的映射。

基本地址映射方式只针对同一个通道中的同一行的映射关系,并行执行程序的优势还没有发挥出来。同时,多核多线程处理器容易导致bank发生访问冲突,这一问题用现有的地址映射方法还不能有效解决。针对这一问题,本研究对地址映射方式进行优化,设计了一种全异或地址映射方式,即取出一部分请求地址与rank地址异或形成新的rank地址,另一部分与bank地址异或形成新的bank地址,如图3所示。

图3 优化后的映射方式

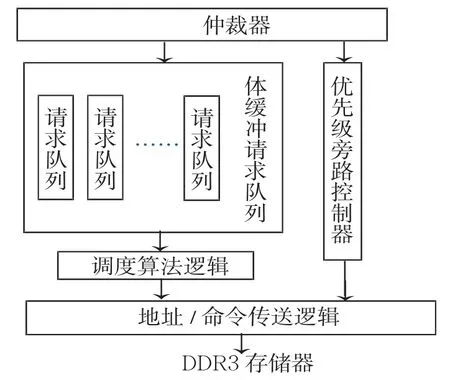

2、分层访存调度

内存系统的带宽和延时与访问的存储体地址和行列地址有着密切的联系,为此本文采用分层调度算法,访存调度流程如图4所示,可根据当前请求和下一请求的地址是确定当前请求访问状态。当前请求读写访问结束时,被访问行将关闭,新的命中行开启,否则当前请求将禁止自动预充,读写访问结束时,当前被访问行保持开启状态。该方法可有效改变访存地址,减少延时,提高存储性能。

图4 访存调度流程

四、结论

X处理器是一款多核多线程高性能处理器。为解决处理器与存储器之间速度差距问题,本文的设计设计一款符合X处理器访存特性的高效存储控制器。提出了改变地址映射方式和存储调试模式的优化设计方案,提高了数据传输的并行性,降低了访存延时,大大提高了处理器的性能。

[1]邓丽.高带宽低延迟的DDR2存储器控制器的研究与实现[D].长沙:国防科技大学,2006:25~28.

[2]陈先.嵌入式SRAM控制器验证关键技术研究[D].西安:西安电子科技大学,2009(1):13-15.

TP332

A

1008-7508(2015)09-0101-02

2015-07-11

孙也(1981-),吉林长春人,吉林广播电视大学讲师,计算机科学与技术专业。