基于FPGA的视频与通讯数据融合设计

2015-10-22韩红霞张海波

韩红霞,孙 航,张海波

(中国科学院长春光学精密机械与物理研究所,吉林长春130033)

基于FPGA的视频与通讯数据融合设计

韩红霞∗,孙 航,张海波

(中国科学院长春光学精密机械与物理研究所,吉林长春130033)

为实现将时间值、方位值等串口通讯信息叠加进数字视频图像信号的某一固定行中,设计了基于FPGA的通讯数据与数字视频数据的融合系统.采用FPGA程序设计实现串行数据接收与内置FIFO处理,并提取视频数据的某一固定行,进行数据融合,使得通讯数据和视频数据在场信号有效下组合输出.基于FPGA的通讯数据与数字视频数据的融合系统实现了通讯数据与视频数据的融合,试验中通讯数据波特率为230.4 kbit/s,视频信号帧频50 Hz,视频数据与通讯数据帧频相同,图像像素为1 024×1 024,通讯数据正确的融合入一场图像的最后一行中,系统工作稳定,工作状态良好.基于FPGA的通讯数据与数字视频数据的融合系统以最简硬件系统实现了通讯数据与数字视频数据的组合输出,满足图像处理及显示系统的要求,具有广泛的工程意义.

视频数据;通讯数据;融合;FPGA

1 引 言

针对图像处理及图像显示等系统的要求,需要将通讯数据叠加进数字视频信息的某一固定行中,设计基于FPGA的通讯数据与视频数据融合系统.采用FPGA编程实现时间、角度值等通讯信息到视频信息的叠加,叠加信息可以在一场图像中指定的任意一行输出,提供给后续的图像处理、图像显示等系统.对通讯数据的接收以及通讯数据到视频数据的融合完全采用基于FPGA的Verilog语言编程结合图形编程实现,在FPGA内部构建通讯数据波特率匹配模块、串行数据的接收模块、行同步信号提取模块以及通讯数据与视频数据组合模块等,实现通讯数据到视频数据的融合功能.通讯数据到视频数据的融合系统设计实现了需要的通讯信息到视频数据的叠加显示等功能,试验证明:系统工作稳定,状态良好[1-3].

2 硬件设计

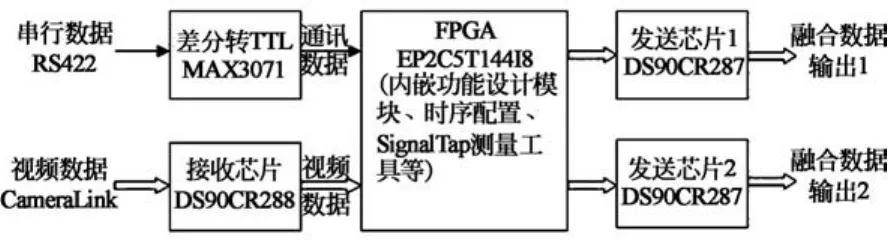

基于FPGA的通讯数据与视频数据融合设计在硬件设计中包括:串行数据输入、数字视频数据输入、FPGA及外围电路、通讯与视频数据融合输出等部分,如图1所示.

图1 通讯数据与视频数据融合硬件结构示意图Fig.1 Hardware structure diagram of communication data and video data composition system

串行输入数据是RS422格式,经差分转TTL芯片MAX3071得到LVTTL格式信号,数字视频输入信号为Camera_Link格式,经Camera_ Link接收芯片DS90CR288得到并行的LVTTL信号,经转换的通讯数据和视频数据分别输入FPGA,FPGA接收串行数据并将其融合入数字视频信号的某一指定行中,实现通讯数据与视频数据的融合,融合数据经Camera_Link发送芯片DS90CR287转换为Camera_Link标准数据,进行输出.

通讯数据与视频数据融合设计的核心是FPGA,FPGA进行逻辑控制和时序配置,同时采用Verilog语言编程结合内嵌功能模块以及Signal-Tap工具,可以实现各种逻辑及时序功能设计. FPGA通过为每个功能建立单独的硬件来实现整个应用程序所需要的逻辑功能,因此具有并行处理的内在特点,程序速度快、运行灵活,并且FPGA内部采用流水结构,因此非常适合进行图像及逻辑方面的相关设计.

通过对FPGA的编程实现了串行数据的接收、串行数据与视频数据的融合以及所有外围芯片的逻辑控制.FPGA内部主要包括4个功能模块,分别是波特率产生模块、串行数据接收模块、行同步信号处理模块和数据处理及融合模块,其中波特率产生模块,是根据已知的接收数据波特率,处理外部时钟信号,产生与波特率相对应的数据接收时钟信号[4-5];串行数据接收模块负责按位接收串行通讯数据,并将有效位数据并行化;行同步信号处理模块负责根据需要提取需要拟合通讯数据的行,或者在行消隐期做出可以拟合通讯数据的行信号,这部分根据工程设计的实际需要,本设计中根据要求将通讯数据拟合进一场数据中的最后一行;数据处理及融合模块负责将视频数据和通讯数据进行组合输出,按时序要求提供给后续图像处理、存储等系统.

3 FPGA程序设计

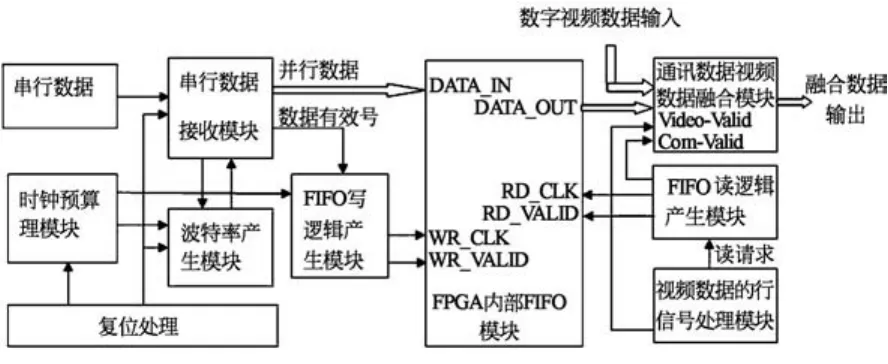

对FPGA编程主要采用Verilog语言结合内嵌功能模块以及内部集成的Signal Tap测量工具实现,主要包括波特率产生模块、串行数据接收模块、行信号处理模块以及通讯数据与视频数据融合模块等.图2给出基于FPGA的通讯数据与视频数据融合程序设计框图.

如图2所示,串行数据输入后,FPGA首先要根据串行数据的波特率产生与输入数据相匹配的接收时钟,即由波特率产生模块产生能够采到每一位数据的有效时钟信号.接着串行数据接收模块根据波特率产生模块提供的有效时钟信号按位接收数据,将串行数据转换为并行数据,并产生与每一个字节对应的数据有效信号[6-8].FIFO写逻辑产生模块根据串行数据接收模块提供的数据有效信号以及时钟预处理模块提供的时钟信号产生FIFO的写时钟信号WR_CLK和FIFO的写有效信号WR_VALID.以上模块均是对串行接收数据进行处理,接下来对数字视频信号进行处理,以达到通讯数据与视频数据融合的目的.视频数据的行信号处理模块负责从场信号包含的若干行信号中提取要发送通讯数据的行信号,并将这个行信号提供给FIFO读逻辑产生模块.读逻辑产生模块根据视频信号的像素时钟和行信号处理模块提供的读请求信号产生FIFO的读时钟信号RD_CLK和读有效信号RD_VALID.FIFO根据读写逻辑,对并行化的串口接收数据进行缓存后输出,得到与视频数据时序相同的信号.最后通讯数据与视频数据融合模块在Video_Valid有效时输出视频信号,在Com_Valid有效时输出通讯信号,并将两者进行时序和数据的整合,得到一场既包含视频信号又包含通讯信号的融合数据输出[9-10].

图2 FPGA实现通讯数据与视频数据融合框图Fig.2 FPGA design diagram of communication data and video data composition system

4 实 验

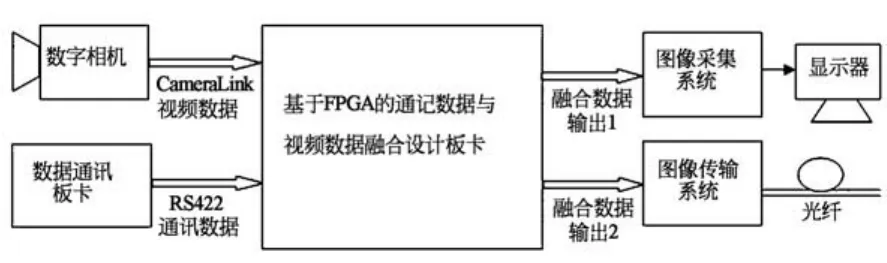

基于FPGA的通讯数据与视频数据融合设计实验中,采用1M30数字相机作为数字视频输出信号源,数据通讯板作为通讯数据的输出信号源,图3给出实验结构图.

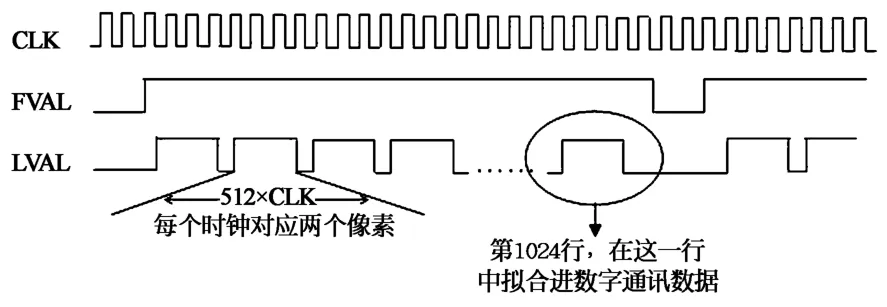

如图3所示,实验中,1M30相机作为视频数据源为通讯数据与视频数据融合设计板卡提供CameraLink格式的数字视频信号,数据通讯板作为通讯数据源为通讯数据与视频数据融合设计板卡提供RS422格式的通讯数据.基于FPGA的通讯数据与视频数据融合设计板卡将输入的视频数据与通讯数据进行融合,得到将通讯数据拟合入视频数据某一固定行中的融合输出数据,分别输出给图像采集系统和图像传输系统.实验中视频数据像素帧频为50 Hz,像素时钟为40 MHz,像元尺寸1 024×1 024,每个像素时钟对应两个12位的数据,将通讯数据拟合入视频数据的最后一行,时序如图4所示.

图3 基于FPGA的通讯数据与视频数据融合设计实验结构图Fig.3 Experiment diagram of the communication data and video data composition system

图4 视频数据时序简图Fig.4 Time sequence diagram of the video data

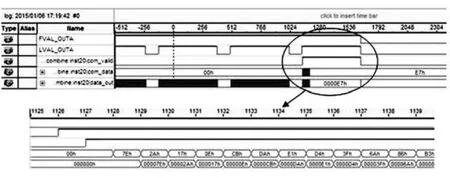

如图4所示,视频输出信号的时序测量显示场同步信号FVAL有效电平下包括1 024个行信号LVAL,行信号有效包括512个时钟信号,而每个时钟信号对应24位的数据输出,表示两个12位的像素值,因此一场图像为1 024×1 024×12 bit,按照要求需要将通讯系统发送的数据拟合进一场图像的最后一行中,基于FPGA的通讯数据与视频数据融合设计实现了这一功能,图5给出采用FPGA内嵌的Signal Tap工具进行测量,得到的数据拟合观测图.

如图5所示,Signal Tap观测图显示,输出的场同步信号和行同步信号与原视频输入的场同步信号和行同步信号一致.在融合数据的最后一行,是通讯板发送的通讯数据,已知通讯板发送来的数据是以7E开头E7结尾的一帧数据,波特率为230.4 kbit/s,图5中显示最后一行数据是融合的通讯数据,由于每个时钟对应的视频数据为24位,为与其保持一致,将通讯数据扩展为24位数据,可以看出融合的通讯数据与原通讯数据一致.图像采集系统对融合数据进行了数据采集并显示,图6给出采集图像显示图.

图5 拟合数据Signal Tap观测图Fig.5 Composition data collected by the SignalTap tool

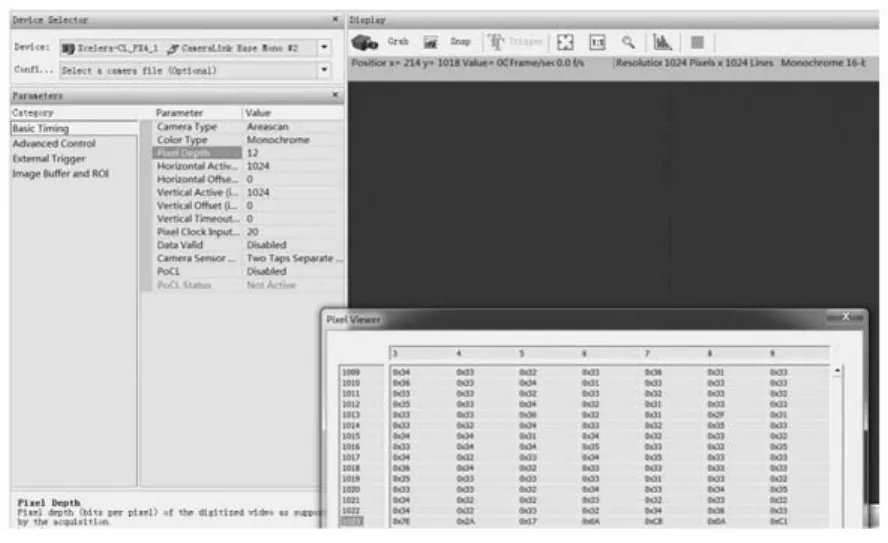

图6 图像采集及像素显示示意图Fig.6 Collected image and pixel value display diagram

图6给出图像采集示意图,用PIXELVIEW工具可以看到指定区域的像素值,从图中可以看出一场图像的最后一行即图中显示的第1 023行的像素值是7E开头E7结尾的通讯拟合数据.图中对像素值的显示说明:基于FPGA的通讯数据与视频数据融合系统设计实现了视频数据与通讯数据的融合,拟合的数据正确,系统工作稳定.

5 结 论

基于FPGA的通讯数据与视频数据融合系统设计实现了将通讯数据拟合进视频数据某一固定行中的功能,实验中视频数据为像素时钟40 MHz,像元尺寸1 024×1 024,数据位12 bit的Camera_Link格式数据,通讯数据为7E开头E7结尾的随机数,实验证明板卡实现了通讯数据到视频数据的融合,融合进视频数据最后一行的通讯数据完整、正确,满足图像采集系统、图像显示系统等后续系统的需求.目前板卡已应用于具体的工作项目中,工作稳定,性能良好.基于FPGA的通讯数据与视频数据融合系统设计成功的将角度信息、时间信息等通讯数据拟合进视频数据中,方便的数据的处理和显示,具有广泛的工程应用意义.

[1] 熊文彬,蒋泉,曲建军,等.基于FPGA实现的视频显示系统[J].液晶与显示,2011,26(1):92-93.

Xiong W B,Jiang Q,Qu J J,et al.Video display system based on FPGA[J].Chinese Journal of Liquid Crystals and Displays,2011,26(1):92-93.(in Chinese)

[2] Levine P A,Saucer D J,Shallcross F V.High frame rata multi-port CCD image and camera[J].SPIE,1992,1952:257-267.

[3] Li X Z,Yu Z Y,Shang F.Multifunction image target generator[J].Experimental Technology and Management,2002,19(4):36-37.

[4] 王明富,杨世洪,吴钦章.大面阵CCD图像实时显示系统的设计[J].光学精密工程,2010,18(9):2053-2059.

Wang M F,Yang S H,Wu Q Z.Design of large-array CCD real time display system[J].Optics and Precision Engineering,2010,18(9):2053-2059.(in Chinese)

[5] 穆欣,胡君,宋启昌,等.空间相机集成测试系统的时钟同步[J].光学精密工程,2010,18(6):1436-1443.

Mu X,Hu J,Song Q C,et,al.Time synchronization of integrated testing system of space camera[J].Optics and Precision Engineering,2010,18(6):1436-1443.(in Chinese)

[6] 郭敬明,魏仲慧,何昕,等.CCD星图模拟器的设计及验证[J].中国光学与应用光学,2010,10(3):486-493.

Guo J M,Wei Z H,He X,et al.Design of CCD starmap simulator and its validation[J].Chinese Journal of Optics and Applied Optics,2010.10(3):486-493.(in Chinese)

[7] 刘妍妍,张新,张建萍.超分辨重建技术及其研究进展[J].中国光学与应用光学,2009,4(2):102-111.Liu Y Y,Zhang X,Zhang J P.Super resolved reconstruction technologies and recent evolution[J].Chinese Journal of Optics and Applied Optics,2009,4(2):102-111.(in Chinese)

[8] 陈娟,陈乾辉,师路欢,等.图像跟踪中的边缘检测技术[J].中国光学与应用光学,2009,2(2):46-53.

Chen J,Chen Q H,Shi L H,et al.Edge detection technology in imaging tracking[J].Chinese Journal of Optics and Applied Optics,2009,2(2):46-53.(in Chinese)

[9] 胡君,王栋,孙天宇.现代航天光学成像遥感器的应用与发展[J].中国光学与应用光学,2010,12(3):519-533.

Hu J,Wang D,Sun T Y.Application and development of recent space optical imaging remote sensors[J].Chinese Journal of Optics and Applied Optics,2010.12(3):519-533.(in Chinese)

[10] 杨为锦,孙强.中波红外连续变焦系统设计[J].中国光学与应用光学,2010,4(3):164-169.

Yang W J,Sun Q.Design of middle infrared continuous zoom system[J].Chinese Journal of Optics and Applied Optics,2010,4(3):164-169.(in Chinese)

Composition design of communication data and video data based on FPGA

HAN Hong-xia∗,SUN Hang,ZHANG Hai-bo

(Changchun Institute of Optics,Fine Mechanics and Physics,Chinese Acadeny of Sciences,Changchun 130033,China)

To realize the composition of the serial port information such as time and azimuth value on the fixed line of the digital video signal,the communication data and digital video signal composition system has been designed.Based on FPGA,the serial port data is received and processed by the FIFO module,and a fixed line signal is extracted.The communication data and video signal composition is realized,and the composition data is output under the frame valid signal.The communication data and digital video signal composition system based on FPGA realized the data composition function.In the experiment,the baud rate of the communication data is 230.4 kbit/s,frame rate of the video signal is 50 Hz,pixel size is 1 024×1 024,the communication data is composed in the last line of one frame video signal correctly,the system works stably and the work status is good.The communication data and digital video signal composition system based on FPGA realizes the data composition in the simplest hardware system,meets the requirements of the image processing and display system,has broad engineer meaning.

video data;communication data;composition;FPGA

TP331

A doi:10.3788/YJYXS20153006.0987

1007-2780(2015)06-0987-05

韩红霞(1979-),女,河北宣化人,博士,副研究员,主要从事光纤通信及FPGA设计等作.E-mail:71828@sina.com

2015-02-23;

2015-06-08.

∗通信联系人,E-mail:mail:71828@sina.com