Ao基于振荡采样的真随机数发生器设计与实现

2015-07-12王晓燕杨先文

王晓燕 ,杨先文

(1.河南中医学院,河南郑州,450008;2.信息工程大学,河南郑州,450000)

0 引言

在信息系统中,密码技术是保护信息安全的核心。密钥管理、密码协议、数字签名、身份认证等对随机序列的应用也越来越广泛。同时随着芯片设计SoC时代的到来,FPGA凭借成本低、设计周期短等优点倍受青睐,基于FPGA实现密码算法已越来越普及,密码SoC具备随机数产生功能是系统安全性的根本要求。因此,如何设计噪声随机可靠,可完全FPGA实现,且资源消耗少的真随机数发生器(true random number generator, TRNG)是重要研究内容之一。本文在对噪声源模型分析的基础上,设计了数字噪声源模块。基于此,在并行输出及控制、在线随机测试等方面进一步探讨,设计并实现了一款TRNG。其噪声源理论可靠,具有速度快、性能好、成本低的应用价值。

1 真随机数发生器结构

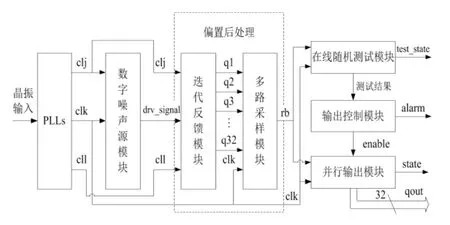

为满足应用系统的实际需求,随机数发生器不仅要保证足够高的输出速率,而且要确保产生序列具有良好的随机性。本文提出的适合FPGA实现的TRNG结构如图1所示,主要由锁相环(PLL)模块、数字噪声源模块、偏置后处理模块、在线随机测试模块、输出控制模块和并行输出模块组成。

图1 基于振荡采样的真随机数发生器结构

PLLs模块由三个独立PLL组成,用于产生TRNG所需的三个时钟信号clj、clk和cll;数字噪声源模块产生随机驱动信号drv_signal,经后处理模块纠偏后产生随机比特rb,依次进入并行输出模块后等待输出。

由于芯片在启动前可能遭受硬件篡改攻击,从而影响随机数发生器自身性能,为确保随机数的质量,保证密码系统的应用安全,在系统上电时对TRNG的启动状态进行自检。在本文设计中,每次上电自检产生20,000比特传送给在线随机测试模块,并将测试结果传送给输出控制模块。若测试未通过,则输出控制模块置控制使能enable为0、报警信号alarm为1,即禁止并行输出模块向外输出产生序列,同时向外部应用环境发送报警信号;否则表示TRNG未遭受硬件篡改。

2 具体模块设计

2.1 数字噪声源模块设计

基于FPGA的噪声源有两种参考设计:1) 环形振荡器或锁相环的抖动;2) 逻辑单元的亚稳态性。本文基于时钟振荡采样原理,利用FPGA内置PLL的抖动行为设计随机噪声源,如图2所示。

图2 基于PLL的噪声源模型

噪声源模型由两个PLL、一个D触发器和一个异或链电路组成。其中,PLLs模块输出两个时钟信号clk和clj,且它们之间满足

其中,Tclk和Tclj分别是clk和clj的周期,fclk和fclj分别是clk和clj的频率,CM和CD分别是clk和clj的系数因子,且为了使得采样点有最大的循环周期,有GCD(CM,CD)=1成立。当采样个数达到CD时,异或链电路进行工作,将CD比特异或后输出1比特随机数。

异或链电路由CD个D触发器构成,采样得到的随机比特经过 个触发器存储移位后相异或最终输出1比特,即其统计特性由定理保证(定理证明省略)。

综上,在CD个采样点中,只要有一个采样为1的概率为1 2,则Bias(bout) = 0,即异或链电路输出比特为1的概率为1 2。即使不存在i∈ {0,1,...,CD-1},使得P(xi= 1 )=1 2,但随着CD的增大,Bias(bout)也将趋向于0。

2.2 并行输出及控制模块设计

并行输出模块将32级T触发器构成的翻转采样模块输出的r1,r2,…,r32进行异或输出,然后输入至32位移位寄存器中并输出所需要的随机数。端口连接是将32位移位寄存器的时钟端连接至时钟clk,输入使能信号置1,输出使能信号连接至输出控制模块的enable,数据输入端口din连接经翻转采样模块各输出端口相异或的结果rb。当检测到clk上升沿时将随机比特rb存入寄存器,存满32位时检测enable是否有效。若enable有效,则将随机序列从端口dout并行输出,同时将状态信号state设置有效,用以标识当前32位随机数产生完毕;否则停止输出随机序列,并保持state无效。

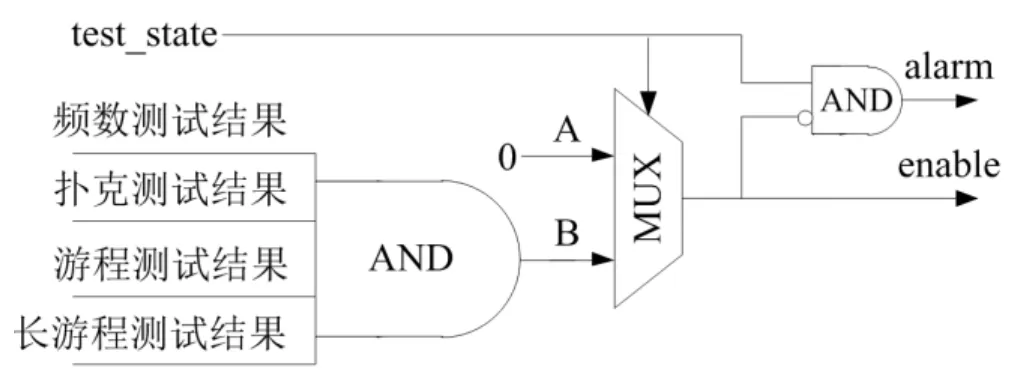

图3 输出控制模块

输出控制模块由2个与门和1个选择器组成,如图3所示。当test_state为0时,表示上电自检未完成,则选择器选通端口A,输出信号0,此时enable和alarm均无效;当test_state由0跳变为1时,表示在线随机测试结束,选择器选通端口B,若所有测试项目均通过测试,则与门输出为1,此时enable有效,alarm无效;若其中一项或多项测试未通过,则与门输出为0,此时enable无效,alarm有效,输出控制模块通过enable控制并行输出模块停止向外输出序列,同时向外输出报警信号。

2.3 在线随机测试模块设计

以FIPS 140-2为依据,设计了在线随机性测试模块,包括4个测试单元,如图4所示。

图4 在线随机测试模块

1)控制单元

控制单元主要有两个功能:1) 计数输入随机序列的比特数,当计数输入序列达到20,000比特时,向各测试单元传送bit_finish,各模块接收后结束测试,将各统计值与标准值进行比较判定,得出相应的测试结果,并向控制单元返回完成信号X_test_finish;2) 当各测试单元的X_test_finish均有效后,置test_state为1,随机性测试结束,输出控制模块接收测试结果。

2)频数测试单元

频数测试的硬件实现较容易,仅需要1个寄存器用来计数输入序列中1的个数,当检测到输入比特为1时,寄存器中的内容加1。当bit_finish有效时,将寄存器中的值与参考值进行比较,若在参考范围内则表示通过该项测试,否则表示不通过。

3)扑克测试单元

扑克测试是将20,000比特随机序列分割成5,000个连续的4比特数据块,数据块取值范围为0~15,统计5,000个数据块16种取值出现的次数,记为ni(i=0,1,...,15)。计算统计值S,

若2.16 ≤S≤46.17,则表示通过测试;否则表示不通过测试。进一步,因为式(1)很难硬件实现,所以可将其转换为先计算,再将结果与新的取值范围[Smin ,Smax ]作比较。其中,

为了减少硬件资源消耗,可计算通过测试时计数器ni中最大值的上限,从而确定计数器所需要的位数。记ni中最大值为ni0,通过上述数据求解得到ni0≈429(求解过程省略)。因此,扑克测试单元的实现需要16个9位计数寄存器、16个9位乘法器、15个21位加位器和部分比较逻辑。

4)游程和长游程测试单元

3 实现性能及测试

采用Verilog描述语言作为TRNG模型的原型设计工具,选择Altera公司Cyclone III系列EP3C80F780C6型号FPGA芯片作为TRNG实现的原型器件,并使用QuartusII 9.0软件对实现进行了编译综合。TRNG综合后共占用1,535个逻辑单元和3,160比特存储器,系统工作时钟频率(即fclk)最高为33.5MHz,随机数生成速率的最大值为33.5Mb/s。同时通过采用16种随机性测试方法对产生序列进行的测试发现,各项测试统计值p-value均大于显著性水平0.01,即表示产生序列通过了所有的随机性测试,表明本文提出的TRNG模型能够产生随机性良好的随机序列。

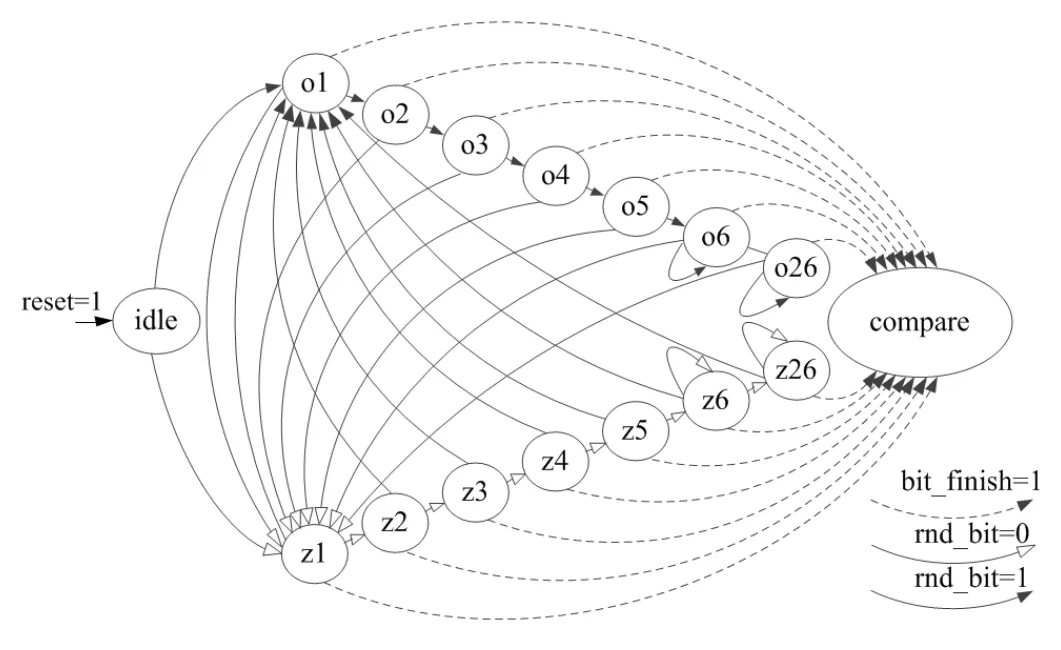

图5 游程和长游程测试状态机

游程和长游程测试实质上可归并为同一类测试,它们由一个状态机控制完成,状态跳转如图5所示,包括空闲状态(idle),比较状态(compare),游程状态zi和 ,其中i=1,...,6,26,表示相应状态下0游程或1游程的长度。当reset有效时,状态机进入空闲等待状态。之后,随机比特将依次进入状态机,当输入的第1比特为0,则状态机由空闲状态转向状态z1,如果第2比特同样为0,则状态机转向z2,继续接收下一比特;反之,如果第2比特为1,则状态机转向o1,此时表示1个游程结束,状态z1相对应的计数寄存器值加1,即长度为1的0游程个数加1。同样,当状态机从o1开始后,若下一输入比特为1,则转向o2;否则转向z1,相应的计数寄存器值加1。特别地,当状态机进入到状态z6或o6后,输入比特仍为0或1,则状态机仍保持原状态,直至输入的0或1的个数超过25时转向z26或o26。当bit_finish有效时,状态机转向比较状态,如果各寄存器值处于相应的阈值范围内,则表示通过测试;否则表示不通过测试。

4 结束语

鉴于随机数在密码技术中大量使用,文章给出了一种基于振荡采样的真随机数发生器,分别设计了数字噪声源模块、并行输出及控制模块、在线随机测试模块。原型实现结果表明其序列产生速度为33.5Mb/s,且产生序列的随机性通过了NIST SP800-22标准。下一步工作,将研究其与密码SoC的集成应用。

[1]韩越,黑勇,乔树山.一种资源优化的祖冲之算法的硬件实现方法[J].科学技术与工程,2013,13(5)∶1330-1334.

[2]王晨光,乔树山,黑勇.低复杂度SM4加密算法IP核设计[J].科学技术与工程,2013,13(2)∶ 347-350, 378.

[3]李峥,杨先文,王安.利用竞争冒险的真随机数发生器设计[J].信息安全与通信保密,2011,(1)∶72-74, 80.