一种改进型X波段双环锁相频率合成器的设计

2015-04-24刘建栋吕进来张方辉吴景峰

刘建栋,吕进来,张方辉,吴景峰

(1.中国电子科技集团公司第13研究所,石家庄 050051;2.空军驻石家庄地区军事代表,石家庄 050051)

一种改进型X波段双环锁相频率合成器的设计

刘建栋1,吕进来2,张方辉1,吴景峰1

(1.中国电子科技集团公司第13研究所,石家庄 050051;2.空军驻石家庄地区军事代表,石家庄 050051)

介绍了双环锁相的基本原理,分析了传统的频率合成方法,提出了一种改进型双环锁相频率合成器的设计方案,采用低相噪、低杂散的小数分频锁相技术,并通过优化电路结构设计,实现了比传统双环锁相频率合成器更优的性能。该设计方案简单实用,已在实际工程中得到了应用,具有一定的推广价值。

双环锁相;低相位噪声;宽频带;小步进;频率合成器

0 引 言

频率合成器的功能是产生和输出高质量的正弦信号,锁相频率合成技术具有优良的特性,特别是随着数字电路的迅速发展,锁相频率合成器所用的器件模块化、集成化,所以广泛地应用在各种电子设备和系统中[1]。其中的双环锁相技术在实现宽频带、小步进的同时,还具有低相噪、微型化、数字化的特点,文献[2]~[3]分别介绍了S波段和C波段的双环锁相频率合成器的实现。本文针对一种X波段、宽频带、小步进的频率合成器,提出了一种改进型双环锁相频率合成器的设计及实现方法。其基本指标要求为:频率覆盖范围9 400~10 400 MHz,最小步进1 MHz,相位噪声优于-90 dBc@1 kHz,杂散抑制优于70 dBc。

1 传统双环锁相分析

双环锁相是广义移频锁相的一种,原理框图如图1所示。其辅环采用高鉴相频率实现频率的大步进,主环输出信号和辅环输出信号进行下混频得到较低频率的中频信号,再反馈到主环的鉴相器,采用低鉴相频率实现频率的小步进。双环锁相比整数模式的单环锁相能实现更低的相位噪声,相比小数模式的单环锁相能实现更好的杂散抑制,具有低成本、高可靠性和良好的环境适应性等优点。

依据图1所示的原理图,主环的分频系数为M=N2/R2,N2为主环射频信号分频比,R2为主环参考信号分频比;辅环的分频系数为M=N1/R1,N1为辅环射频信号分频比,R1为辅环参考信号分频比。在设计时,通过合理优化主环、辅环的分频系数,使两者尽量低且比较接近,以保证性能的最优化。

图1 双环锁相原理图

采用上述传统的双环锁相方案实现在X波段、工作带宽1GHz、步进1MHz的频率合成时,一方面,主环和辅环混频产生的中频频率不能过低,否则由于混频交调产生的镜像频率可能发生“错锁”;另一方面,为实现1MHz步进,鉴相频率最大为1MHz,使得鉴相频率过低,为抑制鉴相泄露,环路滤波器带宽必须窄,这将导致环内的相噪恶化,无法达到指标的要求。为了解决上述困难,本文提出了一种改进型双环锁相的技术方案。

2 改进型合成器的设计

2.1 改进型方案设计

改进型双环锁相方案,在主环和辅环均采用高鉴相频率,避免了鉴相频率过低、分频次数过高导致的相噪恶化;同时在辅环采用小数分频锁相技术,实现小步进;小数分频产生的杂散信号可以通过主路锁相环路的低通滤波器予以滤除,从而解决了宽频带、小步进的技术难点,达到了低相位噪声、低杂散的要求。2种方案的技术特点对比见表1。

改进型方案实现需要解决的关键技术包括:一是高鉴相频率、低相位噪声的小数分频技术;二是小数分频产生的小数杂散的有效抑制。随着近年来集成化性能优良的小数分频鉴相器的涌现,使得实现上述技术不再是问题。该类鉴相器目前最高的工作频率为8GHz,鉴相频率为50MHz,器件噪底为-226dBc/Hz,具有一个24Bit小数模式分频器,提供0Hz频率误差和极低信道噪声的小数频率[4]。

表1 2种方案技术特点对照表

改进型X波段频率合成器的原理如图2所示。在该方案中,经过选择优化,主环鉴相器的工作频率为1 920~2 920MHz,整数鉴相频率为10MHz,步进10MHz;辅环鉴相频率的工作频率7 480~7 489MHz,小数鉴相频率为50MHz,步进1MHz。

图2 改进型双环锁相原理图

2.2 相位噪声设计

此频率合成器由2个锁相环构成。文献[5]就锁相环频率合成器的相位噪声做了详细分析,基于锁相环的相位噪声模型建立此改进型双环锁相频率合成器的相位噪声模型,如图3所示。其中环路1为辅环,环路2为主环。对输出相位噪声起主要作用的是参考部分、器件噪底及压控振荡器(VCO)的影响,由于主要关注的是1kHz的相位噪声特性,因此主要分析参考及器件噪底的影响。

图3 相位噪声模型

根据锁相环的相位噪声特性,参考源在输出端引入的相位噪声为:

Nref(f)=Sref(f)+20lg(fn/fr)

(1)

式中:Sref(f)为参考源的相位噪声;fn为参考信号频率;fr为鉴相频率。

参考源采用100 MHz的信号,其相位噪声优于-150 dBc@1 kHz。基于公式(2)辅环和主环参考源引入的噪声分别为:-112 dBc/Hz@1 kHz、-120 dBc/Hz@1 kHz。

根据文献[6],器件噪底在输出端引入的相位噪声:

NPD(f)=NFOM+20lg(f0/fr)+10lgfr

(2)

式中:NFOM为鉴相器噪底;f0为射频信号频率。

辅环选用鉴相器HMC704LP4的噪底为NFOM=-226 dBc/Hz2,主环选用器件ADF4106的噪底为NFOM=-216 dBc/Hz2,基于公式(2)辅环和主环器件噪声引入的噪声分别为:

NPD1(f)=-226+20lg(7 489/50)+10lg50= -106 dBc/Hz@1 kHz

NPD2(f)=-219+20lg(2 920/10)+10lg10= -99 dBc/Hz@1 kHz

另外,辅环选用的鉴相器HMC704LP4在近端的相噪恶化还包括闪烁噪声,根据文献[4],器件闪烁噪底在输出端引入的相位噪声为:

Nflick(f)=NFOM-flick+20lgf0-10lgfoffset

(3)

式中:NFOM-flick为器件闪烁噪底;foffset为偏离中心频率。

在偏离中心频率1 kHz处,辅环闪烁噪声为:

Nflick(f)=-226+20lg7 489- 10lg1 000=-98.5

则辅环的输出相位噪声为:

通过对比参考源和器件噪底2种噪声源的影响,发现主要影响因素是器件的噪底,即2个环路的相位噪声:

SO1(f)=NPD1(f)=-98 dBc/Hz@1 kHz

SO2(f)=NPD2(f)=-99.6 dBc/Hz@1 kHz

最后的输出为2个环路的混频输出,其输出相位噪声为:

由上述分析可知,此改进型双环锁相频率合成器的相位噪声可以达到指标要求。

2.3 杂散设计

频率合成器中杂散信号的产生主要有3个方面:一是主环和辅环混频产生的各阶交调信号;二是数模混合电路的信号串扰;三是小数分频锁相产生的杂散信号。

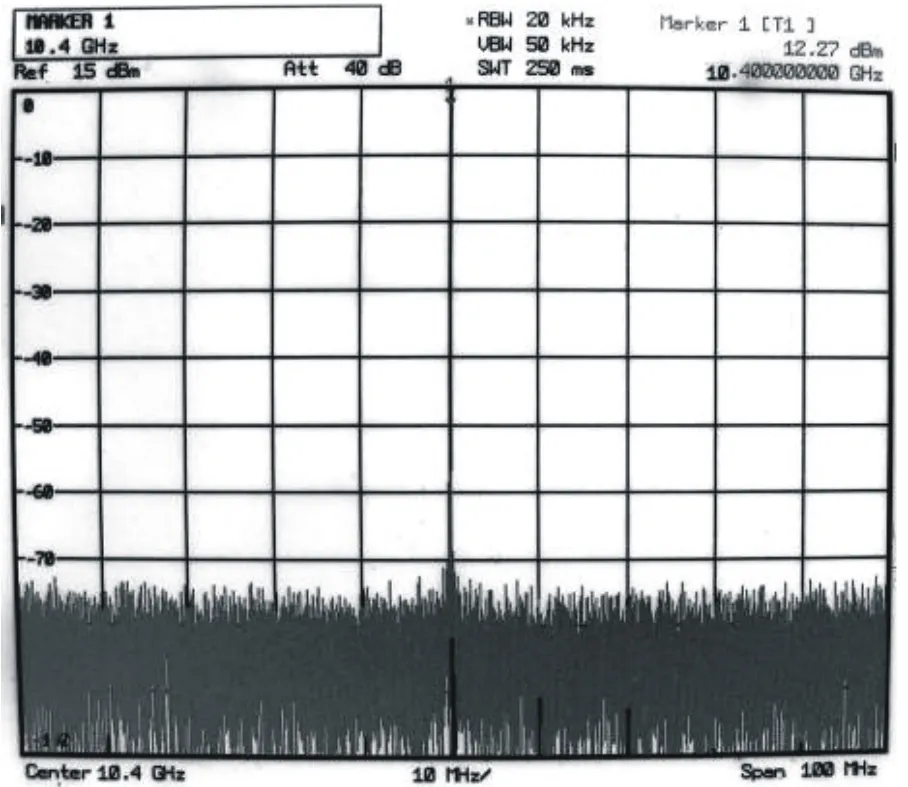

对于前2种情况,可以通过电路滤波和结构的优化设计,予以降低、消除,这里主要讨论对小数分频产生的杂散信号的抑制。由于VCO的输出频率不是鉴相频率的整数倍,VCO与鉴相频率谐波的交调会产生小数杂散。依据文献[4],杂散位于f=nfPD+fPDd/m附近,其中fPD为鉴相频率,n、d、m为正整数,且d 主环为整数分频锁相,不存在类似的情况,而且环路滤波器具有优良的低通特性,可以滤除辅环信号带来的远端杂散信号,进一步提高了输出信号的频谱纯度。 2.4 电路及结构设计 在双环频率合成器中,数、模电路相互交叉、影响,同时混频产生的寄生交调信号比较复杂,为了实现宽频带、小步进、高频谱纯度的信号输出,合理的电路布局及结构优化设计非常重要。在设计时,依据集成化、模块化的设计思路,对主、辅环分单元进行电路和结构的优化分腔布局,对射频和数字电路及电源采用微波电路多层布线方案,分成独立的上下两面,中间采用电磁兼容滤波器馈电互联,解决了信号的串扰问题,提高了杂散抑制度。以上设计使得该X波段频率合成器具备了体积小、重量轻、电磁兼容性好、性能优良等特点,满足了实际工程的使用要求。 研制的工程样机的微波电路布局和结构设计如图4所示,电源和数字电路部分在盒体背面。 图4 微波电路布局图 本文设计的X波段频率合成器实现了-50~+ 85 ℃工作温度范围内,输出频率范围9 400~10 400MHz,频率步进1MHz,输出功率13±1dBm,相位噪声- 93dBc/Hz@1kHz,杂谱抑制-73dBc,产品体积120mm×70mm×20mm,实现了小型化。图5、图6所示为频率合成器频谱测试图。 图5 相位噪声测试图 从上述测试结果可以看出,10.4GHz处信号的相位噪声-93.3dBc/Hz@1kHz,杂散抑制达到了-73dBc,相位噪声与前面的理论计算值有近3dB的差距。这是由于在相位噪声的理论估算中还 有环路滤波器的噪声等一些影响较小的噪声没有计算进去,因此会略有差距。综合各项测试指标参数,此设计很好地达到了预期的设计目标。 图6 杂散抑制测试图 本文提出的改进型双环锁相频率合成器将高鉴相频率、低相噪、低杂散小数分频锁相模式和整数分频锁相模式有机地融合在一起,相对于传统的双环锁相频率合成器, 在不增加硬件复杂度的情况下,实现了更宽的工作带宽和同等的小步进要求,获得了更优的相位噪声和高频谱纯度的信号。该设计方案简单易行, 已在实际工程中得到了应用,具有一定的推广价值。 [1] 王家礼,孙璐.频率合成技术[M].西安:西安电子科技大学出版社,2009. [2] 胡晓文,方立军.一种双环锁相频率合成器的研究[J].合肥工业大学学报,2009,32(2):174-176. [3] 方立军,马骏.C波段低相噪数字锁相频率合成器[J].系统工程与电子技术,2001,23(2):22-24. [4]HITTIE.HMC704LP4Edatasheet[EB/OL].http://www.hittite.com/content/documents/data_sheet/hmc704lp4e.pdf,2011-04-05. [5] 张福洪,陶士杰,栾慎吉.锁相式频率合成器相位噪声分析与仿真[J].电子器件,2009,32(3):22-24. [6]BrennanPV,ThompsonI.Phase/frequencydetectorphasenoisecontributioninPLLfrequencysynthesizer[J].ElectronicLetter,2001,37(15):939-940. Design of An Improved X Band Double Phase-locked Loop Frequency Synthesizer LIU Jian-dong1,LV Jin-lai2,ZHANG Fang-hui1,WU Jing-feng1 (1.The 13th Research Institute,CETC,Shijiazhuang 050051,China; 2.Military Representative of Air Force in Shijiazhuang Area,Shijiazhuang 050051,China) This paper introduces the basic principle of double phase-locked loop,analyzes the traditional frequency synthesizing method,brings forward a design scheme of improved double phase-locked loop frequency synthesizer,uses the fractional frequency dividing phase-locked technology with low phase noise and low stray to realize better performance than traditional double phase-locked loop frequency synthesizer by optimizing the circuit structure design.This design scheme is simple and practical,and has been applied in the actual engineering,is of definite extensible value. double phase-locked loop;low phase noise;wide band;small step;frequency synthesizer 2014-11-14 TN74 B CN32-1413(2015)01-0106-04 10.16426/j.cnki.jcdzdk.2015.01.025

3 研制结果与分析

4 结束语