基于FIR数字滤波器的激光陀螺信号的提取

2015-04-07田熙燕张春侠路静

田熙燕,张春侠,路静

(1.河南科技学院,河南新乡453003;2.北京航天自动控制研究所,北京100854;3.宇航智能控制技术国家级重点实验室,北京100854)

基于FIR数字滤波器的激光陀螺信号的提取

田熙燕1,张春侠2,3,路静2,3

(1.河南科技学院,河南新乡453003;2.北京航天自动控制研究所,北京100854;3.宇航智能控制技术国家级重点实验室,北京100854)

针对激光陀螺输出信号中存在高频抖动分量的问题,采用数字滤波的方式对陀螺输出信号进行了FIR低通滤波,并且将鉴相、计数、锁存、作差、低通滤波等信号处理功能集成在一片FPGA芯片内,缩短了处理时间,提高了系统的集成度.通过激光陀螺信号处理系统静态测试验证了系统功能的正确性,滤波器具有很高的精度和稳定性.

激光陀螺;数字滤波;静态测试

50型二频机械抖动激光陀螺是一种基于Sagnac效应的惯性仪表,其输出信号中除了有效的惯性输入角速度分量外,还含有一些抖动的高频信号成分.因此,在陀螺的输出信号中,要实现陀螺信号的解调就必须滤除抖动信号的高频成分[1].常用的方法有整周期计数和数字滤波两种.整周期计数由于输出结果是每一个机械抖动周期变化一次,因此系统响应速度慢,无法满足角速度快速变化的应用场合.数字滤波响应速度快,每一个采样周期产生一个输出.目前,采用数字滤波方式滤除抖动信号高频信号的应用更多一些.

工程上对激光陀螺的滤波一般采用软件滤波的方式[2],软件滤波存在滤波时间长,系统延迟大等不足.针对该问题,本文对50型激光陀螺信号进行数字低通FIR硬件滤波,且将鉴相、计数、锁存、作差、低通滤波等功能集成在一片FPGA芯片内,减小了滤波时间和系统延迟,并提高了系统的集成度,降低了系统的功耗.

1 FIR低通滤波器MATLAB设计

1.1 FIR滤波器的基本原理

数字滤波器中,采用FIR滤波器,可以随意设计幅度特性,同时保证精确和严格的线性相位;另外,FIR滤波器的单位脉冲响应是有限长序列,因此没有不稳定的问题;其次,由于FIR滤波器一般为非递归结构,因此在有限精度运算下,累计误差较小[3].

对于许多应用来说,数字滤波器一般具有如下差分方程

式(1)中:x(n)为输入序列,y(n)为输出序列,a(k)和b(k)为滤波器系数,N是滤波器的阶数.式(1)中,若所有的b(k)均为零,则有

式(2)就是FIR滤波器的差分方程.因为FIR滤波器具有上述优点,因此选择FIR滤波器进行陀螺信号的滤波处理.

1.2 FIR低通滤波器在MATLAB中的设计

设计中采用Matlab7.0的FDATool工具实现FIR滤波器的设计.FDATool是很好的界面化滤波器设计工具[4],需要根据系统需求设置滤波器的通带频率、截止频率以及带外抑制等参数,可以直观地得到滤波器的频率响应曲线、脉冲响应特性和系数等.FDATool设计产生的系数可以在FPGA编译软件FIR Compiler中直接调用,应用起来十分方便.

激光陀螺惯性输入角速率有效信号在100Hz以下,而陀螺机械抖动以及其它随机噪声频率在300Hz以上,因此需要设计一个低通FIR滤波器来实现陀螺信号的解调,将100 Hz以下信号保留而将300 Hz以上信号滤除.设计中采用具有很大灵活性的Kaiser窗来设计滤波器,其中采样频率4 kHz,通带截至频率100 Hz,阻带截至频率300 Hz,通带最大衰减2 dB,阻带最小衰减50 dB,将获得的59阶滤波器系数按照每个系数一行的形式存放至filter coefficient.txt文件中[5].

2 激光陀螺信号处理系统设计及FPGA实现

2.1 激光陀螺信号处理系统方案

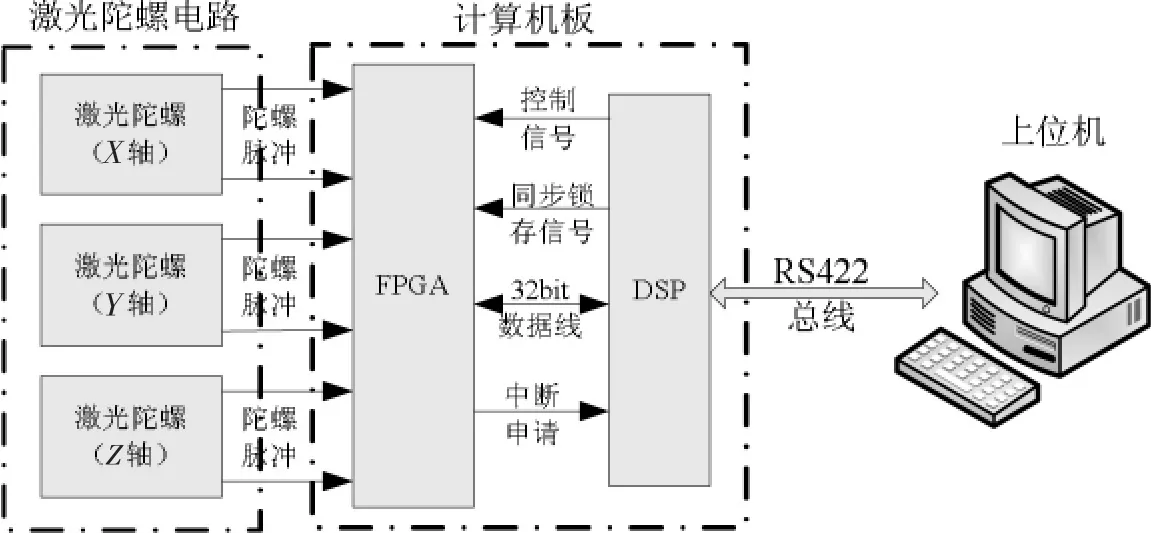

激光陀螺信号处理系统主要由3部分组成:激光陀螺电路、计算机板和上位机.如图1所示.

图1 系统组成Fig.1 Composition ofthe system

X、Y、Z三个轴向的激光陀螺电路主要敏感地球自转角速度,其输出除了有效信号外还包含因为防止闭锁引入的抖动分量以及部分高频噪声;计算机板采用FPGA加DSP架构,主要在FPGA内部对激光陀螺电路的输出脉冲信号进行鉴相、计数、滤波处理,处理结束后将衡量角速度变化的脉冲计数结果由DSP通过RS422总线输出至上位机;上位机主要进行陀螺解调性能的统计和显示[6].

2.2 陀螺信号在FPGA内部处理流程

以X轴的陀螺信号处理为例,内部功能结构组成和信号流向参见图2.

图2 FPGA内部程序结构Fig.2 The internal programblock diagramofFPGA

激光陀螺电路输出经过调制后的两路TTL电平的脉冲信号,首先需要通过鉴相模块将其解调为代表陀螺正负方向的脉冲信号,随后使用同一个时钟的上升沿进行整形,计数器模块对整形后的脉冲信号进行递减计数、按照4 kHz的采样周期进行锁存、锁存完成后单路作差得到4 kHz内的脉冲数、后续正负通道作差获得X轴的陀螺数据,最后经过FIR低通滤波滤除多余的抖动和噪声后得到所需的惯性输入角速度信息.累加器的主要功能是将4 kHz的脉冲数进行累加,从而减少向DSP申请中断的次数,累加到一定周期(如20 ms)时向DSP申请中断,由DSP进行数据读取并通过RS422串口输出至上位机进行结果统计和显示.

其中FPGA和DSP共用同一个时钟源,确保二者时钟同步,采样信号4 kHz由DSP定时器时钟输出.

设计中将上述功能集成在一片FPGA芯片中,片内程序主要包括:陀螺信号鉴相、整形、计数、4 kHz锁存、单通道正负脉冲作差、FIR滤波、20 ms累加、与DSP接口控制等几个功能单元.

2.3 FPGA内部FIR滤波器实现过程

本文采用Altera公司FPGA芯片EP2C35F484I进行电路设计,在Quartus II 12.0开发环境中实现上述功能设计.Quartus II 12.0提供了大量的IP核供用户使用,其中包括FIR滤波器的IP核,本文应用FIR Compiler v12.0完成FIR滤波器设计.

主要设计过程包括下面5步:

(1)参数设计.进行FIR滤波器设计时,通过MATLAB计算出的固定系数都是浮点数,必须将系数量化后再用作IP核处理,量化倍数可以根据精度的需要和占用位数折中选择,在本文设计中量化倍数选择65 536,将filter coefficient.txt文件导入参数设计操作界面,就会自动生成需要的定点系数,由定点系数参与FIR滤波器处理.滤波结束后对滤波结果除以量化倍数65 536便可得到最终的脉冲计数结果.

FIR Compiler v12.0提供4种结构的FIR IP核,完全串行滤波器,多位串行滤波器,完全并行滤波器,可变参数滤波器,每种滤波器各有其优缺点,本文设计选择串行滤波器结构进行设计,其占用逻辑资源最少.

设计中选择单通道、单速率串行滤波器进行设计,经过计数、锁存得到的4 kHz采样周期的陀螺脉冲数为16 bit,量化倍数65 536为16 bit,根据FIR滤波器参数设计公式得到的滤波结果为33 bit,由于DSP的数据位宽为32 bit,因此需要对滤波结果进行截断处理,取低32 bit有效值输出得到一个采样周期的滤波结果.

(2)产生仿真文件.产生仿真需要的仿真模型文件,仿真用Testbench文件以及MATLABM文件.

(3)生成FIRIP核VHDL代码.参数设置以及模型文件生成后,点击生成代码,就会生成设计的FIR VHDL代码.最后生成的FIR IP核输入输出接口参如图3所示,和前后模块之间的输入输出对应关系参见图2.

(4)顶层调用完成系统构建.在加入FIR IP核VHDL代码的工程中,增加鉴相、整形、计数、4 kHz锁存、单通道正负脉冲作差模块的VHDL代码,并且按照图4所示的时序关系,编写顶层文件代码完成FIR IP核的调用和滤波完成后输出数据的读取,最后再进行20 ms累加,完成与DSP的接口控制.

图3 FIR IP核管脚配置Fig.3 The pin configuration ofFIR IP

图4 FIR IP核信号时序关系Fig.4 The sequence diagramofFIR IP

(5)仿真验证与代码下载.将上述编译链接完成的工程进行仿真,确认达到设计要求后,将可执行代码下载至芯片EP2C35F484I器件中进行系统级功能测试.

3 激光陀螺信号系统的解调功能验证

在静态情况下,利用上述激光陀螺信号处理系统对陀螺的输出解调性能进行测试,在上位机中进行数据分析和波形绘制,其中X轴的上位机测试结果如图5所示,左图为FIR滤波完成后20 ms累计的陀螺脉冲数,右图为10 s累计的脉冲数.

图5 X轴的上位机测试结果Fig.5 PCtest results ofthe X axis

试验过程中通过更改FPGA和DSP程序,采用DSP进行了FIR软件滤波精度测试,与FPGA硬件滤波进行了对比,测试结果参见表1.

表1 DSP软件滤波与FPGA硬件滤波测试结果Tab.1 The test results ofDSP software filteringand FPGAhardware filtering

由表1可以看出,由于滤波系数的取整问题,FPGA硬件滤波比浮点DSP软件滤波的精度稍差,但是整体上可以与软件滤波的精度相当;同时硬件滤波占用的时间明显小于软件滤波的时间,大大缩短了系统延迟.

4 小结

本文首先采用Matlab的FDATool工具进行了针对激光陀螺滤除机械抖动信号的FIR滤波器设计,并采用FPGA芯片进行了包括鉴相、整形、计数、FIR滤波、累加等陀螺信号处理过程的实现,最终搭建测试系统对软件滤波和硬件滤波结果进行了静态测试和比对,结果表明该滤波器具有很高的精度和稳定性,相比软件滤波缩短了时间,保证了精度.

[1]高伯龙,李树棠.激光陀螺[M].长沙:国防科技大学出版社,1984.

[2]张永瑞,李锦明,苏树清.基于FPGA和DSP的激光陀螺信号处理电路设计[J].中国测试,2014,40(2):110-113.

[3]廖红华,吴长坤,廖宇,等.基于广义形态滤波的低电压芯片电泳电色谱信号去噪研究[J].湖北民族学院学报:自然科学版,2014,32(4):439-444.

[4]林一超,米国鑫,刘泽华,等.基于FPGA的FIR滤波器设计[J].电子世界,2014(3):136.

[5]温锋,李锦明.基于FPGA的激光陀螺信号高速解调滤波设计[J].电子技术应用,2014,40(1):90-96.

[6]高黎明,乐晋.基于以太网络接口的激光陀螺信号处理电路设计[J].计算机与数字工程,2011(2):187-189.

(责任编辑:卢奇)

The extraction of laser gyro signal based on FIR digital filtering

TIAN Xiyan1,ZHANG Chunxia2,3,LU Jing2,3

(1.Henan Institute ofScience and Technology,Xinxiang453003,China;2.BeijingAerospace Automatic Control Institute,Beijing100854,China;3.National KeyLaboratoryofScience and Technologyon Aerospace Intelligence Control,Beijing100854,China)

Aiming at the problem of high frequency jitter in the laser gyro output signal,with the method of digital filtering,the gyro output signal has been processed using a FIR low-pass filter.And the phase detecting,counting,latches, making a difference,low-pass filtering such as signal processing function were all integrated in one FPGA chip.The processing time was shorted and the integration of the system was increased.Through static testing of the laser gyro signal processing system,the system function was verified,a high accuracy and stability of the filter was also proved.

laser gyro;digital filtering;static test

TN911.72

A

1008-7516(2015)06-0057-05

10.3969/j.issn.1008-7516.2015.06.011

2015-10-14

田熙燕(1980―),女,河南舞阳人,硕士,讲师.主要从事信号处理研究.