烧结条件对Co2O3掺杂ZnO基陶瓷压敏电阻电性能的影响

2015-03-27徐卓杨昌平杨闰高鹏

徐卓,杨昌平,杨闰,高鹏

(湖北大学物理与电子科学学院,湖北武汉430062)

0 引言

ZnO压敏电阻是一种多功能新型陶瓷材料,以ZnO为主体,添加若干其他氧化物改性的烧结体材料. ZnO压敏电阻具有非线性系数高、响应时间快、漏电流小、制造成本低廉等优点,广泛应用于电子通信、集成电路以及其它领域[1].低压压敏电阻主要用于半导体器件的过压保护,在电路中与用电器并联,当工作电压正常时,其电阻值很高,仅允许微安级的漏电流通过,对电路设备几乎没有影响;当工作电压过载时,其阻值急剧下降,电流迅速增大,从而保护了与之并联的电气设备免受过电压的损坏,对提高电子电器设备的可靠性和安全性起到了重要作用[2].

最早的压敏陶瓷是20世纪30年代初期由贝尔实验室制成的SIC陶瓷,之后分别出现了SrTiO3基和TiO2基电容—压敏双功能陶瓷材料.1968年Matsuoka发现了一种新型陶瓷材料—ZnO压敏电阻器,由于具有优异的性能从而大量取代了其他陶瓷材料[3].ZnO压敏电阻的非线性是一种晶界现象,晶界势垒导致材料的非线性,添加各种氧化物可以使杂质在晶界处偏析或扩散,使其变为活性晶界[4].Bi2O3的存在是ZnO压敏陶瓷产生非线性的基础及必备条件,压敏陶瓷的非线性本质上并非产生于Bi2O3,但Bi作为晶界激活剂,能使其他过渡金属氧化物向晶界偏析.TiO2作为一种晶粒生长促进剂,在烧结过程中可以有效地促进晶粒长大,降低压敏电压,其作用机理在于固相传质[5].Co2O3常作为ZnO压敏陶瓷非线性改善的主要添加剂.在烧结过程中,Co2O3部分固溶于ZnO晶粒中,而在烧结后冷却过程中,以Bi2O3为主要成分的晶界溶液中所含的Co成分偏析于晶界层,因而提高晶界的势垒高度,提高非线性[6].MnO2和Co2O3的掺杂具有共性,Driear等人研究发现,压敏陶瓷中同时添加Mn和Co时的综合电性能优于单独添加Co时的综合电性能[7].上述氧化物掺杂已有很多学者做了深入的研究,但Co2O3对ZnO-Bi2O3-TiO2-MnO2体系的掺杂,以及烧结条件与压敏陶瓷电性能之间的关系的研究并不多见.本实验中通过掺杂不同份量的Co2O3证明Co掺杂对非线性的贡献,并研究不同烧结温度和烧结时间对压敏陶瓷电性能的影响,获得压敏参数良好的低压压敏陶瓷.

1 实验方法

本实验中采用传统固相反应法制备ZnO陶瓷样品.原料为分析纯的ZnO、Bi2O3、TiO2、Co2O3和MnO2.其中Bi2O3、TiO2、MnO2用量(按占总物质的摩尔分数计,下同)分别为0.7%、1.0%、0.5%,Co2O3的掺杂量分别为0%、0.5%、1.0%、1.5%,按化学计量比称取,以无水乙醇为溶剂,ZrO2球为球磨介质,在球磨机中以300 r/min的速度球磨24 h,取出后于100℃烘干12 h,750℃预烧2 h.粉末在10 MPa下压制成直径约10 mm,厚度约1 mm的圆片,然后在1 100~1 300℃下分别煅烧2~12 h.将烧结好的样品经粗磨和细磨,两面涂银后于600℃下烧结30 min以获得接触良好的电极.

采用美国吉时利公司生产的2400型数字多用表(源表)测量样品的压敏电压梯度、漏电流密度、非线性系数和E-J特性;采用美国安捷伦公司6500B型阻抗分析仪对样品进行阻抗测量;采用德国BRUKER公司brukerd8-advance型X线仪对样品进行物相与结构分析;采用日本JEOL公司JSM-7100F型扫描电子显微镜观察样品的形貌.

2 结果与讨论

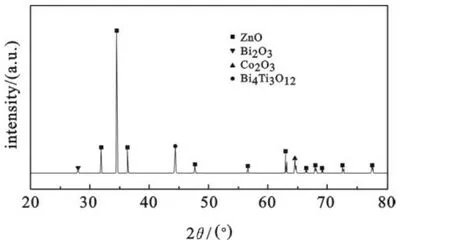

2.1 Co2O3掺杂对电性能的影响 图1为Co2O3掺杂ZnO压敏电阻的XRD图谱,陶瓷电阻中包含有Zn-Bi系压敏陶瓷的基本组成物相:ZnO主晶相、Bi2O3相、Co2O3相以及Bi4Ti3O12相.Bi4Ti3O12相为尖晶石相,会阻碍晶粒的正常生长.图中未出现Mn相,一方面由于它部分固溶于ZnO主晶相,部分固溶于晶界富铋相,另一方面由于它的含量较少.

图1 Co2O3掺杂ZnO压敏电阻的XRD图谱

首先研究Co2O3掺杂量对ZnO压敏电阻的电性能影响,烧结温度为1 200℃,烧结时间为5 h.图2为压敏电压梯度E1mA、非线性系数α和漏电流密度I与掺杂量的关系.由图2可以看出,没有Co2O3时,压敏场强较高,随着掺杂量的增加,压敏电压梯度逐渐减小,在1.0%时压敏电压梯度为29.6 V/mm,继续增加Co2O3的掺杂量,压敏电压梯度反而增大.这是由于Co代替Zn时为施主杂质,可以通过产生锌空位而得到补偿,从而促进扩散传质,有利于晶粒长大[8].压敏陶瓷的压敏电压可以表示为U1mA=(D/d)Ugb.Ugb为单个晶界的压敏电压,D为样品的厚度,d为晶粒的平均尺寸.平均晶粒尺寸越大,单位厚度的晶界数越少,压敏电压梯度越小[9].由于锌空位的产生有限,Co对ZnO晶粒长大的促进作用只在初期比较明显,再增加Co的掺杂量,压敏电压梯度反而增大.

由图2可以看出,随着掺杂量的增加,非线性系数α逐渐变大,在1.0%时达到最大为13.2,随着掺杂量进一步增至1.5%时,非线性系数迅速降至9.6.产生此种变化的原因与晶界势垒高度密切相关.通过测量样品的E-J特性,运用晶界势垒模型[10],依据公式J=A*T2exp[(βE12-φβ)/kT],式中J为热激发电流密度,A*为Richardson常数,E为电场强度,k为Boltzmann常数,β是与Schottky势垒宽度有关的常数,φβ是晶界势垒高度,计算得到不同Co2O3掺杂量在室温下的势垒高度,其结果如表1所示,晶界势垒的变化与非线性系数的变化一致.

图2 压敏电压梯度E1mA、非线性系数α及漏电流密度I与Co2O3掺杂量的关系

表1 不同Co2O3含量样品在室温下的晶界势垒高度

由图2还可以看出,漏电流密度I随着掺杂量的增加呈现先减小后增大的趋势,掺杂量为1.0%时漏电流密度最小为0.42 μA/mm2.其原因是晶界势垒的降低使漏电流有所增大,且Co2O3掺杂量较高时,晶粒的不均匀和大量气孔也导致漏电流密度上升.

综合比较可以看出,当Co2O3掺杂量1.0%时电性能最佳,此时压敏电压梯度E1mA为29.6 V/mm,非线性系数α为13.2,漏电流密度I为0.42 μA/mm2.

2.2 烧结温度对电性能的影响 烧结温度对ZnO压敏陶瓷的电性能有很大的影响[11].图3为样品烧结温度在1 100~1 300℃之间,烧结时间为2 h,Co2O3掺杂量为1.0(摩尔分数)时3参数的变化.结果表明随着烧结温度的升高,压敏电压梯度E1mA呈减小的趋势.这是因为烧成温度升高利于晶粒生长,导致最终的晶粒尺寸较大,降低压敏电压梯度.当温度超过1 200℃后,压敏电压梯度变化不大.非线性系数α随着烧结温度的升高先增大,在1 200℃时达到最大值15.4,之后迅速减小.这是由于过高的烧结温度导致Co、Bi等掺杂物挥发,使晶界势垒降低,导致非线性系数降低.漏电流密度I随着烧结温度的升高先逐渐减小,随后急剧增大,产生这种现象的原因是高温破坏了陶瓷样品组织结构的均匀性,增加内部气孔,使漏电流密度增大.

综合比较可以看出,烧结温度为1 200℃时,低压ZnO压敏电阻的电性能最佳,此时压敏电压梯度E1mA为30.3 V/mm,非线性系数α为15.4,漏电流密度I为0.25 μA/mm2.

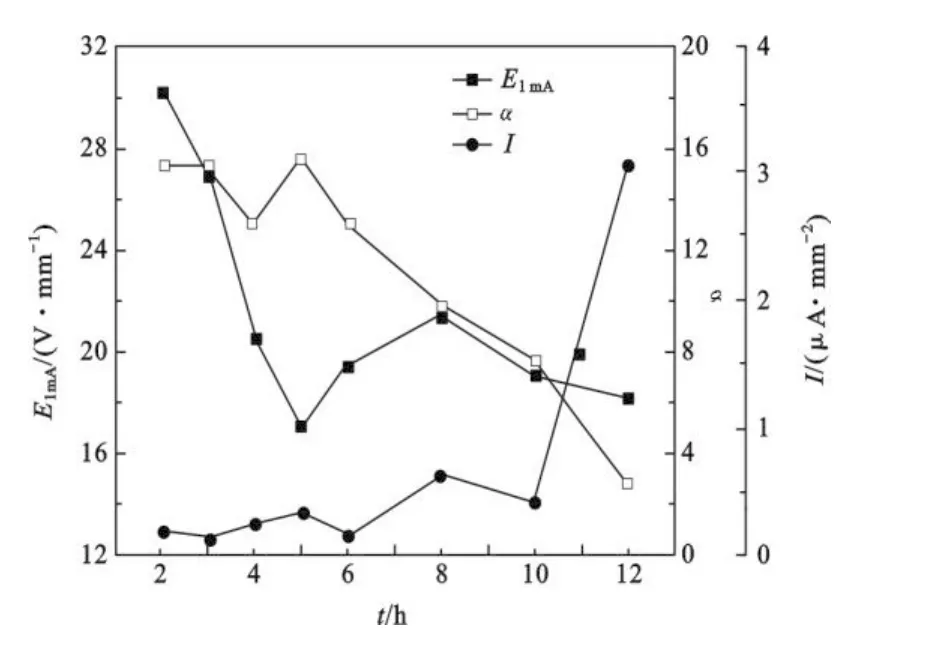

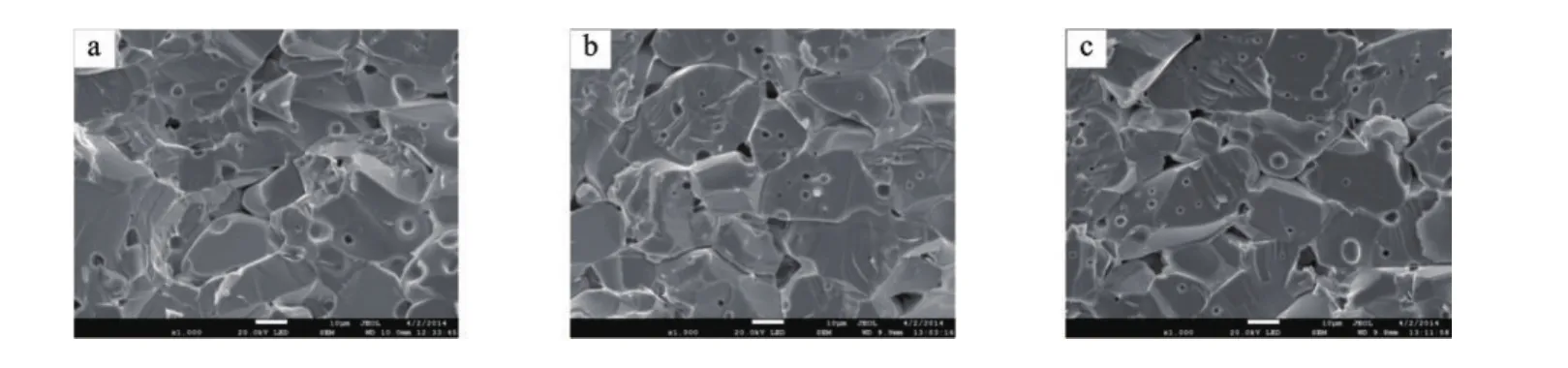

2.3 保温时间对电性能的影响 在1 200℃的烧成温度,Co2O3掺杂量为1.0(摩尔分数)的基础上,改变烧结时间分别为2、3、4、5、6、8、10、12 h.由图4可以看出随着烧结时间的增加,压敏电压梯度E1mA进一步减小,这是由于随着烧结时间的增加,晶粒进一步生长,降低压敏电压梯度;非线性系数α在烧结5 h后明显减小,过长的烧结时间导致Co、Bi等掺杂物挥发更多,致使晶界势垒降低,非线性系数减小;漏电流密度I在烧结6 h后明显增大,烧结时间过长同样会破坏样品组织结构的均匀性,增加内部气孔,使漏电流密度增大.对不同烧结时间的样品进行电子显微镜扫描观察其形貌,随着烧结时间的增加,样品的平均晶粒尺寸依次为7.5 μm、10.2 μm、14.3 μm、24.4 μm、16.8 μm、13.5 μm、14.7 μm、15.8 μm.图5为不同烧结时间样品的扫描电镜照片,可以看出样品晶界清晰可见,平均晶粒大小随着烧结时间逐渐增大,在烧结时间超过5 h后变化不大,与图4中压敏电压梯度的变化相符合.另外,烧结5 h时样品晶粒内部气孔最小,数目最少.综合考虑低压压敏陶瓷的电性能参数可以看出样品烧结时间为5 h时电性能最佳,此时压敏电压梯度E1mA为17.1 V/mm,非线性系数α为15.7,漏电流密度I为0.34 μA/mm2.

图3 压敏电压梯度E1mA、非线性系数α及漏电流密度I与烧结温度T的关系

图4 压敏电压梯度E1mA、非线性系数α及漏电流密度I与烧结时间t的关系

图5 不同烧结时间4 h(a)、5 h(b)、6 h(c)时样品的扫描电镜照片

图6为保温5 h时样品的I-V特性曲线.开始加电压时,流过样品的电流很小,这是由于ZnO压敏陶瓷晶界电阻很大,外加电压为小电压时晶界势垒未能被击穿,陶瓷样品表现为大电阻;当外加电压超过压敏临界电压,晶界势垒被击穿,只有晶粒内禀电阻时,电流迅速增大,陶瓷样品表现为小电阻,并可以由斜率算出击穿后的样品电阻约为48 Ω.

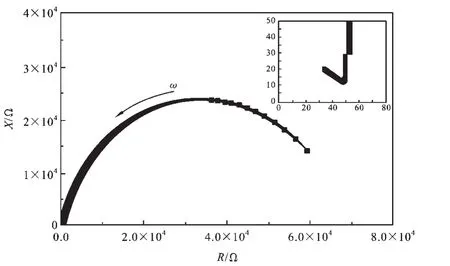

复阻抗图可以准确地反映陶瓷内部不同区域的电学性能[12].图7为保温5 h时样品的复阻抗图.由于测试温度较低时,无法得到完整的复阻抗图,为了更好地揭示ZnO压敏陶瓷压敏性能产生的内部导电机理,将样品放在450 K的测量温度下,频率在20~15 MHz之间.样品的复阻抗图呈现半圆弧,低频端在实轴上的交点表现为晶界电阻,大约为70 KΩ;高频端在实轴上的交点非常小,代表晶粒电阻,大约为50 Ω,与I-V特性曲线图上算得的电阻值一致.

图6 烧结5 h时样品的I-V特性曲线

图7 烧结5 h时样品的复阻抗曲线

3 结论

1)采用固相反应法制备Co2O3掺杂ZnO系列低压压敏电阻,当Co2O3掺杂量为1.0(摩尔分数)、烧结温度为1 200℃、烧结时间为5 h时过压保护综合性能最好,其压敏电压梯度E1mA为17.1 V/mm,非线性系数α为15.7,漏电流密度I为0.34 μA/mm2.

2)ZnO压敏陶瓷电阻由晶粒界面电阻和晶粒内禀电阻组成,当外加电压低于临界电压时,样品表现为大电阻,主要由界面电阻贡献;当外加电压高于压敏临界电压时,界面被击穿,表现为晶粒内秉电阻特性.

[1]Gupta T K.Application of zinc oxide varistors[J].J Am Ceram Soc,1990,73(7):1817-1840.

[2]周东祥,张绪礼,李标荣.半导体陶瓷及应用[M].武汉:华中理工大学出版社,1989:32-70.

[3]Matsuoka M.Non-omic properties of zinc oxide ceramics[J].Jpn J Appl Phys,1971,10(6):736-746.

[4]王振林,李盛涛.氧化锌压敏陶瓷制造及应用[M].北京:科学出版社,2009:15-28.

[5]Varela J A,Poleti D.Structural and electrical properties of ZnO varistors containing different spinel phases[J].Ceramics International,2001,27(1):115-122.

[6]许业文,何忠伟,徐政.Co2O3和MnCO3掺杂对低ZnO压敏电阻电性能的影响[J].材料科学与工程学报,2005,23(4):525-528.

[7]Smcki F,Greuter F.Key role of oxygen at zinc oxide varistor grain boundaries[J].Appl Phys Lett,1990,57(5):446-448.

[8]Kutty T R N,Ezhilvalavan S.The influence of Bi2O3nonstoichiometry on the nonlinear property of ZnO varistors[J].Mater Chem Phy,1994,38:267-276.

[9]Chun Ying-Chung,Shen Chi-Yen.Grain growth and electrical properties in ZnO varistors with various valence states of additions[J].Jpn J Appl Phys,1991,30(1):84-90.

[10]Pianaro S A,Bueno P R.Effect of Bi2O3addition on the micro structure and electrical properties of the SnO2,CoO,Nb2O5,varistor system[J].J Mater Sci Lett,1997(16):634-638.

[11]Wang M H,Hu K A.Electrical characteristics and stability of low voltage ZnO varistors doped with Al[J].Materials Chemistry and Physics,2006,100:142-146.

[12]Andres V M,West A R.Impedance and modulus spectroscopy of ZnO varistors[J].Journal of Electroceramics,1997,1(2): 125-132.