基于Nios Ⅱ嵌入式处理器的SOPC中精度测频电路的设计

2015-03-10董建树袁晓宇严宗瑞

董建树,袁晓宇,王 惠,严宗瑞

(1.北京自动化控制设备研究所,北京100074;2.北京振兴计量测试研究所,北京100074;3.海军指挥学院,南京210016)

基于Nios Ⅱ嵌入式处理器的SOPC中精度测频电路的设计

董建树1,袁晓宇1,王 惠2,严宗瑞3

(1.北京自动化控制设备研究所,北京100074;2.北京振兴计量测试研究所,北京100074;3.海军指挥学院,南京210016)

中精度频率测量电路主要用于中精度石英振梁加速度计频率输出的二次测量。通过比较并选择合适的测量方法,详细地分析了方案的理论误差,研究基于Nios Ⅱ嵌入式处理器的测频电路,将数据采样和运算单元都集成在FPGA芯片中,形成一个片上操作系统SOPC,获得了较高精度的测量结果。

测频;FPGA;嵌入式处理;SOPC

0 引言

石英振梁加速度计是一种力敏感梁式谐振器约束的线性加速度计,其产生的谐振频率表示为惯性系统的输入加速度的函数。中精度频率测量电路主要用于中精度石英振梁加速度计频率信号输出的二次测量,它将测量结果反馈给导航计算机。

由于石英振梁加速度计的标度因数较小,只能通过专用的测量电路进行精确的测量。在以前的设计方案中,一般通过数字逻辑电路与微处理芯片共同组合,实现要求的功能,很显然,系统的集成程度不高,甚至无法满足高速电路设计的要求。

这里提出一套新的基于Nios Ⅱ嵌入式处理器的SOPC中精度测频电路方案,可以将设计中几乎所有的逻辑模块、运算模块、控制模块都高度集成在一片FPGA中,最大限度地减少了外围电路的使用,同时片上可编程系统(SOPC)还具有设计周期短、开发成本低、设计灵活的优点。

1 测频方案的选择

频率测试有很多种方法,目前常用的有四种方法:测频法、测周期法、等精度法和相检法。传统的测频法和测周期法在实际应用中具有较大的局限性,并且对被测信号的计数始终存在±1个字的误差,测试精度与计数器中记录的数值量相关,记录数据越少,精度越低。所以,这两种测试方法不能满足较高精度的要求。

相检法通过检测信号的相位重合点,不仅实现了对被测信号的同步,也实现了对标频信号的同步,大大消除了一般测频系统中的±1个字的计数误差。但是,当待测信号和标准信号的频率值相等或成整数倍或分数倍的关系时,一旦两信号有相位差,就不会有相位重合的时刻,则测量进程陷入死胡同。

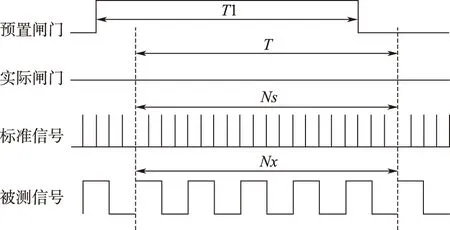

等精度测频法中,由实际闸门控制两个计数器分别对标准信号和被测信号同时计数,通过两个计数器计数值之间的比较,计算得到被测频率。实际闸门由根据测试需要设置的预置闸门经被测信号同步后形成,测量过程中,由于实际闸门与被测信号完全同步,消除了被测信号的±1个字的误差,误差的来源只有标准信号本身以及其计数误差。

其基本原理如图1所示。

图1 等精度测频原理时序图Fig.1 The timing scheme of equallyaccurate frequency measurement

综合考虑采用等精度频率测量法,它能够消除对被测频率信号计数所产生的误差,实现了宽频率范围内的中精度测量[1]。在设计中充分考虑引起误差的各种因素,尽量将其降低到适当范围,以满足中精度的要求。

2 等精度测频法的误差分析

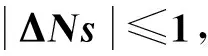

如果在一次实际闸门时间T中,计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。标准信号的频率为fs,则被测信号的频率为

(1)

由式(1)可知,若忽略标频fs的误差,则等精度测频可能产生的相对误差为

(2)

其中,fxe为被测信号频率的准确值。

(3)

将式(1)和式(3)代入式(2),并整理得

(4)

由式(4)可知,测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关,这样就实现了整个测试频段的等精度测量。

闸门时间越长,标准频率越高,测频的相对误差就越小。标准频率可由稳定度好、精度高、频率高的晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。

前面将标频信号作为一个稳定的常数,忽略了标频fs的误差,这里将它考虑进去综合推导。

对式(1)进行微分得到被测频率的误差为

(5)

(6)

由式(6)可知,测量频率的相对误差与标准频率的数值、准确度以及闸门时间相关。在硬件电路中,实际闸门时间T的准确度是与晶振频率的准确度息息相关的,标准频率信号也是直接或间接地来自晶振频率。

3 片上系统的Nios Ⅱ软核设计

当前嵌入式系统发展朝着小体积、低功耗、高性能的趋势发展。MCU、DSP、FPGA三种处理器的结合是未来嵌入式系统发展的趋势,可编程片上系统SOPC可以将三者完美结合起来。一般采用大容量FPGA作为载体,在片上定制MCU处理器和DSP功能模块,同时设计其他逻辑功能模块。NiosⅡ系统为用户提供了最基本的IP核,设计师可以用它裁减合适的嵌入式系统。

NiosⅡ处理器是指在一个芯片上包含一个或多个可配置的CPU软核、与CPU相连接的片内外设和存储器以及与外设相连的接口等,所有的组件在一个FPGA上实现。NiosⅡ处理器具有定制指令、灵活的外设配置与地址映射、自动创建系统等特点,极大地提高了系统性能。

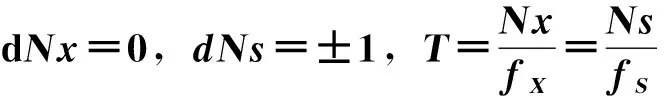

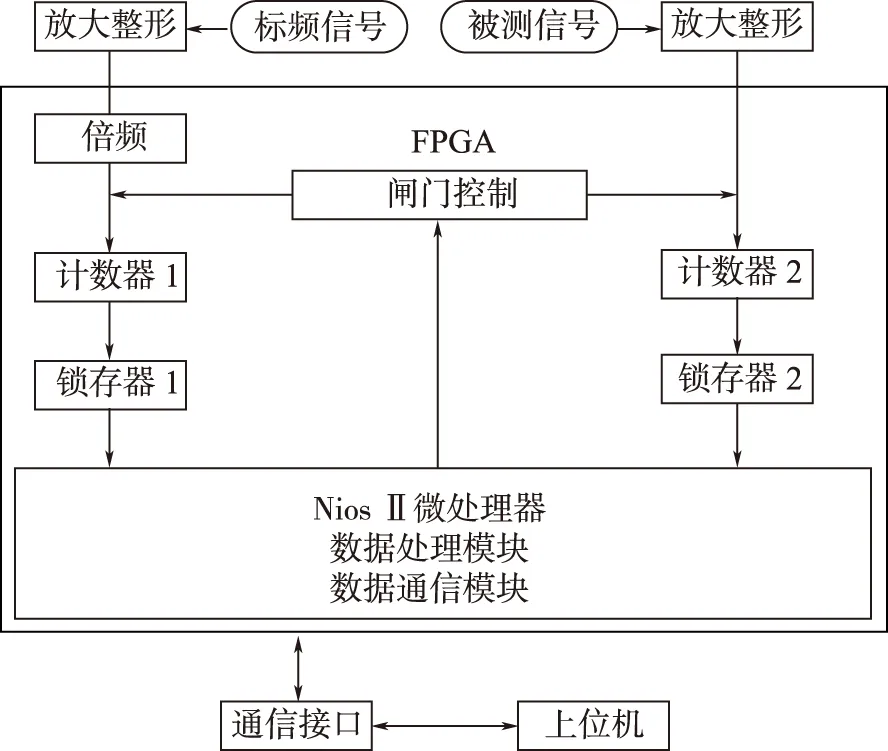

测频电路的核心设计是SOPC片上可编程系统的设计,NiosⅡ软核是片上系统的核心内容[2],测频电路的原理如图2所示。通过对FPGA芯片进行编程,能够实现九路信号的计数、运算处理、串口通信三大复杂的功能。

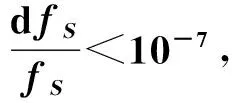

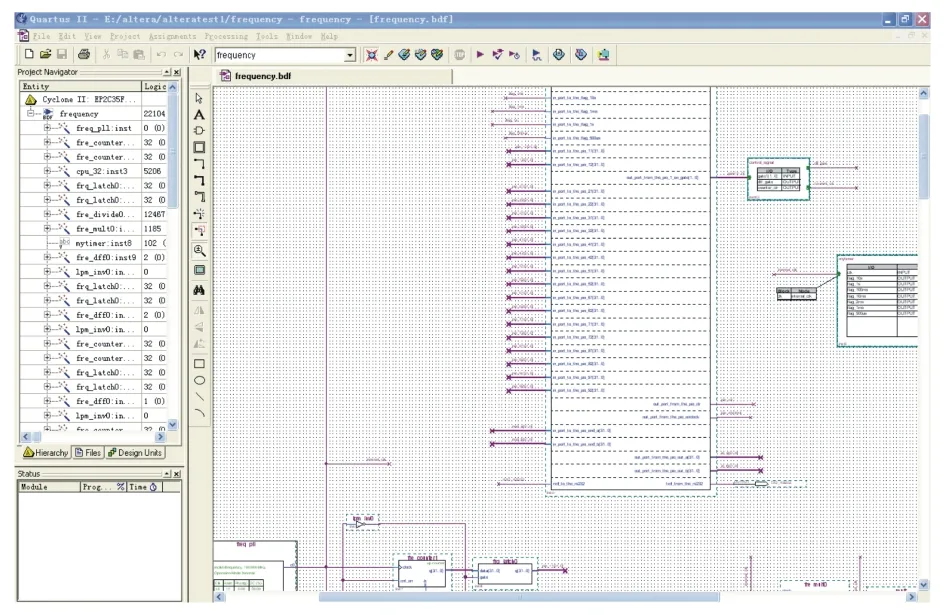

采用QuartusII软件进行FPGA的硬件设计如图3所示。标准频率信号从外部的时钟输入端倍频后获得,经过整形后的被测信号输入到触发器中。NiosⅡ软核控制预置门信号为高电平时,被测信号的上升沿通过触发器的输出端,启动计数器计数;当预置门信号为低电平时,计数器关闭。随后将数据送入乘除法器中进行运算,结果通过UART外设输出。通过对实际数据容量的理论分析,设计采用了宏功能模块来实现32位硬件乘法器和96位的硬件除法器。

图2 测频电路原理框图Fig.2 The functional block diagram of frequency measurement circuit

图3 FPGA的硬件设计图Fig.3 The hardware design scheme of FPGA

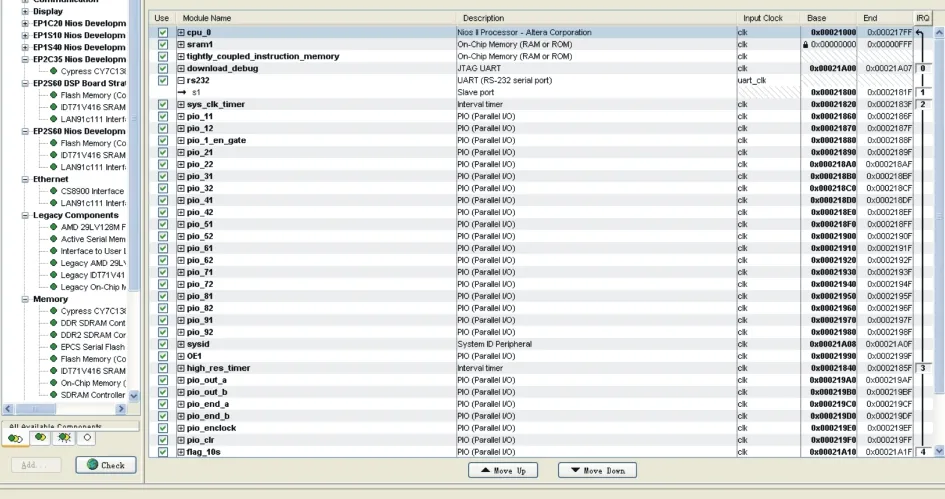

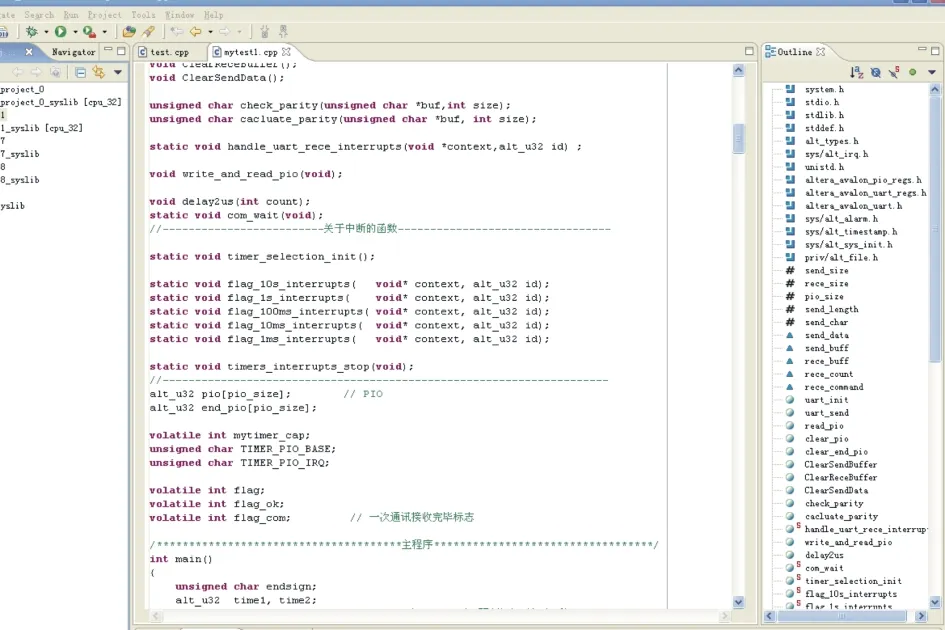

NiosⅡ作为一个可灵活定制的32位CPU,它的外设是可选的IP核或自定制逻辑[3],我们根据系统设计要求,通过SOPCBuilder向导式的界面定制裁减得当的SOPC系统。完整的基于NiosⅡ的SOPC系统作为一个软硬件复合的系统,在开发时可以分为硬件、软件两部分,如图4和图5所示。

图4 Nios Ⅱ硬件设计图Fig.4 The hardware design scheme of Nios Ⅱ

图5 Nios Ⅱ软件设计图Fig.5 The software design scheme of Nios Ⅱ

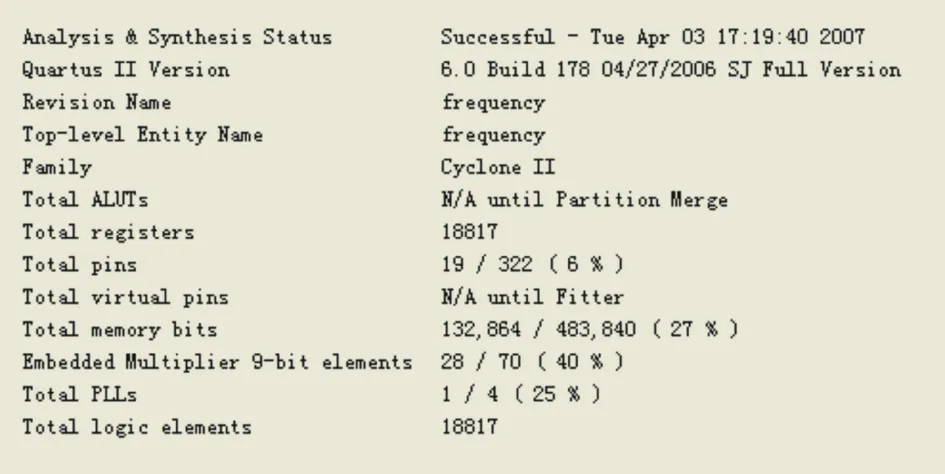

在NiosⅡ的开发流程中,我们首先使用SOPCBuilder系统综合软件来选取合适的CPU、存储器以及外围器件,并且定制相应的功能;然后使用QuartusⅡ软件选取可编程器件,对生成的HDL设计文件进行布局布线,并对NiosⅡ系统上的I/O口分配管脚、编译,综合生成一个适合目标器件的网表作为配置文件;最后,使用编程器和下载电缆将配置文件下载到开发板上。FPGA工程的编译报告如图6所示。

图6 FPGA工程的编译报告Fig.6 The compile report of FPGA project

4 测频电路的硬件实现

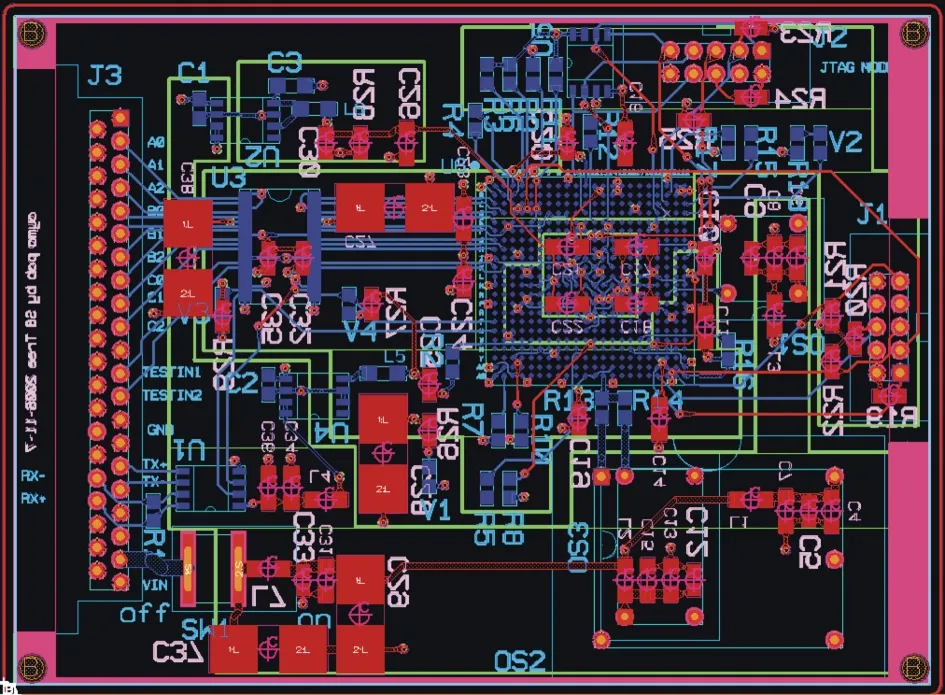

利用高端复杂电路设计软件ExpeditionPCB设计的电路板,如图7所示。同时采用信号完整性分析软件对电路板图进行了高速信号的串扰、EMC等分析,预先确保了电路板设计质量[4]。

图7 高端复杂电路设计软件Expedition PCB设计的电路板图Fig.7 The circuit PCB scheme designed by advanced circuit design software Expedition PCB

样机为一块专用测频电路板,按照功能可以分为:晶体振荡器、输入信号电平转换器、闸门发生器、计数器、乘法器、除法器、数字信号处理软核、通信接口以及电源管理系统[5]等模块。

其中,晶体振荡器作为标准频率源和FPGA工作的全局时钟;电平转换器起到电平转换和整形驱动的作用;锁存器锁存九路标频和被测频率的计数值;闸门发生器用于信号同步;乘法器/除法器用于数字运算;数字信号处理软核进行数据处理、计数控制及通信处理,依据上位机的命令,将采样结果通过通信串口传输给外部系统。电源管理系统给电路板分别提供5V、3.3V和1.2V三种电压。

另外,设计不仅采用了新器件,而且大量地采用了新的软件,包括FPGA设计软件QuartusII系列(NiosⅡ、SignalTapII)、高端复杂电路设计软件ExpeditionPCB系列(DxDesigner、ExpeditionPCB、I/ODesigner)、信号完整性分析软件HyperLynx[6]。其他小软件如串口调试助手、BorlandC++Builder等,这些先进的开发软件都为电路设计提供了极大而有效率的帮助[7]。

5 试验与分析

在试验中,采用高精度的铷原子钟WX-10标准频率源做对比试验。铷原子钟准确度为5×10-9。将频率标准的三路输出信号随机接入(并记录)测频电路的九路输入端,分别进行0.1Hz、1Hz、10Hz采样频率的测试。在通电2s后开始采数。在0.1Hz、1Hz、10Hz采样频率下,现场至少测试15min,并提交调试阶段测试的数据。测试完成后,用Excel绘制曲线图,进行精度和稳定性分析。

在每个采样频率下,对每通道数据求均值,该均值与频率真值的相对误差作为该通道的测频准确度。对每通道数据求标准偏差,标准偏差与测频真值之比作为该通道的测频稳定性。

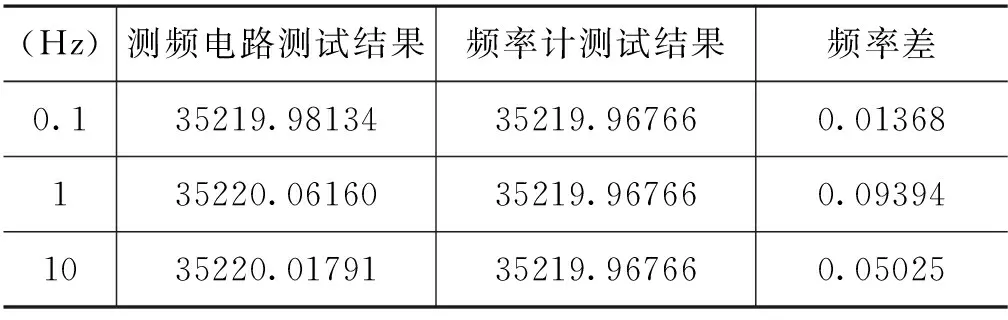

取第一通道的测试均值与安捷伦5312A频率计测得的结果进行对比,如表1所示。

表1 加速度计测试结果对比Tab.1 The test results contrast of accelerometer

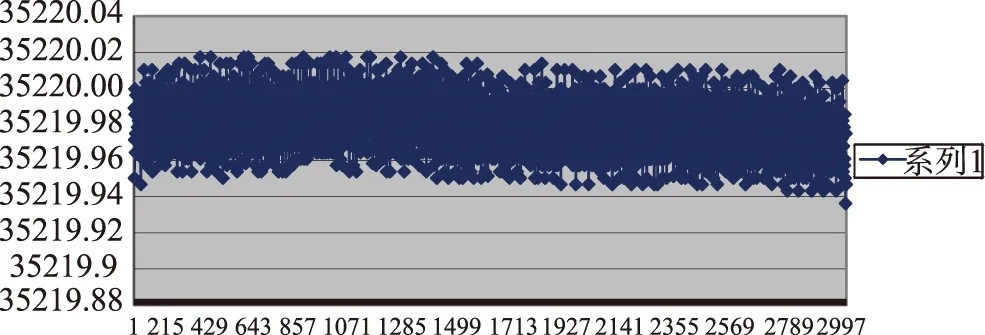

加表的第一通道输出,10Hz采样频率下的测试曲线如图8所示。

图8 加表的第一通道输出的测试曲线Fig.8 The test curve of the firstchannel output for accelerometer

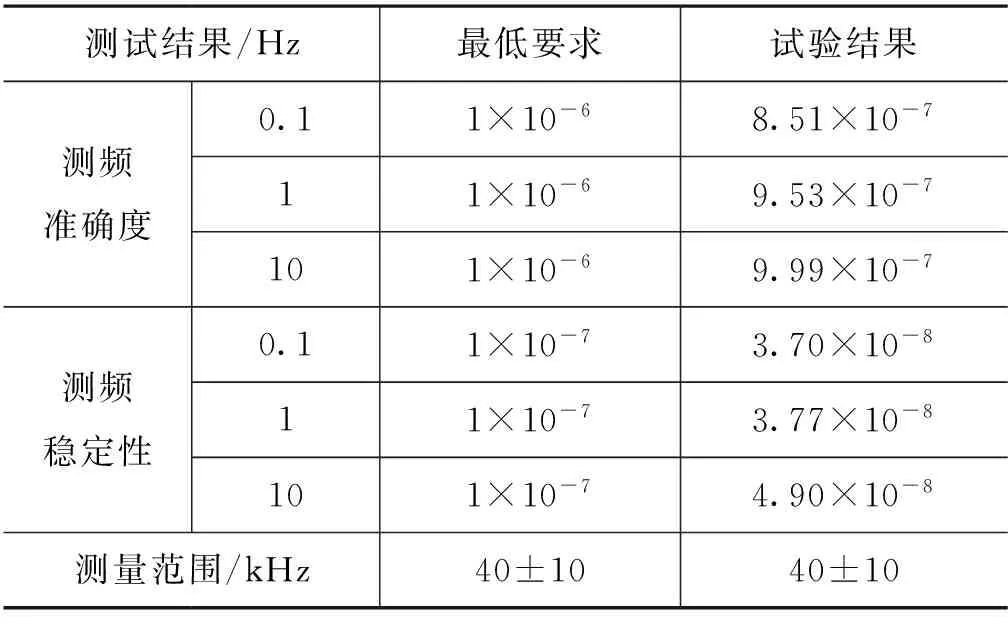

对测量精度进行了分析和计算,获得以下对比的结果如表2所示。

表2 测试结果Tab.2 The test results

结果表明,该测频电路实现了九路通道输入,测频范围25~50kHz,输出接口为RS422方式,测频精度满足指标要求,采样频率实现了输出数据的速率有1次/10s、1次/s、10次/s三挡的要求。与振梁表联调,在1Hz采样时,不同通道的测试结果一致性好。

6 小结

通过研究与试验,基于Nios Ⅱ嵌入式处理器的SOPC中精度测频电路具有以下的特点:

(1)测频电路系统的高度集成化

方案设计中,在一片FPGA内部集成了所有的逻辑模块、运算模块、控制模块、UART软核等,几乎实现了信号采集、数据处理、通信协议等全部功能,最大限度地减少了外围离散电路的使用,这也是未来嵌入式系统发展的趋势。

(2)设计软件的高端复杂化

使用高端复杂电路设计软件进行BGA封装设计,采用BGA球栅阵列的封装形式芯片,进行电路板制板。另外,PCB厂家只能获得Gerber文件和钻孔文件,这样也提高了设计文件的保密性。

(3)较高的频率测量精度

设计并改进运算模块,提高测频精度,高速采样下的连续、实时采样,优化设计,尽量降低FPGA的资源利用率和功耗。实际测试时,被测信号为(40±10)kHz时,输出数据的速率有1次/10s、1次/s、10次/s三挡(主要是受RS422/RS232转换接头的实时性和稳定性的影响)。该样机在1Hz采样频率下静态测试每一路的实际精度为:相对误差小于9.99×10-7,稳定度小于4.90×10-8。

(4)FPGA的嵌入式软核的应用

鉴于FPGA的飞速发展,在可编程逻辑器件中不仅采用硬件的IP核,以节约资源提高设计效率,而且采用了Nios Ⅱ软核这款32位高性能处理器在FPGA内部进行配置,实现了可编程片上系统,提高了系统的可靠性。

基于Nios Ⅱ嵌入式处理器的SOPC中精度测频电路的设计,采用以上关键技术将数据采样和运算单元都集成在FPGA芯片中,形成一个片上操作系统SOPC,获得了较高精度的测量结果。

[1] 章军,张平,于刚.多周期同步测频测量精度的提高[J].电测与仪表,2003,40(6):16-17.

[2] 李兰英.Nios Ⅱ嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2008.

[3] 周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2008.

[4] 张海风.HyperLynx仿真与PCB设计[M].北京:机械工业出版社,2006.

[5] 徐海军,叶卫东.FPGA在高性能数据采集系统中的应用[J].计算机技术与应用,2005,25(1):40-43.

[6] 周润景,景晓松.Mentor高速电路设计与仿真[M].北京:电子工业出版社,2008.

[7] 王诚,吴继华,范丽珍,等.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2011.

SOPC Medium Precision Design for Frequency Measurement Circuit Based on Nios Ⅱ

DONG Jian-shu1,YUAN Xiao-yu1,WANG Hui2,YAN Zong-rui3

(1.Beijing Institute of Automatic Control Equipment,Beijing 100074,China;2.Beijing Revitalization Institute of Measurement and Test,Beijing 100074,China;3.Nanjing Naval Command Academy,Nanjing 210016,China)

The medium precision frequency measurement circuit is presented for the second measurement of quartz flap accelerator’s frequency output.Firstly,the scheme’s theoretical error is analyzed in detail by comparing and selecting proper measurements.Secondly,the frequency measurement circuit based on Nios Ⅱ embedded processor is discussed:both the data sampling and operation unit are integrated in FPGA chip,which forms SOPC,and a higher precision measurement result is achieved.

Frequency measurement;FPGA;Embedded processing;SOPC

2015 - 03 - 20;

2015 - 04 - 15。

董建树(1979 - ),男,主要从事工业测控技术,信息化技术等方面的研究。

E-mail:treeplanter@163.com

TL822

A

2098-8110(2015)05-0070-06