基于FPGA的某ISAR成像数字中频接收机实现

2015-03-06张庆祥尹程成立涛

张庆祥,尹程,成立涛

(哈尔滨工业大学电子工程技术研究所,黑龙江哈尔滨150006)

基于FPGA的某ISAR成像数字中频接收机实现

张庆祥,尹程,成立涛

(哈尔滨工业大学电子工程技术研究所,黑龙江哈尔滨150006)

根据软件无线电理论设计了一种应用于逆合成孔径雷达成像系统的数字化中频接收机,提出了一种可变抽取因子的数字下变频方案,可以大大提高接收机系统的灵活性。该数字化中频接收机最终在Xilinx Virtex-6 FPGA上实现,可保证在不发生频谱混叠的情况下将中心频率为105 MHz,带宽0~20 MHz之间可变的中频信号下变频为低数据率的数字零中频信号。系统提供2~84之间共14种不同的抽取因子,可以根据输入信号带宽进行配置。测试结果表明,该系统设计正确且无虚假动态范围大于90 dB。

数字中频接收机;数字下变频;多速率信号处理;抽取因子

0 引言

传统的模拟中频接收机由于模拟器件和电路的不稳定性,正交混频时很难实现同相/正交(Inphase/ Quadrature,I/Q)通道幅度和相位的良好平衡,直接影响到接收机的动态范围等性能指标[1]。随着数字信号处理器件的发展,数字中频接收机由于具有精确、可靠、灵活、体积小、成本低等优点逐渐取代模拟中频接收机成为雷达系统的一个关键部分。根据软件无线电的思想,接收机中的模/数转换部分应该尽可能靠近天线[2],但是,目前的模/数转换器件还无法满足对射频信号进行无失真采样的条件,而且射频采样的直接影响就是采样后的数据率非常大,现有的数字信号处理器(Digital Signal Processor,DSP)、现场可编程门阵列或通用信号处理器件无法完成这种高速的数据处理,所以数字中频带通采样结构被广泛采用。

FPGA具有强大的并行数据处理能力,可编程而且实时性好,用于完成数字下变频等信号预处理;DSP适用于完成复杂的基带信号处理算法,但实时性不高。为了完成数据的实时处理,本文的接收机采用FPGA+DSP架构。同时,针对逆合成孔径雷达成像的回波信号的特点,提出了可变抽取因子的数字下变频方案。

1 数字中频接收机相关理论

雷达数字中频接收机的主要作用是将模/数转换器(Analog to Digital Converter,ADC)采样后的中频信号转换为数字基带信号,同时通过多速率信号处理将采样速率调整至适宜于后端信号处理器的速率。本部分介绍数字中频接收机相关的一些理论。

1.1 带通采样定理

对于低通信号,为了避免混叠,采样频率需要满足奈奎斯特采样定理。但是对于带通信号,尤其是窄带信号,采样频率通常不用大于信号最高频率的2倍也可以避免混叠。通常,带通信号的采样频率可以按照下式确定[3]:

式中:n为非负整数;fc为信号载频或中心频率。

1.2 数字下变频

窄带带通信号可以表示为:

式中:a(t)为信号的幅度函数;ω0为载频角频率;φ(t)为相位函数[4]。采样周期为Ts,则采样后的信号为:

I,Q两个通道的数字本振信号分别为:

经过混频器后输出为:

经过低通滤波器后,高频成分被滤除,从而得到基带信号:

1.3 多速率信号处理

多速率信号处理包括抽取和插值两部分,抽取可以降低数据率,而插值则可以增大数据率。本文数字下变频时主要涉及到的理论是整数倍的抽取。

经过数字下变频,中频信号的载频被去除,但是信号的数据率并没有降低,这很不利于后级的高阶数字滤波器的设计实现,所以需要对数字下变频后的数据进行抽取处理以降低数据率。

假设原始信号序列为x() n,抽取因子为D(D为正整数),则抽取后的新序列为:

其离散时间傅里叶变换为[5]:

即抽取后的信号频谱Xd() ejω可以由原信号频谱先做频率的D倍扩展,后按2π/D的整数倍移位后叠加得到。

如果原始信号序列x(n)的采样频率为fs,那么其无模糊带宽为fs/2;对序列进行D倍抽取后,新的序列xd(n)的采样频率为fs/D,无模糊带宽为fs/2D。要使抽取后的信号频谱不发生混叠,需要在抽取前加入带宽为π/D的防混叠低通滤波器,以保证x(n)中不含有大于π/D的频谱分量[6]。

2 数字中频接收机实现

2.1 系统硬件结构介绍

本文设计的雷达中频接收机为两路模拟中频信号输入,中心频率均为105 MHz,带宽0~20 MHz之间可变。

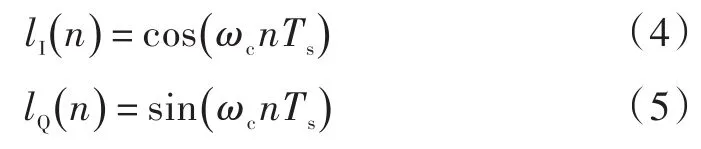

为了使接收机具有较强的适应性,需要高带宽、高分辨率的ADC和强大的基带信号处理功能。综合考虑采样精度和采样速率,选择LTC2185作为设计的模/数转换芯片,负责两路信号的模/数转换。LTC2185是一款双通道模/数转换器,最高采样速率为125 MHz,采样位宽为16位,能够提供76.8 dB的信噪比和90 dB的无杂散动态范围[7]。由于数字下变频中混频滤波需要实现较多的逻辑运算和乘法运算,所以FPGA选用Xilinx Virtex -6系列中专门针对高性能逻辑和数字信号处理优化的LXT系列中的XC6VLX240T。基带信号处理选用浮点型DSP处理器TigerSHARC TS201S,该DSP不仅具有强大的定点和浮点运算能力,而且具有丰富的I/O资源[8],可以方便地与外部通信。系统平台设计结构如图1所示。

图1 硬件平台结构

2.2 接收机FPGA软件设计

Virtex-6 FPGA内部模块主要分为数字下变频模块和TS201S接口模块。数字下变频模块接收模/数转换后的信号,进行数字下变频处理和抽取滤波;TS201S接口模块负责FPGA与DSP之间的数据传输,软件模块划分如图2所示。

图2 FPGA软件模块划分

数字下变频模块内部结构设计如图3所示。模/数转换器LTC2185输出的低压差分信号通过专用差分引脚输入FPGA内部,ADC接口模块将输入的双数据率低压差分信号转换为单端单数据率信号。数字下变频部分进行混频、抽取、滤波等处理。

图3 数字下变频模块

数字本振采用直接数字频率合成器实现,输出I,Q两路正交本振信号。由于雷达回波信号幅度波动范围较大,为了避免采样信号幅度过小或过大的情况出现,设计了增益控制模块,用于控制信号幅度保持在合理范围内。双通道FIFO用于缓存数据,FIFO存储器的容量根据输入输出数据率设计为深度32 768,64位的读/写位宽。

TS201S接口模块主要用于传输FPGA数字下变频后的数据至TS201S和译码TS201S的指令,其中SPI接口模块用于配置模/数转换器,如图4所示。

图4 TS201S接口模块

数字下变频、SPI接口、状态寄存器等模块中的配置寄存器映射到TS201S的地址空间,TS201S通过读/写相应地址进行初始化配置等操作。译码器通过对地址信号和控制信号进行译码,产生相应寄存器和FIFO的读/写控制信号。另外,当FIFO中数据满时,TS201S接口模块负责产生中断信号通知DSP读取数据。

2.3 可变抽取因子的数字下变频设计

传统的数字下变频中,ADC采样后得到的信号直接与本振信号进行混频,然后进行抽取滤波以得到数据率较低的基带数字信号,实现简单,资源占用少[9]。但是,这种数字下变频抽取比例往往是一固定因子,当输入模拟信号带宽发生较大变化时容易出现频谱混叠或者抽取率不够等,因此不适用于输入信号带宽随时间有较大变化的情况。为了解决这一问题,本文设计一种抽取因子可变的数字下变频结构。

设计中采样频率fs为84 MHz,将84分解为质数的乘积84=2×2×3×7,设计4个抽取因子为2的抽取滤波器、2个抽取因子为3的抽取滤波器和2个抽取因子为7的抽取滤波器。一组I,Q通道的滤波器组成一个滤波器组。设计结构如图5所示。

图5 可变抽取因子数字下变频

ADC采样后的输入与数字本振产生的本振信号混频后得到I,Q两路输出,将这两路输出分别连接到4个多路选择器。多路选择器根据控制信号选择某一路输入作为输出,连接至一个滤波器组。4路滤波器组的输出除了连接至多路选择器5之外,全部反馈至多路选择器1~4。这样,通过对多路选择器1~4的控制,就可以控制4个抽取滤波器组的级联顺序;通过对多路选择器5的控制,可以选择某一抽取滤波器组的输出作为整个数字下变频的输出。

例如,多路选择器1选择混频后的输出作为滤波器组1的输入,多路选择器2选择滤波器组1的输出作为滤波器组2的输入,多路选择器3选择滤波器组2的输出作为滤波器组3的输入,多路选择器4选择滤波器组3的输出作为滤波器组4的输入,多路选择器5选择滤波器组4的输出作为数字下变频的输出,则抽取因子为7×2×2×3=84。如果多路选择器5选择滤波器组2的输出作为数字下变频的输出,则抽取因子为7×2=14。

可以计算出,通过这种结构设计,该系统总共可以实现2~84共14种不同的抽取因子,相应地,数字下变频输出信号的采样率可以在1~42 MHz之间变化,输入信号的带宽可以在0~20 MHz之间变化。这样,系统可以根据输入信号带宽和输出数据率要求控制数字下变频的抽取因子,使得系统具有很强的适应性。

每个滤波器组中的抽取滤波器的冲激响应根据设计要求用Matlab进行设计然后量化得到。每个滤波器均设计了动态重配置的功能,冲激响应参数可以由TS201S实时配置。

3 仿真测试结果

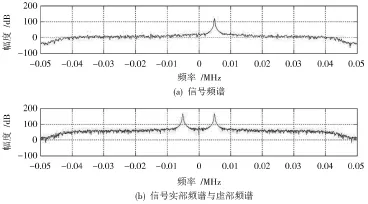

根据设计需求,编写仿真测试平台,通过该测试平台对该中频接收机进行了全面的测试。仿真测试结果如图6所示。

图6 仿真测试结果

系统上电后,TS201S通过读/写地址空间对状态寄存器、中断屏蔽寄存器、中断使能寄存器、可编程FIFO、数字本振、抽取滤波器等进行配置,然后通过SPI接口对LTC2185进行配置。待各项配置完成后,系统进入正常工作状态。

实际测试中,使用惠普公司HP8226A产生待采样信号,数字下变频数据存储在TS201S的高速缓存中,利用Matlab分析数据,证明了设计的正确性,如图7所示。

图7 数字下变频测试结果

由于设计中采用了高分辨率的ADC且滤波器幅频特性经过精心设计,该数字中频接收机的无虚假动态范围达到了90 dB以上。设计的数字中频接收机已经成功应用于实际ISAR成像系统中。

4 结语

本文讨论了一种应用于ISAR成像系统中的宽带数字中频接收机的软硬件设计与实现。根据ISAR成像系统回波特点设计了一种抽取因子可在2~84之间变化的数字下变频结构,使得系统对回波频谱宽度有较强的适应性(0~20 MHz)。仿真实验和实际测试均证明了设计的有效性,而且系统的无虚假动态范围大于90 dB。

[1]LIU Wei,YAO Di,SUN Yingqin.Design of digital IF receiver based on ADCs and FPGAs[C]//Proceedings of 2013 IET International Radar Conference.Xi’an,China:IET,2013:1-4.

[2]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.

[3]LIU Jianhua,ZHOU Xiyuan,PENG Yingning.Spectral arrangement and other topics in first-order bandpass sampling theory[J].IEEE Transactions on Signal Processing,2001,49:1260-1263.

[4]郑薇,赵淑清.随机信号分析[M].哈尔滨:哈尔滨工业大学出版社,2011.

[5]CROCHIERE R E,RABINER L R.Interpolation and decimation of digital signals:a tutorial review[J].Proceedings of IEEE,1981,69(3):300-331.

[6]程佩青.数字信号处理[M].北京:清华大学出版社,2007.

[7]Linear Technology.LTC2185/LTC2184/LTC2183 datasheet[EB/ OL].[2011-02-17].http://www.linear.com.

[8]Analog Devices.TigerSHARC embedded processor ADSPTS201S[EB/OL].[2006-06-23].http://www.analog.com,2006.

[9]ZHUO Zhihai,LI Shange,LI Wenguang.Implementation of high-performance multi-structure digital down converter based on FPGA[C]//Proceedings of 2012 the 11th IEEEInternational ConferenceonSignalProcessing.Beijing,China:IEEE,2012:31-35.

Realization of FPGA-based digital intermediate frequency receiver for ISAR imaging

ZHANG Qingxiang,YIN Cheng,CHENG Litao

(Research Institute of Electronic Engineering Technology,Harbin Institute of Technology,Harbin 150006,China)

A digital intermediate frequency receiver applied to inverse synthetic aperture radar(ISAR)imaging system was designed according to software defined radio theory.The digital down conversion scheme of variable extraction factor is proposed to improve the flexibility of the receiver system.The digital intermediate frequency receiver is realized on Xilinx Virtex-6 FPGA,which can convert the variable intermediate frequency signal whose center frequency is 105 MHz and bandwidth ranges from 0~20 MHz into digital zero intermediate frequency signal of low data rate in the condition of without spectrum aliasing.The system provides 14 different extraction factors among 2~84,which can be configured according to the bandwidth of input signal.The test results show that the system design is correct,and the spurious-free dynamic range is bettter than 90 dB.

digital intermediate frequency receiver;digital down conversion;multi-rate signal processing;extraction factor

TN957.5-34

A

1004-373X(2015)23-0060-04

10.16652/j.issn.1004-373x.2015.23.017

张庆祥(1962—),男,黑龙江哈尔滨人,教授,硕士生导师。主要研究方向为雷达信号处理、并行处理技术、可编程逻辑器件系统设计与应用。

尹程(1991—),男,四川绵阳人,硕士研究生。主要研究方向为现代信号处理、嵌入式技术。

2015-05-26

国家自然科学基金重点基金(61032011)

成立涛(1989—),男,湖南永州人,硕士研究生。主要研究方向为现代信号处理。