大规模SoC的电源网络设计

2015-02-26张玲,王澧

张 玲,王 澧

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

在现代集成电路特别是在超大规模集成电路的设计中,电源网络如何分布已成为一项越来越重要的工作。通常,芯片面积中很大一部分被电源/地线占据,而随着集成电路工艺水平的不断提高,特征尺寸不断减小,芯片规模、频率和功耗却在不断提高[1]。在SoC芯片电源设计中,有两个方面需要特别关注,它们是电迁移和电源/地线网络上的IR-drop。

2 电源网络设计中的EM和IR-drop现象

随着集成电路进入到深亚微米阶段,芯片的工作速度和可靠性等各方面的要求都需要设计工程师仔细考虑到。其中,电迁移(EM)与IR-drop的实现是否能达到预期,对芯片的各项特征起到了关键的作用。

2.1 EM现象

在金属线中,电流是通过电子的不断流动来传导的。在电子流动中不断地撞击原子,当电流密度达到一定值并持续一段时间后,会使金属原子的位置发生改变,这种现象称为电迁移(EM)[1]。EM会导致金属线的形状发生改变,甚至造成电路的断路,或导致相邻导线间产生短路,从而使得电路不能正常工作,影响芯片的可靠性和寿命。

随着超大规模集成电路特别是SoC电路的不断发展,芯片的功耗不断增长而芯片电压却在不断降低,因此,电源/地网络承受的电流不断增大。与此同时,由于工艺特征尺寸不断减小,金属连线的宽度也随之减小,这样,金属连线上的电流密度变得越来越大。因此,EM现象在现代集成电路设计中变得越来越严重[2]。

以下因素会影响由电迁移导致的电路产生故障的时间:温度、金属的材料和电流密度[2]。在现代集成电路设计中,经常采用以下方法来减少EM的产生:(1)采用合金或者铜来代替铝制作金属互连线。(2)采用热传导系数较高的材料来制作绝缘层,并在芯片封装和系统设计时充分考虑散热的问题。降低金属材料的温度可以大大降低EM的影响。(3)控制金属线上的电流密度。降低电流密度不仅对电迁移导致的电路失效有直接的减少作用,而且由于电流密度的减少可以降低金属材料的温度,从而可以进一步减少EM的产生[2]。

2.2 IR-drop现象

随着SoC芯片的工作电压不断降低,电源金属线变得越来越细,由此带来的金属线电阻变得越来越大。这样,电源电压有相当一部分消耗在电源线路上,由此引起门电路的供电电压大幅下降,这就是通常说的IR-drop[3]。同样的情况也出现在地线网络上,从而导致门电路的地电压不等于供电电源的地电压。

在通常的芯片设计中,VDD供电电压要经过封装管壳管脚(Package Pin,Bonding)、电源压焊点(Power Pad)、电源环(Power Ring)等器件与连线才能最终到达标准单元门电路的VDD电源端,如图1所示。

图1 电源线路消耗图

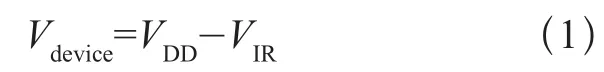

由于在这些金属连线上存在着一定的电阻,导致门电路实际的VDD电压有所下降,因此门电路VDD端的电源电压实际为:

其中,Vdevice为门电路电源端的实际电压,VDD为芯片的供电电压,VIR为芯片中由电源网络的电阻所消耗的电压。

IR-drop现象的产生,除了会降低门电路的噪声容限以外,还会延长时序收敛,从而降低了芯片的性能,严重时会导致芯片的功能出现错误[3]。例如,在典型的0.18 μm工艺的设计中,如果门电路的供电电压降低10%,会导致门电路的传播延时(Propagation Delay)增加8%[3]。因此,在现代集成电路设计中,通常要求在门电路的电源和地之间的实际电压大于理想供电电压的90%。考虑到在地线网络上同样存在着噪声,因此式(1)中电源网络上的VIR应小于理想供电电压的5%,即:

因此,在集成电路设计中经常采用以下方法来降低IR-drop等的影响:(1)增加电源网络和地线网络上的金属连线资源,从而减小网络的电阻;(2)在芯片内部放置去耦电容,为器件开关时所产生的瞬时大电流提供额外的电荷。

3 电源/地网络的设计策略

在SoC设计中必须仔细分析和优化电源网络以避免EM、IR-drop等现象对系统性能与可靠性的影响。

在2.1节中介绍了多种方法都可以有效地减小EM的影响,但是在芯片设计中,芯片设计工程师能直接控制的只有电流密度。对电流密度的控制,最有效的方法是通过增加电源/地网络上金属连线的宽度,从而减小流过金属线上的电流。

若电源/地网络上的金属线宽度增加了,也可以有效地降低IR-drop对系统的影响。但是,若增加的连线资源大大超出需要,则会造成芯片面积的浪费,从而导致SoC芯片的成本上升。而且,由于电源网络中的金属线占用了大量的布线资源,如果使用过宽的电源线,还可能导致布线中的拥塞(Congestion)问题无法解决。因此,如何在SoC中进行合理、有效的电源分配就成为十分重要的问题[4]。

在以往的设计中,由于没有合适的方法,设计者不能在设计的初始阶段就开始进行电源/地网络的分析与优化,只是根据个人经验来进行电源/地网络的设计。针对这一问题,本文提出一种方案,可以在芯片的布局规划(Floorplan)阶段通过一些简单的估算来进行电源/地网络的初步设计。并以此作为参考设计,借助于对其进行IR-drop和EM的分析,经过少许的修改和优化,即可得到满意的电源/地分配网络[5]。

3.1 确定power/ground PAD的数目

在电源/地网络的设计中,首先要解决的问题就是电源/地PAD的数目以及摆放位置。通常,这些PAD均匀分布在PAD Ring上,因此,主要的问题就是确定它们的数目。根据芯片的功耗以及工作电压,可以估算出总的电流大小:

其中,Itotal为芯片的Chip Core部分总的电流大小,Ptotal是Chip Core上的总功耗,Vcore为Chip Core的工作电压。当芯片的工作电流确定了之后,根据公式(4),即可确定所需的电源/地PAD的数目。

其中,Ipad为一对Power Pad和 Ground Pad所允许通过的电流的最小值。式中N为设计所允许的Power/Ground Pad的最少数目,通常在设计允许的情况下,应该尽可能多地放置Power/Ground Pad。这不但可以减小IR-drop,而且冗余的Power Pad和Bonding Wire也可以减小寄生电感,从而降低瞬时电流变化而导致的电压波动。

3.2 确定Power Ring 和Power Grid的数目

Power Grid的设计是整个SoC芯片电源/地网络设计中的主要部分。Power Grid从Power Ring上提取电流,并向Power Rail提供驱动。由于Power Rail的宽度通常是固定的,因此Power Grid的设计不但直接决定了其本身的IR-drop,而且还决定了在Power Rail上的IR-drop[6]。

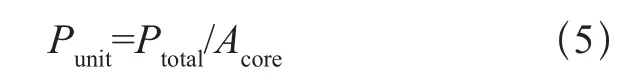

首先,根据硅片面积和芯片的整体功耗,估算出硅片上单位面积的平均功耗:

公式中,Ptotal是chip core上总的平均功耗,Punit为chip core上单位面积的平均功耗,Acore是chip core的硅片面积。

其次,估算某一固定长度的标准单元行(standcell-row)上所消耗的平均电流:

其中,I是长度为l的cell-row中消耗的电流,W是standcell的高度。

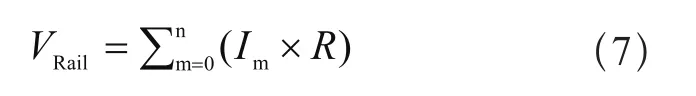

若一行中,有n个串联的长度为L的power rail上的IR-drop为:

其中,Im是第m个长Cell-row上的电流,R是长度为l、宽度为d的power rail金属线上的电阻。R可以由加工工艺参数得出,Im可以由另一个公式(8)得出:

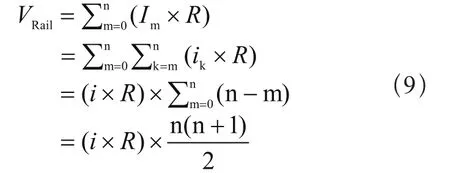

将式(8)代入式(7)中,可得到式(9):

最后,设计师需要决定设计中可以接受的在power rail上的IR-drop的大小,并根据式(9)计算出n的大小,从而确定power grid之间的间距。当power grid的间距定下来之后,根据其上每一条金属线的平均负载及加工的工艺参数,可以很容易地确定其宽度。

4 设计实例及实验结果分析

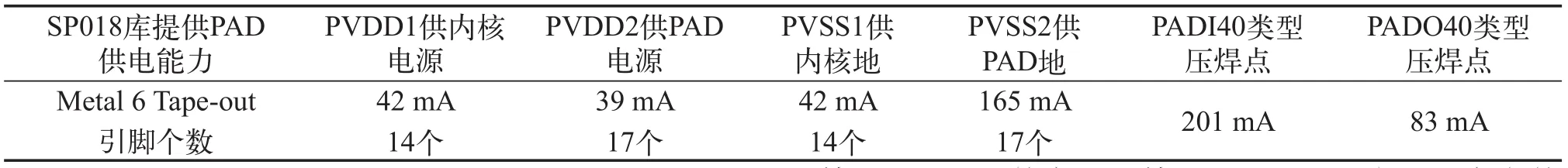

作者在工作中设计了一款芯片,该芯片含有4个SRAM宏单元。该芯片采用SMIC 0.18 μm 1P6M Salicide CMOS工艺,工作频率为100 MHz,PAD的工作电压为3.3 V,CORE的工作电压为1.8 V。该芯片工作时的动态功耗不高于540 mW,供电方面采用最直接的策略就是尽量增加整个芯片的电源、地引脚,详情见表1。SMIC SP018库所提供的电源、地PAD的供电能力,一方面与PAD逻辑本身有关,另一方面与采用的压焊点结构有关。该芯片设计中由于采用交错排列的压焊点排布,共采用了2种压焊点设计,分别为PADI40及PADO40。如表1所示,如果PVDD1这个PAD与PADO40压焊点结构组合使用,则供电能力只有42 mA,受制于PVDD1的供电能力;PVSS2这个PAD与PADO40压焊点结构组合使用时,也只有83 mA的供电能力,受制于PADO40压焊点的供电能力。但由于芯片提供的PAD 3.3 V PAD共17对,内核1.8 V PAD共14对,所以从理论上无论使用何种组合,都已经可以满足芯片动态功耗的需要。

表1 电源/地PAD的供电能力表

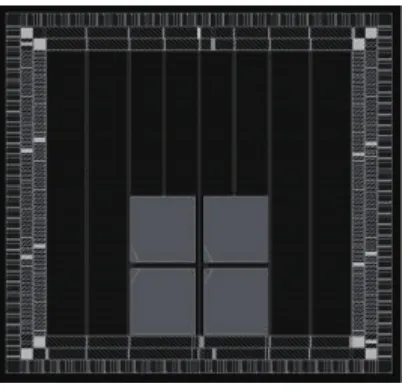

根据该芯片包含的标准单元与IP硬核的数目及面积,以及结合封装管壳的要求,先估算芯片的面积。该芯片预估面积为6 mm×6 mm。在本设计中,理想电压为1.8 V,即VIR≤18 mW,再根据3.2节中计算Power Grid的方法,算出Power Grid在水平方向的条数以及间隔间距。在实际应用中,考虑到各个IP模块的大小及形状,在实际的电源网络中,将Power Grid在水平方向的间距定为600 μm,如图2所示。

图2 电源网络排布图

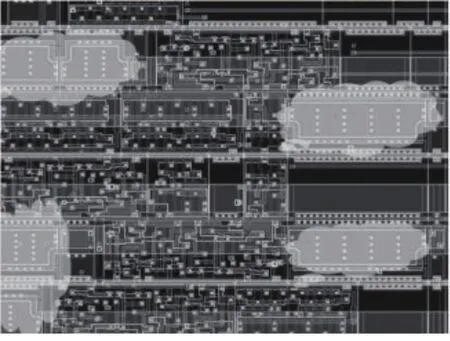

为了更好地减小电源/地网络的EM及IR Drop效应,电源/地的ring采用金属叠层的方法以减少寄生电阻。水平方向采用Metal3/Metal5叠层,垂直方向采用Metal4/Metal6叠层。为了更好地稳定内核电源/地网络,在该芯片内设计专门的去耦电容,数量级达到十几个nF,以稳定内核电源地线网络。图3为去耦电容的版图与在版图中的位置。

图3 去耦电容在版图中的放置

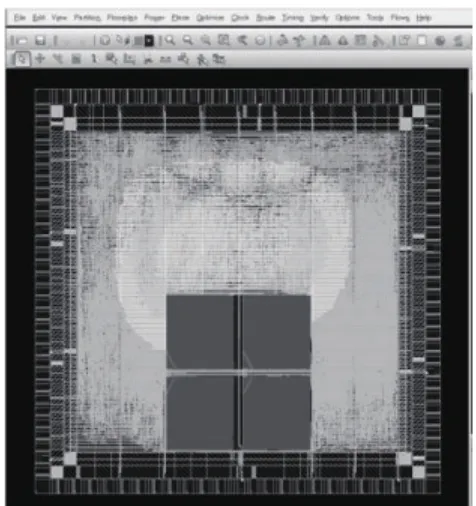

在综合考虑电源/地PAD的数目、宏单元的摆放位置以及电源/地线的规划后,可以在布局布线工具Encounter中查看压降分析结果,对照本文中提出的电源/地网络的设计策略,验证本文提出的方法是否正确。在Encounter中按照本文提出的方法设计了电源/地PAD的数量与摆放位置,以及电源/地环的宽度与Power Grid的间隔距离。在Encounter中得到一个电压压降图,其电压压降分析结果如图4所示。黄色区域与绿色区域的面积最大。压降力度按颜色红、橘红、黄、绿、蓝依次减弱,可见此款芯片的压降力度比较理想。压降报告显示VIR最大压降为65.47 mV,VIR≤5%VDD,满足压降要求,从而表明本文提出的电源网络的设计方法在该芯片的设计中得到了很好的验证。

图4 版图电压降示意图

该电路测试内容复杂。通过对该电路的工作原理和电气参数的理解与分析,采用美国泰瑞达公司的J750测试系统完成圆片中测及成品测试。该芯片中测平均成品率85%,封装的全线总成品率达到了96.67%。

5 总结

在现代超大规模集成电路的设计中,如何有效地避免由于EM和IR-Drop等现象对系统性能造成影响,已成为芯片设计中的一个重要环节。针对这一问题,本文首先介绍了这些现象产生的原因和影响因素,其次提出了一种简单、有效的方法,可以在物理设计中对SoC的电源网络进行一些简单的估算,并以此为参考,可以有效地设计出实际的电源网络,从而保证电源分配的可靠性。最后,结合作者实际工作中设计的电路,给出了该芯片电源/地网络的设计实例,通过该实例证明本文所提方法的实用性和有效性。

[1] Payman ZarkeshHa, Meindi James D. Optimum on chip power distribution networks for gigascale integration[C].Proceedings of the IEEE 2001 International Inter connect Technology Conference, Burlingame,CA,USA:IEEE,2001, (6): 125-127.

[2] 田志新,刘勇攀,杨华中,等. 基于马尔可夫—蒙特卡洛采样的电源网络分析[J]. 微电子学与计算机,2008, (12): 1-4.

[3] 严晓浪,杨垠丹. 超深亚微米集成电路IR-DROP快速论证分析的研究[D]. 浙江大学,2004.

[4] 时昕. 深亚微米SoC中的电源_地网络设计[D]. 北京:中国学位论文全文数据库,2007.

[5] 陈春章,艾霞,王国雄. 数字集成电路物理设计[M]. 北京:科学出版社,2008.

[6] 刘辉华. 超深亚微米SOC芯片布局布线实现[D]. 成都:电子科技大学,2006.