基于FPGA同步时钟测量系统的研究及实现*

2014-12-10王国富张法全叶金才

陈 巍 ,王国富 ,2,张法全 ,叶金才

(1.桂林电子科技大学 信息与通信学院,广西 桂林 541004;2.广西无线宽带通信与信号处理重点实验室,广西 桂林 541004)

0 引言

瞬变电磁法是勘探地下不同介质电性参数的重要方法之一,在抢险救援、工程施工设计、地下水勘探以及矿产勘探等领域被广泛应用[1-2]。煤矿探水雷达利用瞬变电磁法的原理,在发射机关断发射电流的瞬间,接收机采集接收地下介质产生的纯二次场,因此需要发射机与接收机之间同频同相地工作,同步时钟信号是双极性的,且要求同步时钟精度优于800 ns。由于勘探地质的复杂性和未知性,通过GPS和恒温晶振的互补协调工作来产生同步时钟[3-4],接收机与发射机的同步时钟信号在空间上是分离的,所以同步时钟信号往往不是完全同步的,会产生不可避免的时间差,而这个时间差的大小决定了整个系统采样的精度和后续反演算法的准确性。在实际过程中,用示波器观察往往只是得到短期的观测数据,不能对时间差数据进行存储,得到的结论并不准确,因此对同步时钟信号的矫正具有一定的局限性。参考文献[5]提出了一种倍频相移的时间间隔测量方法,最大分辨率为625 ps,参考文献[6]提出了基于CPLD的时间间隔测量方法,最大分辨率为300 ps。本设计提出了一种高精度的同步时钟信号时间差测量系统,最大分辨率为200 ps,对同步时钟信号的时间差可以进行长时间测量,并能对时间差数据进行存储,在上位机上对存储的时间差绘制成曲线。与参考文献[5]、[6]相比,本设计具有更高的精度,能够对时间差进行存储和绘制成曲线,拥有更广泛的应用前景和实用性。

1 总体框架

同步时钟信号时间差测量系统主要由恒温晶振模块、单极性转换电路模块、时间间隔测量模块、LCD、SD卡和PC等组成,系统框图如图1所示。单极性转换电路a、b分别把双极性同步时钟信号 A、B转换成单极性信号C、D,再通过时间间隔测量模块测得单极性信号C、D之间的时间差,时间间隔测量模块在FPGA内部完成。时间差可以在LCD上显示,SD卡可以对时间差进行存储,PC可以对SD卡存储的时间差绘制成曲线,用来观测时间差的变化。系统电源模块为系统提供工作电源,恒温晶振为FPGA模块提供稳定的工作频率。

2 各模块设计

2.1 单极性转换电路

图2 单极性转换电路

由于煤矿探水雷达的同步时钟信号A、B是双极性的,而FPGA模块无法处理负电平,所以需要将同步时钟信号进行单极性转换。以同步时钟信号A为例,单极性转换电路如图2所示。当INA+是正电压、INA-是负电压时,则光耦Opt1导通,光耦Opt2截止,与非门NAND1输出高电平,与非门NAND2输出低电平,经过异或门XOR后输出高电平。同理:当INA+是负电压、INA-是正电压时,光耦Opt1截止,光耦Opt2导通,与非门 NAND1输出低电平,与非门NAND2输出高电平,经过异或门XOR以后输出高电平,波形图如图3所示。同步时钟信号在每个周期内有两次归零突变,这两次突变控制发射机的发射脉冲和接收机的信号采样脉冲,因此需要测量这两次突变的时间差。

图3 单极性转换电路各点波形图

2.2 时间间隔测量模块

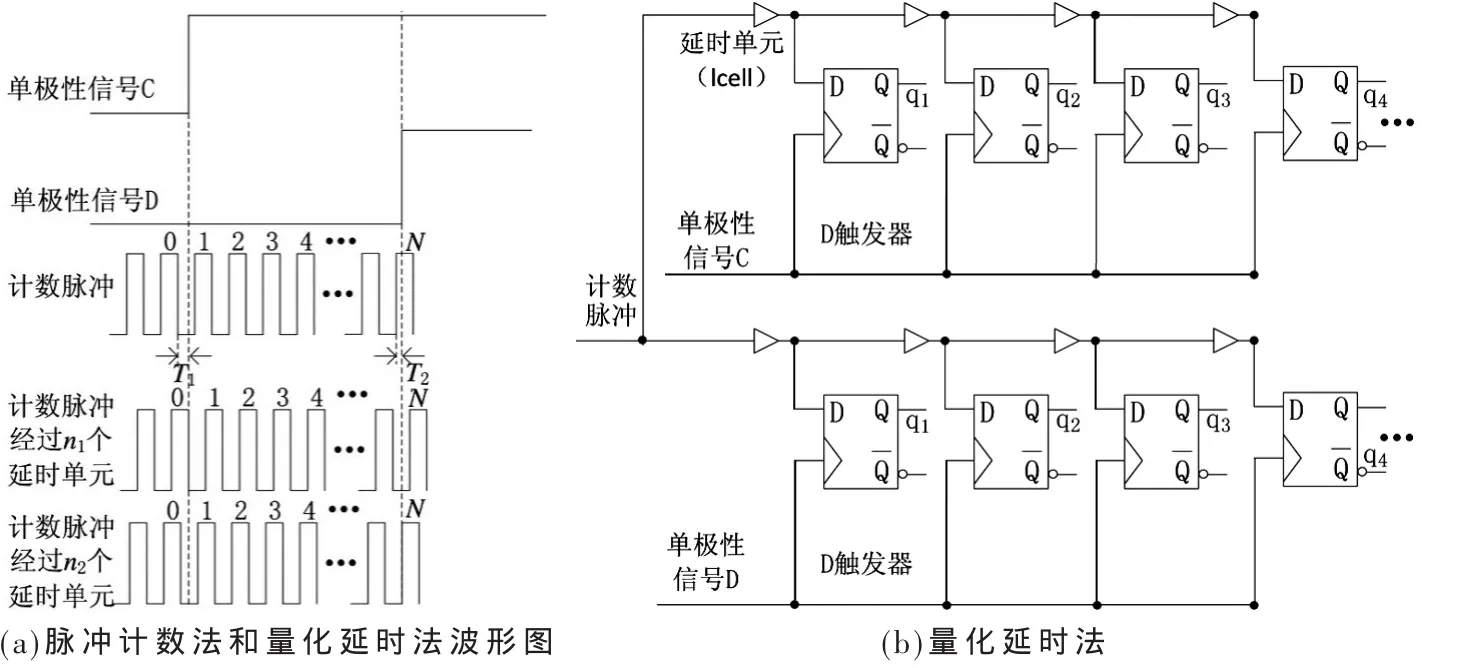

同步时钟信号 A、B通过单极性转换电路 a、b进行转换,由于单极性转换电路是完全对称的,因此对同步时钟信号造成的延时误差可以忽略不计。恒温晶振输出频率稳定,在短期内稳定度很好,且不受外界温度影响,为FPGA提供精确的时钟。FPGA调用IP核中的锁相环(PLL),将恒温晶振输出的10 MHz频率倍频到 100 MHz,这样可以有效地降低计数误差,误差为10 ns。时间差测量模块对单极性信号C、D进行时间差精密测量,包括脉冲计数法和量化延时法,两者之和即为单极性信号C、D的时间差。脉冲计数法和量化延时法的波形如图4(a)所示,单极性信号C的上升沿作为脉冲计数单元的计数开始信号,单极性信号D的上升沿作为脉冲计数单元的计数结束信号,计数脉冲周期T=10 ns,计数结果为粗测量。T1是计数脉冲与单极性信号C不对齐的部分,T2是计数脉冲与单极性信号D不对齐的部分,测量结果为精测量,精测量由FPGA的内部硬件延时单元lcell和D锁存器实现,量化延时法如图4(b)所示。

图4 时间差测量原理

图中选用4级延时单元作为示例计算T1和T2。计数脉冲信号经过FPGA内部延时单元作为D触发器的信号输入,单极性信号C、D作为D触发器的时钟输入,D触发器在时钟上升沿发生状态转换,输出信号等于输入信号。在延时单元链中,每个延时单元的延时时间t=200 ps,因此每经过一个延时单元,计数脉冲相对于单极性信号C、D会延时200 ps。如图 4(a)所示,当单极性信号C的上升沿到来时,计数脉冲与单极性信号C的上升沿不对齐部分T1是低电平,则计数脉冲经过n1个延时单元后,第0个计数脉冲的下降沿与单极性信号C的上升沿对齐。此时,在量化延时单元链中,前n1-1个D触发器输出的是低电平,第n1个D触发器输出的是高电平,通过对D触发器进行编码,能够知道n1的值和不对齐部分T1是低电平,则时间T1=n1t;当单极性信号 D的上升沿到来时,计数脉冲与单极性信号D的上升沿不对齐部分T2是高电平,则计数脉冲经过n2个延时单元后,第N个计数脉冲的上升沿与单极性信号D的上升沿对齐。此时,在量化延时单元链中,前n2-1个D触发器输出的是高电平,第n2个D触发器输出的是低电平,通过对D触发器进行编码,能够知道n2的值和不对齐部分 T2是高电平,则时间T2=n2t。

综上:不对齐部分T1存在两种可能,为低电平或者高电平;不对齐部分T2也存在两种可能,为低电平或者高电平,而通过对D触发器的编码,能够知道不对齐部分T1、T2是低电平还是高电平,进而能够得到准确的时间差 △Ti。

其中,N是计数脉冲个数,T是计数脉冲周期,n1是求T1的延时单元个数,n2是求 T2的延时单元个数,t是延时单元的延时时间,0表示低电平,1表示高电平。

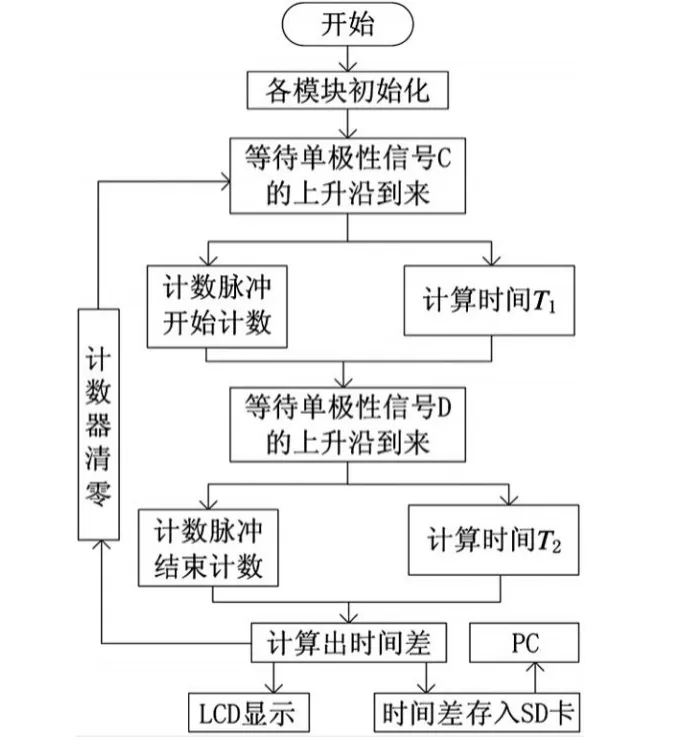

2.3 系统软件设计

软件是控制硬件和实现算法的关键,本设计采用模块化分层管理,提高软件的稳定性和可行性,系统的软件流程图如图5所示。

3 实验结果

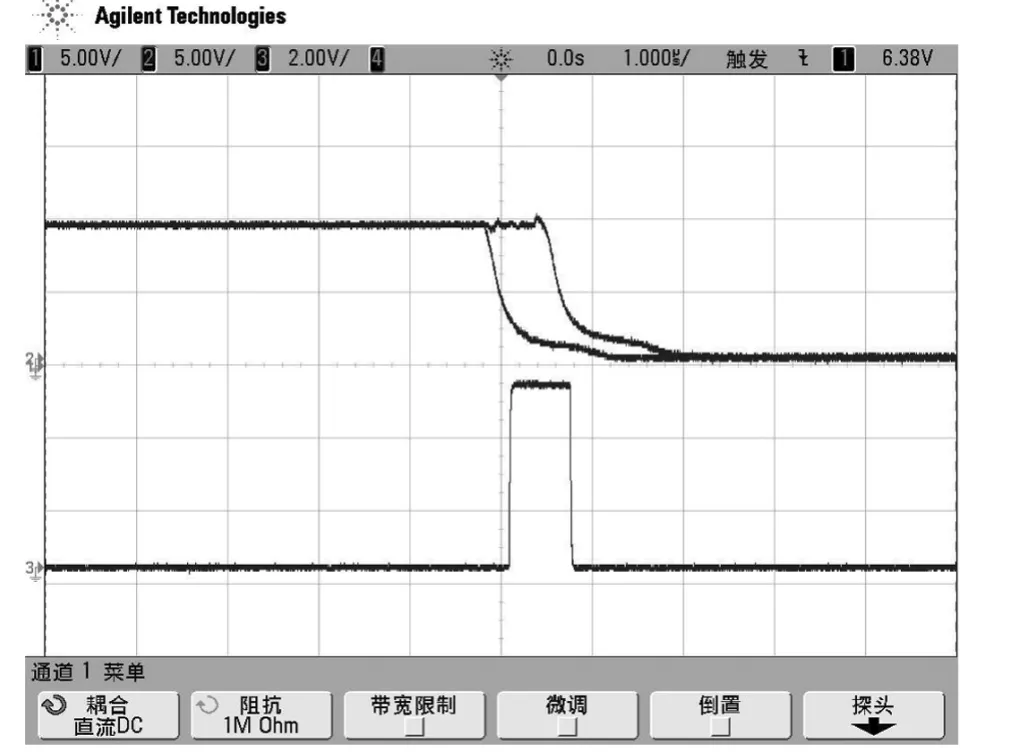

为了验证本系统的正确性和可行性,对煤矿探水雷达的接收机与发射机的同步时钟信号进行时间差测量。煤矿探水雷达采用6.25 Hz的双极性波,经过单极性电路转换以后,信号频率变为12.5 Hz,图6是两路同步时钟信号的波形,通道3是提取后的时间差,从图中可以看出,时间差小于800 ns,与实际时间差相符合。

图5 软件流程图

图6 时间差波形

表1 时间差实验结果

表1是同步时钟信号时间差测量系统工作8小时的统计数据。显示时间差的误差区间和落在该区间的次数,当时间差超过800 ns时,同步时钟精度不能达到煤矿探水雷达的勘测要求。从表1可以清楚地看到,时间差低于400 ns占99.85%,最大时间差不大于 800 ns,完全满足煤矿探水雷达的同步时钟精度要求。

4 结论

本文针对煤矿探水雷达进行勘测时需要高精度同步时钟的要求,设计并实现了高精度同步时钟信号时间差测量系统。该系统利用计数脉冲对同步时钟信号进行粗测量,内部延时单元和D触发器对同步时钟信号进行精测量,两者之和即为测量结果。用计算机对存储的时间差数据绘制成曲线,能够更加直观的判断同步时钟信号的稳定性。该系统已经应用到煤矿探水雷达的实际勘探中,对同步时钟信号时间差观测和矫正起到了很大的作用。

[1]姚丽,韦静,王玉阳.瞬变电磁法地质勘探的仿真研究[J].计算机仿真,2013,30(8):413-416.

[2]李宏杰.瞬变电磁探测技术在煤矿防治水中的应用[J].煤矿安全,2013,44(4):159-161.

[3]申屠刚,钱刚,杨贵玉,等.基于时间同步技术的新型远方终端单元设计[J].电力系统自动化,2008,32(15):45-48.

[4]吴宁,潘小龙,虞皆侠.高精度 GPS同步时钟的研究与实现[J].电力系统自动化,2008,32(10):61-65.

[5]蔡德胜,方寿海.一种短时间间隔测量方法的研究及其FPGA 实现[J].微电子学与计算机,2012,29(10):34-36.

[6]王加祥,相征,琚翔.基于CPLD的高精度时间间隔测量系统的设计[J].电子技术应用,2010,36(11):62-65.