PDP列驱动芯片能量恢复效率模型

2014-11-09华国环刘清惓

华国环,刘清惓

(南京信息工程大学 电子与信息工程学院,江苏 南京 210044)

1 引 言

等离子显示(PDP)、液晶显示(LCD)、LED(light emitting diode)背光的液晶显示、有机发光二极管(OLED)是几种重要的平板显示技术。OLED显示器拥有众多的优点:例如高对比度、高效率、较宽的可视角度、刷新率高、结构简单[1]。但是,OLED电视有一些严重的缺陷:例如寿命退化问题,以及高昂的制造成本[2]。因此,OLED电视在平板电视领域还没有得到广泛使用。传统LCD电视和LED电视的主要区别是背光源不同。LED电视相较于LCD电视有以下优点:低功耗、超薄、画质更佳[3]。PDP电视有一些内在的优点:例如自发光、刷新率高、动态显示效果好[4-5]。来 自 value electronics的2013 年 度 平 板电视专业画质测试结果显示,PDP显示技术依旧拥有最佳的综合显示效果[6]。PDP电视普遍具备600Hz的图像刷新频率,所以PDP电视非常适合3D图像显示[7]。但是,当平板电视的尺寸大于127cm(50in)时,PDP电视的功耗要比LCD电视大。

PDP电视的功耗由3部分组成:静态功耗、维持功耗和寻址功耗[8]。静态功耗,又称为固有功耗,它可以通过显示全黑图像来测量。维持期功耗有X、Y驱动电路功耗以及X、Y两电极对向放电产生的功耗组成[9-10]。国内外很多关于PDP能量恢复技术的研究都集中在X、Y板级能量恢复电路的改进设计及优化上[11-14]。比如通过使用放电补偿的方法,维持电路中的开关管都可以实现ZVS开启,并且屏电压没有明显的掉落[11]。Sangshin Kwak提出的维持电路跟传统的Weber电路相比,它的电压只有一半,这带来的好处是半导体器件的应力降低,同时成本降低[12]。通过在谐振中使用额外的功耗注入,维持电路可以工作在ZVS模式[13]。在Jae-Kyu Park提出的维持电路中,同步电流建立的方法增强了屏电压波形上升和下降时间的灵活性,并且减小了电感中电流的平均值[14]。上述能量恢复技术研究都是关于板级能量恢复性能提升和降低功耗的。

寻址功耗由PDP列驱动芯片自身功耗以及A、Y两电极之间对向放电产生的功耗组成[15]。寻址期功耗是PDP整机功耗的重要组成部分,尤其在3D显示PDP电视中。在显示白色隔点图像时,寻址功耗大约占系统总功耗的20%。但是涉及芯片级的能量恢复电路的研究报道很少。

为了分析PDP列驱动芯片的能量恢复效率,寻求降低寻址功耗的有效方法,本文提出了两个分析模型。分析结果揭示了列驱动芯片能量恢复效率的影响因素有3个:充电时间TE,沟道电阻Ron,负载电容CL。文中通过PDP系统测试验证了分析模型的精确度。本文提出的分析模型可以指导PDP列驱动芯片的设计。

2 列芯片能量恢复工作原理

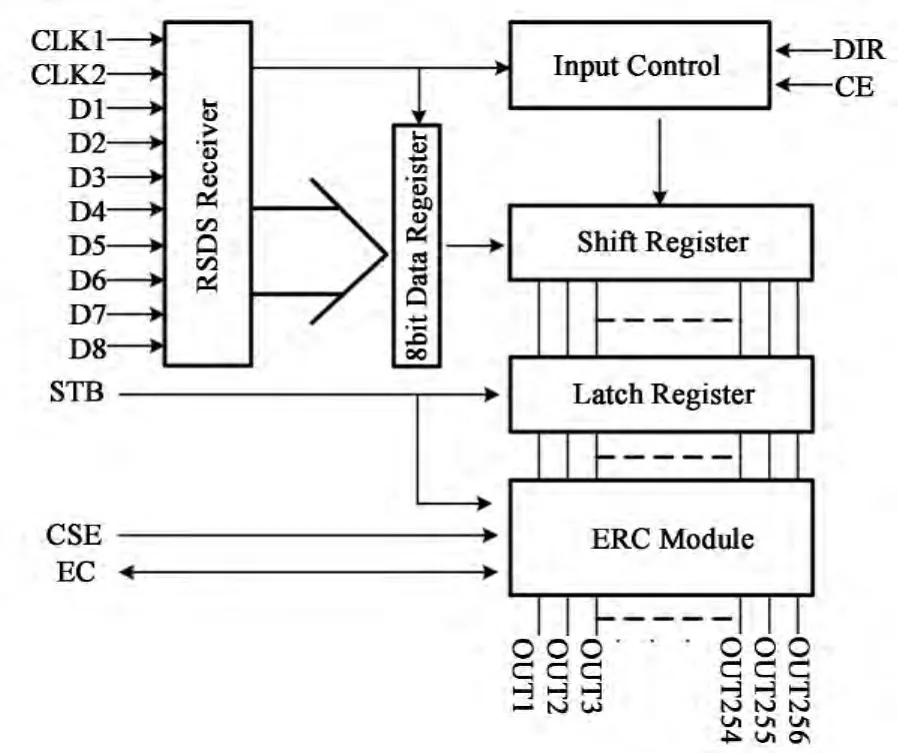

图1是目前大量应用的256路列驱动芯片的框图,D1~D8,CLK1和CLK2组成5对RSDS(Reduced Swing Differential Signaling)输 入 接口。CE信号是芯片的使能信号,当CE置高的时候,列驱动芯片能正常工作。DIR信号决定RGB数据在列驱动芯片中的传输方向,当DIR为高的时候,RGB数据信号的传输方向是OUT1→OUT256;反之,RGB数据信号的传输方向相反。STB信号是锁存器Latch的控制信号,当STB信号处于下降沿时,锁存器中的数据传输给能量恢复模块。CSE信号是能量恢复模块的使能信号,当CSE信号置高时,列驱动芯片的能量恢复电路开启。EC信号是双向端口,能量恢复的电流就经过该端口流入或者流出列驱动芯片。

图1 PDP列驱动芯片的组成框图Fig.1 Block diagram of PDP data driver IC

能量恢复模块包含有256个能量恢复基本单元,每个单元的组成原理图见图2。

图2 能量恢复模块原理图Fig.2 Schematic of energy recovery module

在图2中,能量恢复控制模块是CSE、STB和低压数据信号的逻辑组合。MP1~MP5是P型横向扩散 MOS(pLEDMOS)晶体管;MN1~MN5是N型横向扩散 MOS(nLEDMOS)晶体管;CEC是储能电容,存储的电荷来自于Vpp(高压电源端);CEC电容位于列驱动芯片的外部,没有集成在芯片内部。CL是寻址电极的等效电容。DPLD管采用100V高压CMOS工艺平台加工而成[16],DPLD管是个高压开关管,控制着能量恢复单元电路中电荷存储释放过程中的通断。MP1~MP3以及MN1~MN3共6个晶体管,组成了列驱动芯片的高压驱动电路,这6管结构是PDP列驱动芯片中广泛使用的经典结构。LV1~LV3信号是MN1~MN3晶体管的栅极驱动信号。晶体管MP4、MP5、MN4和MN5用于控制DPLD管的开启与关闭;E1和E2信号是晶体管MN4和MN5的栅极驱动信号。

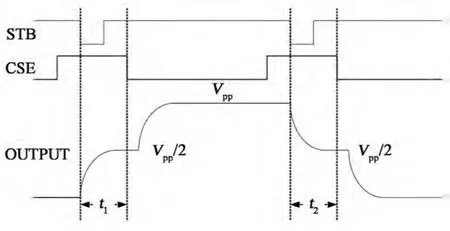

能量恢复基本单元的控制信号和OUTPUT之间的关系见图3所示。

图3 能量恢复基本单元输出波形Fig.3 Output waveform of energy recovery unit

从图3可以看出,当OUTPUT电平从零转变为Vpp时,只要STB信号处于下降沿同时CSE信号置高,电荷就会从储能电容CEC中转移到负载电容CL,经过t1时长之后,CSE信号由高变为低,OUTPUT的电平通过MP3晶体管被上拉至Vpp。当OUTPUT电平从Vpp转变为零时,只要STB信号处于下降沿同时CSE信号置高,电荷就会从负载电容CL中转移到储能电容CEC,经过t2时长之后,CSE信号由高变为低,OUTPUT的电平通过MN3晶体管被下拉至零电位。寻址电极上的电荷被转移到CEC里存储起来,上述电荷转移的过程就是列驱动芯片能量恢复电路的工作过程。

3 能量恢复效率模型

3.1 CRC分析模型

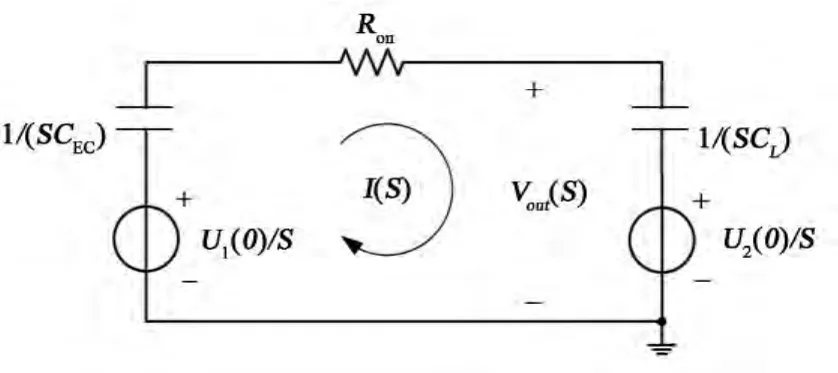

从上文分析的结果看,列驱动芯片能量恢复电路就在t1和t2时间段起作用。在t1和t2期间,DPLD处于导通状态,导通电阻Ron是DPLD管最重要的参数。t1期间,储能电容CEC通过导通电阻为Ron的DPLD管向负载电容CL充电;t2期间,负载电容CL通过导通电阻为Ron的DPLD管向储能电容CEC充电。这两个阶段属于信号与系统理论中零输入响应过程。t1和t2阶段的频域分析模型如图4所示;图中Vout(S)是OUTPUT端的电压响应;Ron是DPLD管的等效沟道导通电阻,通过测试DPLD管的I-V特性曲线,可以估算出Ron的平均值。对于漏电流能力较弱的DPLD管,t1和t2时间段的I-V 特性曲线斜率基本一样,所以t1和t2时间段的DPLD管导通电阻Ron基本一样。由频域分析模型,列方程解出Vout(S)的频域表达式;通过拉普拉斯反变换方法可以求解出的Vout(t)时域表达式,进而也就可以定量计算列驱动芯片的能量恢复效率。

图4 列驱动芯片能量恢复等效电路模型Fig.4 Energy recovery equivalent model of data driver IC

储能电容CEC和负载电容CL之间的电荷交换可以用零输入响应来求解,因为在电荷转移的过程中,没有其他电压源或者电流源引入。

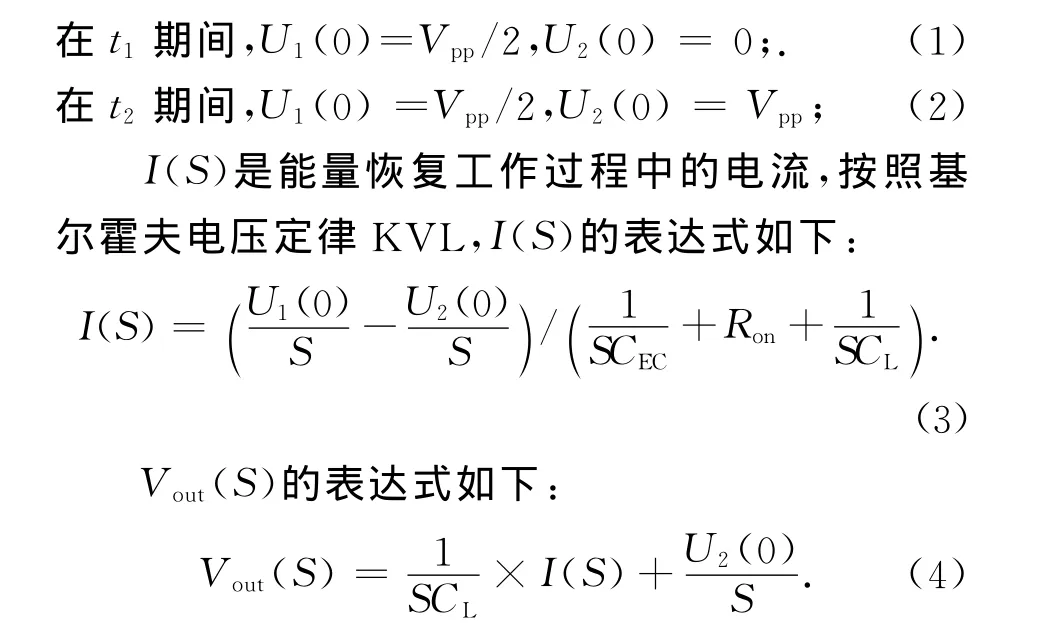

在图4中,U1(0)和U2(0)是CEC和CL的初始电压,其初始值如下:

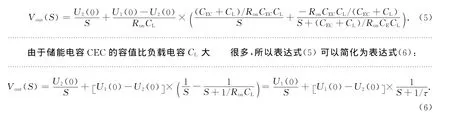

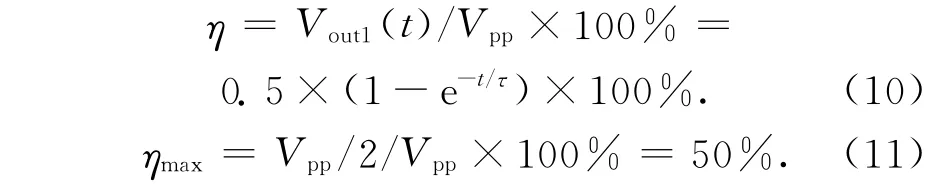

把表达式(3),代入表达式 (4),可以得到如下表达式 (5):

在表达式(6)中,τ = RonCL,Vout(t)的时域解可以用拉普拉斯反变换求解出,如表达式(7)所示:

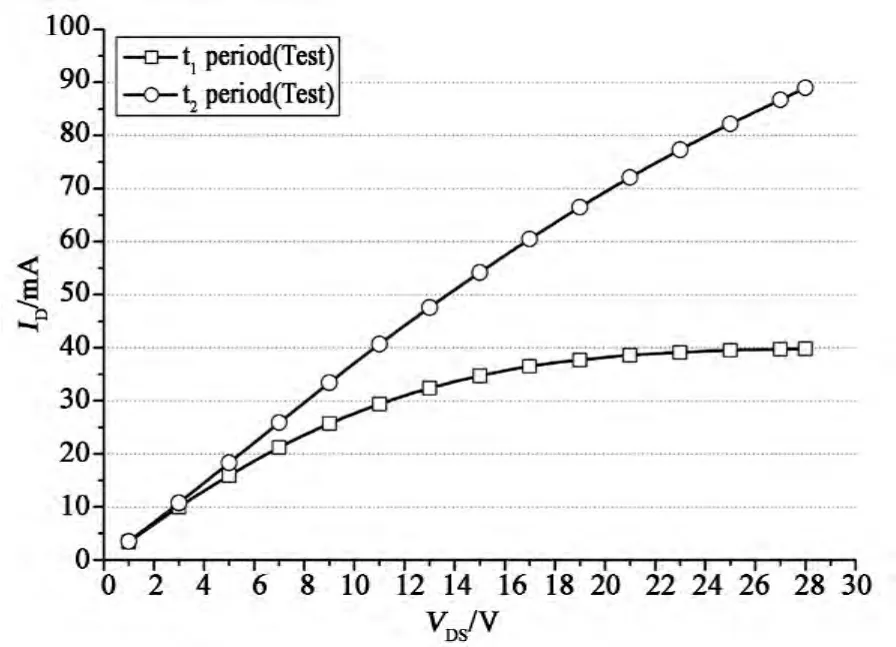

从表达式(8)可以看出:在t1期间,当充电时间t趋向于无穷大时,Vout1(t)的最大值是Vpp/2;所以能量恢复的效率表达式以及最大值表示为如下表达式(10)和(11):

在实际PDP系统中,t1和t2的值相等,它们都称之为充电时间TE。

从表达式(10)可以看出影响列驱动芯片能量恢复效率的主要因素有3个:充电时间TE、沟道电阻Ron、负载电容CL。提高列驱动芯片能量恢复的效率,可以通过延长充电时间TE,减小沟道电阻Ron和负载电容CL的大小来实现。

选取一款DPLD管沟道电阻Ron为2.7kΩ的列驱动芯片,在充电时间TE为60ns,CL=50 pF,Vpp=56V的条件下,利用表达式(8)和(9)可以计算出该列驱动芯片在充电和放电结束时列驱动芯片的OUTPUT电压分别是10.84V和45.16V,同时也可以计算出该列驱动芯片的能量恢复效率为19.4%。

3.2 压控电流源模型

上述的CRC模型适用于漏电流能力较弱的DPLD管,但是对于漏电流能力较强的DPLD管,该模型就不能同时保证充电和放电过程中的模型精度了。具体原因如下:t1和t2阶段的DPLD管的漏电流能力是不同的。按照经典CMOS理论[17],MOS管的漏电流ID随 MOS管的衬偏电压VBS不同而变化。t1和t2阶段的衬偏电压VBS是不同的。t1和t2阶段的衬底电压VB=Vpp,并且由于储能电容CEC比负载电容CL大很多,所以储能电容CEC相当于是个恒定电压源,并且电压保持Vpp/2不变。在t1阶段,CEC和CL的初始值分别是Vpp/2和0V,漏电流ID从CEC流向CL,CEC连着DPLD管的源极S端口,即VS=Vpp/2,所以t1阶段的衬偏电压VBS=Vpp/2。在t2阶段,CEC和CL的初始值分别是Vpp/2和Vpp,漏电流ID从CL流向CEC;在电荷存储过程中,CL上的电压由Vpp减小至Vpp/2;CL连着DPLD管的源极S端口,即VS=Vpp~Vpp/2,所以此时的衬偏电压VBS=0V~Vpp/2。

从上文的分析可以看出,t1阶段的衬偏电压VBS比t2阶段大。MOS管的阈值电压Vth是随着衬偏电压VBS的增大而增大的;漏电流ID的是随着阈值电压Vth的增大而减小的;所以衬偏电压VBS越大,漏电流ID就越小。

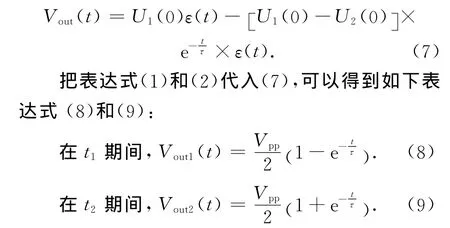

图5 列驱动芯片DPLD管的ID测试曲线Fig.5 ID test curve of DPLD transistor of data driver IC

为了便于直观分析,本文选取了一款漏电流能力较强的列驱动芯片,实测了t1和t2阶段的漏电流ID曲线,如图5所示。VDS和ID使用的是绝对值;图中可以看出,在VDS相同的情况下,t2阶段的漏电流ID比t1阶段大的要大。

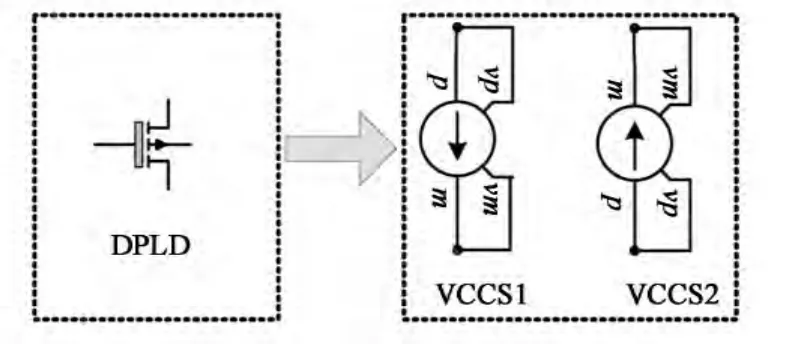

图6 DPLD管的等效模型Fig.6 Equivalent model of DPLD transistor

按照列驱动芯片能量恢复的工作机理,DPLD管在充电和放电的过程中充当一个开关的作用,并且这个开关的导通电阻跟随VDS变化。因此DPLD管可以用VCCS(压控电流源)来模拟,如图6所示。

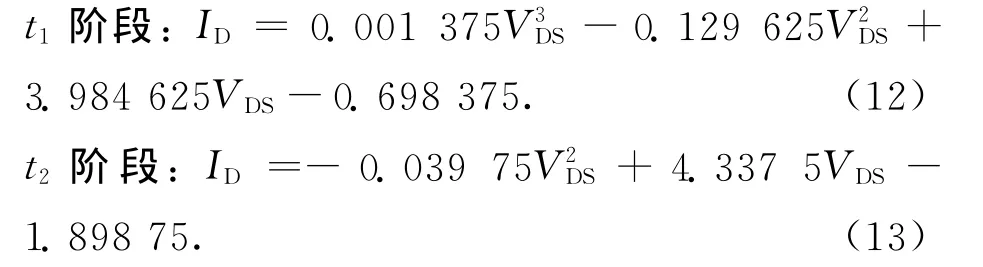

图6的ID-VDS曲线可以拟合出漏电流ID和漏源电压VDS之间的数学表达式。t1和t2阶段的ID-VDS数学表达式分别如下:

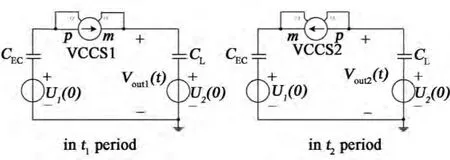

表达式(12)和(13)可以用来创建VCCS模型,并嵌入到系统仿真软件Saber中去仿真充电和放电过程的能量恢复波形。t1和t2阶段的能量恢复仿真电路如图7所示。

图7 t1和t2阶段的能量恢复仿真电路Fig.7 Energy recovery simulation circuit in t1 and t2period

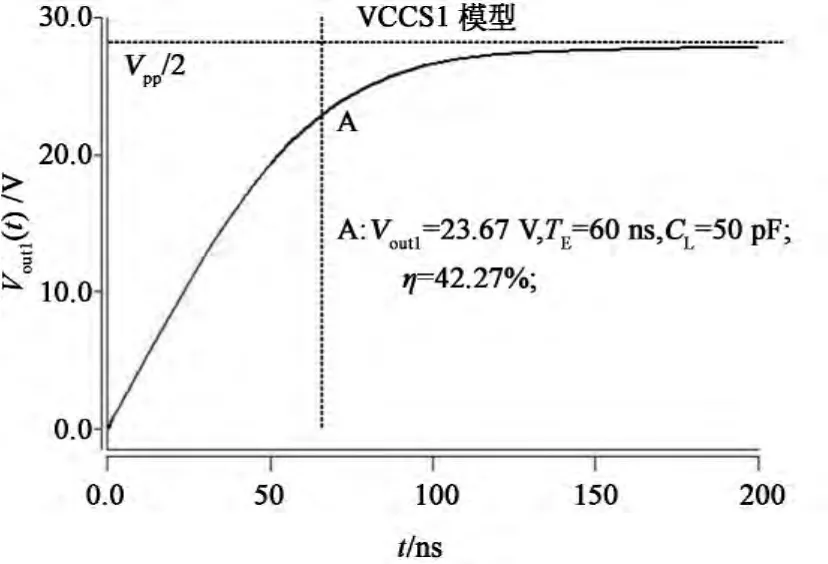

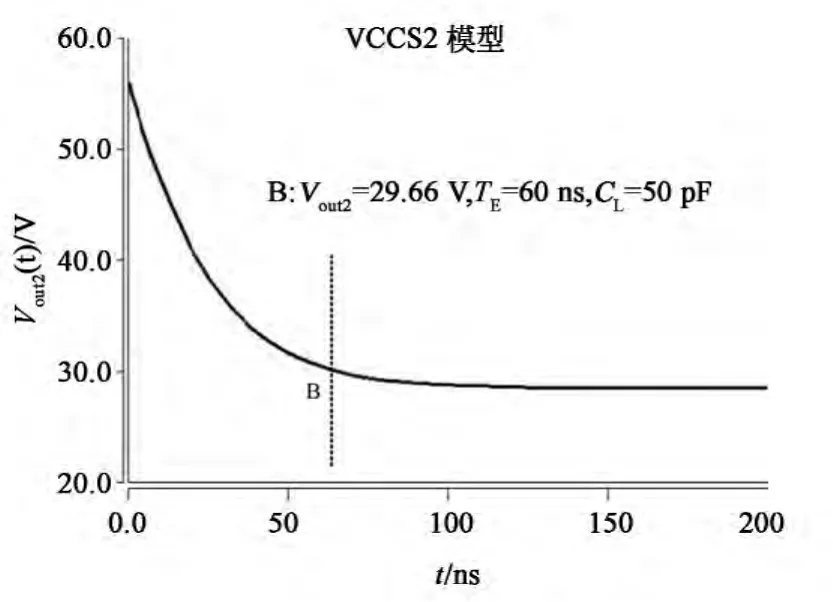

在图7中,VCCS1和VCCS2两个仿真模型分别由表达式(12)和(13)创建。U1(0)和U2(0)是CEC和CL的初始值,具体值跟表达式(1)和(2)一样。能量恢复效率η用表达式Vout1(t1)/Vpp×100%来计算。利用图7的仿真电路得到t1和t2阶段的能量恢复波形,分别如图8和9所示。

图8 t1阶段充电能量恢复波形Fig.8 Charge waveform of energy recovery in t1period

图9 t2阶段放电能量恢复波形Fig.9 Discharge waveform of energy recovery in t2period

图8和图9中的仿真条件如下:Vpp=56V,CEC=0.1μF,CL=50pF。当充电时间TE为60 ns时,充电电压Vout1(60ns)是23.672V,放电电压Vout2(60ns)是29.662V,这款列驱动芯片的ERC效率为42.27%。这个结果说明漏电流能力越强的DPLD管,对应的列驱动芯片的能量恢复效率越高。

4 测试结果

上述CRC模型和VCCS模型的精度可以用实际的PDP系统来验证。将上述两款模型分析所用的列驱动芯片分别绑定在PDP系统中,如图10所示。该PDP系统的分辨率是1366×768,尺寸是127cm(50in);寻址电极的等效电容为50pF。

图10 实测芯片能量恢复效率所用50寸PDP系统Fig.10 50in PDP system for testing energy recovery efficiency

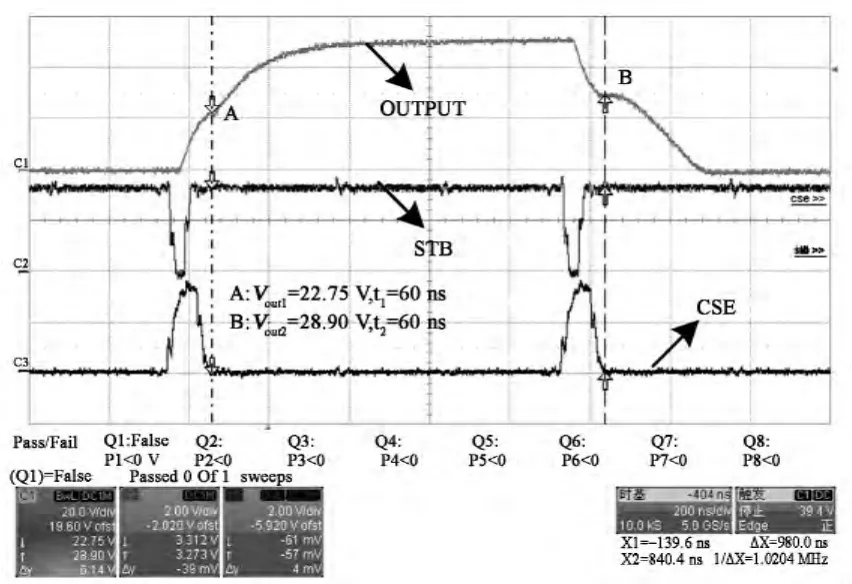

测试CRC模型和VCCS模型所用的列驱动芯片的能量恢复波形分别如图11和图12所示。

图11 CRC模型所用列驱动芯片的能量恢复波形Fig.11 Energy recovery waveform of the data driver IC used in CRC model

图12 VCCS模型所用列驱动芯片的能量恢复波形Fig.12 Energy recovery waveform of the data driver IC used in VCCS model

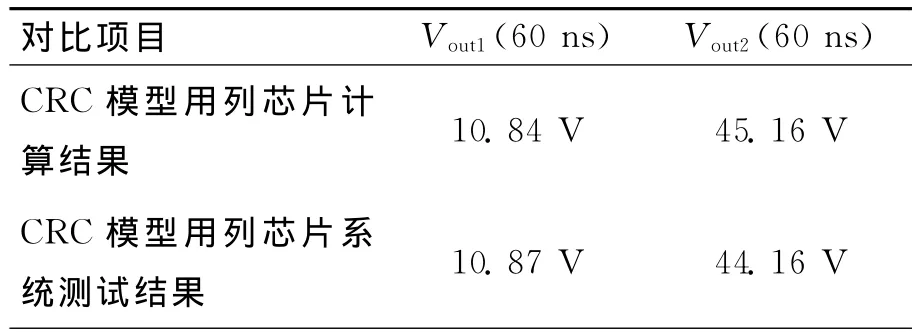

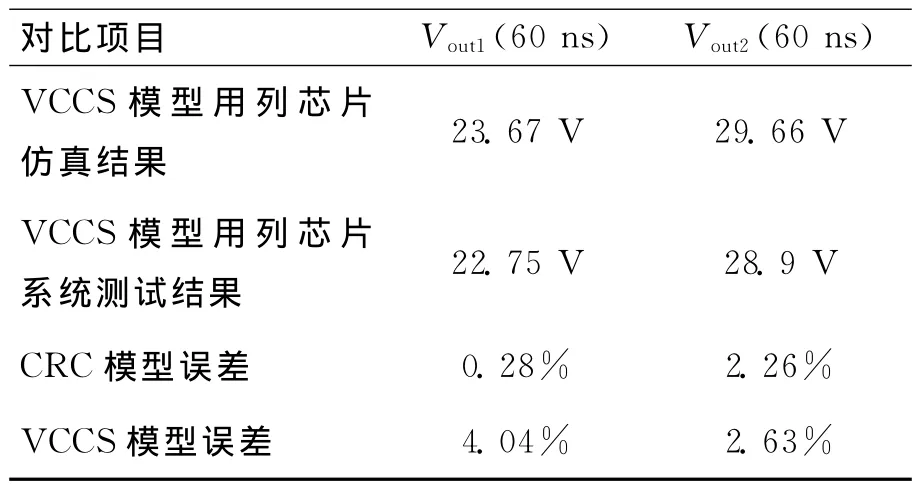

图11和12中的测试点A和B的电压值分别是能量恢复充电和放电结束时刻的数值。CRC模型分析所用的列驱动芯片的充电和放电电压分别是10.87V和44.16V,VCCS模型分析所用的列驱动芯片的充电和放电电压分别是22.75V和28.90V。将PDP系统实测结果和模型计算仿真结果对比如表1所示。

表1 PDP系统测试和模型仿真结果对比Tab.1 Comparison between system test and model simulation

续表

由表1的模型误差结果可以看出,VCCS和CRC模型的精度都很高,模型误差分别是2.26%和4.04%。

5 结 论

提出了两种模型来仿真计算PDP列驱动芯片的能量恢复效率。CRC模型有具体的解析结果,可以推论出影响PDP列驱动芯片的能量恢复效率的因素有3个:充电时间TE,沟道电阻Ron,负载电容CL。VCCS模型弥补了CRC模型在强漏电流能力的DPLD管分析上存在的不足,经过曲线拟合方式得到的漏电流ID和漏源电压VDS之间的多项式表达式可以很方便地嵌入系统仿真软件Saber中进行列驱动芯片的能量恢复波形仿真。模型仿真计算结果和实际系统测试的结果对比表明CRC和VCCS模型都具备较高的精度,模型误差分别是2.26%和4.04%。两种模型分析的结果表明,沟道电阻Ron对列驱动芯片的能量恢复效率影响很大,使用较小Ron的DPLD管可以显著提高PDP列驱动芯片的能量恢复效率。

[1]卢海平,刘伟奇,康玉思,等.超大视场头盔显示光学系统设计[J].光学精密工程,2012,20(5):979-987.Lu H P,Liu W Q,Kang Y S,et al.Design of compact optical system in wide-angle head mounted display[J].Opt.Precision Eng.,2012,20(5):979-987.(in Chinese)

[2]Kuei Y L,Paul C C.A new AMOLED pixel circuit with pulsed drive and reverse bias to alleviate OLED degradation[J].IEEE Trans.Electron.Dev.,2012,59(4):1123-1130.

[3]常锋,孙志远,王瑞光,等.LED显示图像的非均匀度校正改进方法[J].光学精密工程,2011,19(4):929-937.Chang F,Sun Z Y,Wang R G,et al.Improvement of nonuniformity correction of LED display images[J].Opt.Precision Eng.,2011,19(4):929-937.(in Chinese)

[4]王勇森,华国环,何晓莹,等.基于PDP驱动技术的行扫描芯片浪涌电压抑制方法[J].液晶与显示,2012,27(1):98-102.Wang Y S,Hua G H,He X Y,et al.Inhibition method of scan driver IC's surge voltage based on PDP driving technology[J].Chinese Journal of Liquid Crystals and Displays,2012,27(1):98-102.(in Chinese)

[5]冯庆志,王淑荣,王晓君,等.PDP荧光粉的相对亮度与VUV激发光谱的测量[J].光学精密工程,2008,16(1):59-63.Feng Q Z,Wang S R,Wang X J,et al.Measurements of relative luminance and VUV excitation spectra for PDP phosphors[J].Opt.Precision Eng.,2008,16(1):59-63.(in Chinese)

[6]Value Electronics.(2013)Samsung,panasonic plasma TVs trounce the LED competition (Again)at flat panel shootout 2013[DB/OL].Available:http://www.valueelectronics.com/.

[7]Yeoul N,Seok J H,Junkyu M,et al.A processor-based decoupled timing controller for flexible and low-cost 2D/3Dplasma display panel design[J].IEEE Trans.Consum.Electron.,2011,57(1):19-27.

[8]Xiao N Z,Chun L L,Zhen T T,et al.Analysis of the address power in PDPs with a newly developed equivalent circuit model[J].IEEE Trans.Consum.Electron.,2007,53(2):243-248.

[9]Jie L,Xiao Y H,Shen X,et al.A review of energy recovery circuits for plasma display panels[J].IETE Technical Review,2011,28(1):40-49.

[10]Sangshin K.A review of switch-mode sustain drivers with resonant networks for plasma display panels[J].IEEE Trans.Ind.Electron.,2010,57(5):1624-1625.

[11]Sang K H,Myung J Y.High performance and low cost single switch current fed energy-recovery circuit for AC plasma display panel[J].IEEE Trans.Power Electron.,2007,22(2):338-345.

[12]Sangshin K,Jin W J,Dong M L,et al.A new sustain driver with energy recovery circuit based on low-voltage components and low-voltage power supply for AC plasma display panel[J].IEEE Trans.Consum.Electron.,2008,54(3):1321-1328.

[13]Ling G M,Zhi H L,Chun L L.Energy recovery circuit with auxiliary power supply for AC plasma display panel[J].IEEE Trans.Consum.Electron.,2007,53(2):765-768.

[14]Jae K P,Hyun L D,Bong H K.Asymmetric current buildup sustainer for AC plasma display panel[J].IEEE Trans.Ind.Electron.,2008,55(4):1863-1870.

[15]Byong D C.Enhancement of current driving capability in data driver ics for plasma display panels [J].IEEE Trans.Consum.Electron.,2009,55(3):992-997.

[16]Qian Q S,Sun W F,Li H S,et al.Reliability investigations and improvements of the pLEDMOS for PDP data driver ICs[J].Semicond.Sci.Technol.,2011,26(5):1-6.

[17]Behzad R.Design of Analog CMOS Integrated Circuit [M].Boston:McGraw-Hill,2001:23-24.