基于FPGA多波束成像的声纳系统设计※

2014-08-27杨成杨康董琎琎夏伟杰

杨成,杨康,董琎琎,夏伟杰

(南京航空航天大学电子信息工程学院,南京210016)

引 言

多波束成像声纳利用了数字成像技术,在海底探测范围内形成距离—方位二维声图像,具有很高的系统稳定性和很强的信号处理能力。但是由于数字成像系统数据运算量大、需要实时成像等特点,对处理器性能要求很高。随着适用于并行处理的现场可编程门阵列(FPGA)器件的快速发展,采用大规模FPGA 为核心处理器的图像声纳,在提高了整体性能的同时,其系统结构也更加简单[1]。

1 系统概况

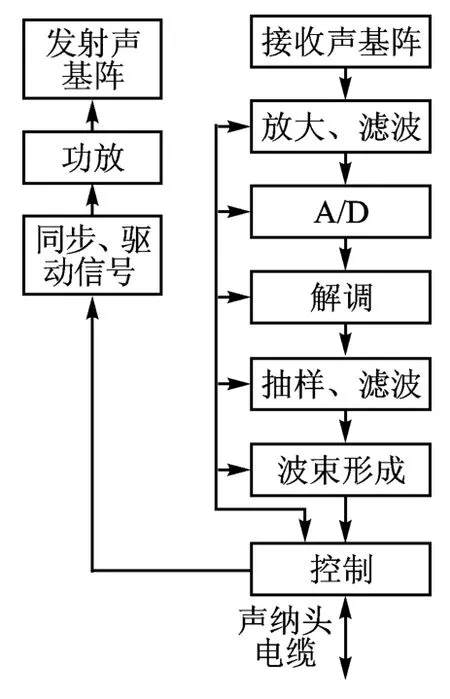

该成像声纳的电路系统处于一个密封的水密舱内部,由180路基元的收发模块、实时信号处理模块、数据传输与控制模块、电源模块以及接口板和一些连接器组成。具体声纳头内部的构成如图1所示。

图1 声纳头内部结构示意图

图中深色部分为声纳的发射和接收声基阵。系统工作时,通过发射声基阵将发射模块产生的震荡信号转换成脉冲声波发射出去,信号在水底形成反射,反射的声波信号再经接收声基阵转换为电信号,进入接收电路。接收声基阵具有180个基元,每个基元输出的回波信号通过接口板进入接收电路进行信号的调理与采集。采集后的180路数字信号再进入信号处理模块,该模块对采集数据进行复解调、抽样和数字滤波等一系列的处理,实现数字波束形成以及控制千兆网传输系统上发最终的波束数据。同时干端PC实时下发控制命令,对发射接收电路和波束形成过程进行控制。电源模块则负责给成像声纳系统中各个分模块供电。该系统的功能框图如图2所示。

系统主要技术指标略——编者注。

2 系统硬件模块设计

2.1 发射接收模块设计[2]

发射接收电路性能的好坏直接影响了多波束声纳成像的质量。发射接收模块的原理框图如图3所示。

功放电路在由频率合成器产生的工作频率信号、脉宽控制电路和功率控制电路的共同作用下,产生不同强度、不同脉宽的振荡信号,此信号加载在发射基阵上,转换成脉冲波发射出去。接收基阵通过FPGA的控制信号同步地将声纳回波转换成电信号,送入接收机前端的调理采集电路中进行小信号的前置放大、TVG/AGC放大、滤波和采集等处理,产生180 通道的数字信号。FPGA 根据PC下发的指令控制增益控制放大模块和ADC 模块,对信号进行时间增益放大和自动增益控制[3-4]。

图2 水下系统功能框图

图3 发射接收模块原理框图

2.2 数字信号处理及传输模块设计

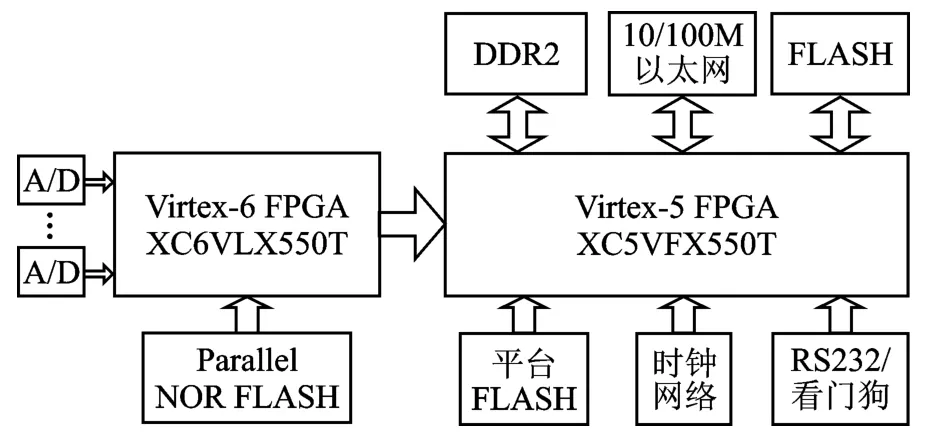

根据设计要求,数字信号处理及传输模块主要实现对回波数据进行波束形成,以及通过千兆网口上发波束数据和下发PC端的控制命令。该模块电路的总体框图如图4所示。

图4 数字信号处理模块总体框图

声纳接收模块的信号调理采集电路同时采集各接收阵元的回波信号,产生180路数字差分信号。在数信号处理模块中,对采集的信号依次作复解调、滤波抽取和波束形成等处理[5],最终输出512个波束数据。具体的信号处理流程如图5所示。

本系统采用Xilinx公司Virtex 6的XC6VLX550T芯片作为实时数据处理及波束形成的核心器件。实际算法所需的资源数量和XC6VLX550T的资源数量略——编者注。

数字信号处理模块输出的波束在100m 的量程范围内具有58.007Mbps的数据传输率,本系统采用2倍以上的设计余量,通过千兆网来实现波束数据的网络传输[6]。设计中采用Xilinx公司的Vitex-5FX70T 的FPGA 为平台,基于该芯片内部的PowerPC440硬核处理器,在该处理器上移植VxWorks操作系统,完成数据的网络传输功能。片上系统的设计框图如图6所示。

PowerPC440处理器利用PLB总线控制外围设备IP核,将FIFO 中的波束数据通过NPI接口搬移到DDR2中,达到一定的数据量后,再通过DMA 通道将数据从千兆以太网发送出去。由于FPGA 内部BlockRAM 的容量无法满足VxWorks对存储空间的需求,因此使用一片32 MB的FLASH 来存储VxWorks映像和引导程序,以及一片256 MB 的DDR 为其提供运行程序的空间,RS232串口作为调试时的输入/输出。

图5 数字信号处理流程图

图6 片上系统设计框图

该模块通过千兆网口可以接收到干端PC 下发的控制命令,实现对发射接收模块、信号调理采集模块、信号处理及波束形成模块和千兆网数据传输等模块的控制。主要的控制命令略——编者注。

2.3 系统电源设计

根据系统技术指标要求,多波束成像声纳的电源由干端电源盒产生的48V 直流电压供应,通过电缆传输到水下声纳头内部的电源板上。电源板对系统中各模块供电,既要达到功耗要求,又要满足各模块之间的电源隔离。因此电源板中采用了砖形隔离模块,产生了发射机所需的+95V、+15V 和+5V,以及接收机所需的±5.5V、+2.1 V。其中发射机电源地和接收机电源地隔离,以避免发射机噪声通过地信号进入接收机中。电源板中的电路原理图略——编者注。

接收机所需的电源通过板间接线从电源板连到数字信号处理板上。调理采集板所需的电源信号则从数字信号处理板通过层间接插座向各个调理采集小板分发。在每块调理采集小板上,上述电源信号经过低噪音的LDO线性低压降电源芯片进行稳压。信号调理采集板上电源网络略——编者注。

数字信号处理板的电源地和调理采集板的电源地通过磁珠在电源板上单点共接。数字信号处理板中电流的回流路径比调理采集板中电流的回流路径短,数字部分的地相对于系统地的阻抗更低,因此数字信号处理板地上的噪声不能通过电流回流到信号调理采集板中,从而避免了模拟信号受到数字信号的干扰[7]。从电源板过来的电源信号在数字信号处理板上通过LT 公司的LTM4600进行电平转换,得到FPGA 及其外围设备所需的电源信号。数字信号处理板上的电源网络略——编者注。接板传输到各调理采集板中进行采集,完成采集后的信号再通过板对板层叠连接器汇总到数字信号处理板中做波束形成处理,最后波束数据从以太网口输出,通过千兆网传输线上传到干端PC进行成像显示,按照这种信号通路来设计系统硬件平台的架构。

在设计时,为了减小系统体积和设计风险,将180路信号调理采集模块分成6块小板实现,每块调理采集小板按照32路设计。6块小板分成两个区,每个区层叠三层,并通过1mm 脚间距的层叠连接器将小板上采集的信号传输到数字信号处理板上。发射机放置在声纳头部,和声纳舱中的接收模块隔离,以减小相互之间的信号干扰。电源板为系统中发热量最大的设备,方案中将电源板放在系统最顶部,板上的各电源模块紧贴声纳头壁,在系统运行时可以将电源板产生的热量及时地引导到机壳上,散发到周围的水体中。系统的整体架构如图7所示。

图7 系统硬件平台架构

6块调理小板的电路结构完全一致,通过层间接插座传递信号。接插座的层叠设计需要满足在调理板堆叠次序任意的情况下,使得不同的板层输出不同通道的采集信号。图8为层叠结构示意图,图中F1、F2、F3分别代表不同接插座所在层为第一层、第二层和第三层,TOP 和BOTTOM 则表示接插座布于同层板的不同面。装配时,上一层板的BOTTOM 插座接下一层板的TOP 插头,第一层板的BOTTOM 插座插在数字信号处理板的插头上。

图8 层叠结构中的信号传递示意图

2.4 系统架构设计

如上所述,本系统的硬件平台由发射机、信号调理采集板、数字信号处理板、电源板以及一些接口板和连接器件组成。系统工作时,声纳回波信号从接收基阵上通过转图中每一层板的TOP和BOTTOM 接插座上具有相同网络标号的引脚在电气上是相连的,如P5 的“1”号引脚和P6的“3”号引脚在电气上属于同一网络“A”。

现不妨假设每一层板采集两个通道的信号,各层板采集的两个通道信号分别输入到插头P1、P3和P5的2、6脚(标有黑色圈),再由P2、P4 和P6 插座依次传递到母板上。如图所示,三层板总共采集和传输了6 个通道的信号:A、B、C、D、E和F。第一层板采集到通道A 和通道D的信号,第二层板采集到通道B和通道E 的信号,第三层板采集到通道C和通道F的信号。第三层板上TOP插头和第一层板的BOTTOM 插座信号对应关系完全一致。最后调试的时候,只要对应好网络便可以在任何一层板的接插座上测试到每一层板上两个通道采集的数据。

本系统中各层调理采集板采集32个通道的数据,通过6块层叠接插座实现板间信号的传输。

3 系统显控设计

干端软件有控制和显示的功能,控制部分主要是通过网口向水下设备发送控制命令,显示部分则是将波束形成后的数据经过处理后呈现图像,实现声纳成像的功能。考虑到图像显示的速度,采用多线程工作模式,分别创建数据接收线程和数据显示线程,同时完成成像功能。

干端主控软件对外数据接口有网口和串口两种,以太网口主要传输控制命令、参数及图形数据,三路RS232串口分别接收来自外部的定位信息如测深仪、GPS、姿态仪等。

干端主控软件接收到的波束数据为方位—距离向的二维数组,即原始一帧数据为矩形图像,其中方位向为512个波束值。而实际的数据为扇形的,以接收点为圆心,512个波束值为同一距离90度扇形上的点。所以在进行图像显示的时候需要将原始数据进行转换。具体的转换过程如图9所示。设原始矩形中的点(j,k),经过转换算法后对应扇形图像上点的坐标为(x,y),方位角α(单位弧度),则:

图9 波束图像转换示意图

其中width为扇形角对应的弦长,t为图像上近场盲区中的像素点数,pointnum 为最大量程接收到的距离向上的点数,则pointnum+t表示对应最大量程时图像距离向上的像素点。

最终的显控软件界面略——编者注。

4 测试结果及分析

系统联调结果图略——编者注。测试信号为脉冲调制正弦波,信号脉宽为0.2ms,脉冲重复周期为67ms,测试结果表明系统可正常工作,PC 端显示出测试信号所形成的512个波束,根据信号的幅度变化,窗口内的条纹信号也可相应低由暗到明。

基于此系统的水下测试结果图略——编者注。综合测试结果,水下被测目标清晰可见,其外形尺寸和实物十分吻合,系统性能优良。

结 语

文中给出了一种基于FPGA 的多波束成像声纳整机的系统设计方案。该系统基于Xilinx公司的FPGA 芯片,根据干端PC 下发的控制指令对180个基元的发射接收电路进行控制,实现对180路通道的水声信号的调理和采集,完成数字波束形成,并将波束数据通过千兆网上传至干端PC进行显示。该系统架构紧凑,整机集成度高,且测试结果表明该系统性能优良,可满足实际的水下目标探测的需要。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1]刘鑫,孙大军,田原,等.一种高速声纳实时处理系统的设计与实现[J].电子技术应用,2013,39(4):12-5.

[2]雷东,陈钧.HY1600测深仪发射接收电路的实现[J].海洋测绘,2003(6):47-48.

[3]蒋立军,杜文萍,许枫.侧扫声纳回波信号的增益控制[J].海洋测绘,2002,22(3):6-8.

[4]卢逢春,张殿伦,张宏宇.多波束条带测深仪的增益控制方案[J].海洋工程,2003,21(1):90-93.

[5]殷凤平.防蛙人声纳接收处理分机研制及其整机试验研究[D].南京:南京航空航天大学,2010.

[6]张晓燕.基于FPGA 的机载视频处理与图形生成系统设计与实现[D].南京:南京航空航天大学,2011.

[7]李维成,李鹏,刘英帅,等.印制电路板的优化布线与抗干扰措施[J].中国科技投资,2013(6):27.