基于System Generator的Rife算法的FPGA实现*

2014-06-03吕晨阳

吕晨阳,王 建

(南京船舶雷达研究所,江苏 南京210003)

频率测量在电子侦察中扮演了重要的角色[1]。随着电子技术的发展,传统的侦察接收机向着数字化、软件化方向发展[2]。传统的基于模拟电路的测频方法需要转换为数字方法实现。模拟侦察接收机中通常采用基于相位差的频率测量方法[3]。该方法在数字电路中同样可以方便地实现,但该方法对信噪比要求比较高[3]。基于数字电路的优点,可采用先进的算法实现更高的性能。Rife算法[4]是一种常用的基于DFT频谱的频率测量算法,具有算法实现容易、精度高等优点。而DFT运算可以通过FFT进行快速运算。

为保证截获概率,侦察接收机带宽不断增大,现瞬时带宽已达500 MHz[2]。传统的基于DSP和GPP的系统已难以满足实时处理的需求,采用基于FPGA的信号处理机已成为普遍的解决方法[5-7]。

FPGA设计中基于HDL和定点的设计方法不同于传统的DSP和GPP平台中基于C语言和浮点的设计方法。HDL语言语法和语言的可综合性限制了算法的实现[7-8]。 基于此,Xilinx和 Altera公司分别推出了简化FPGA数字处理系统的集成开发工具System Generator for DSP和 DSP Builder[9],快速、简易地将 DSP系统的抽象算法转化成可综合的、可靠的硬件系统,为DSP设计者扫清了编程的障碍[8-9]。

1 Rife算法

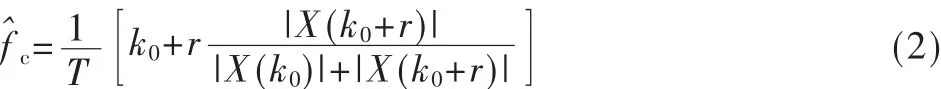

式中,当|X(k0+1)|≤|X(k0-1)|时,r=-1;当|X(k0+1)|>|X(k0-1)|时,r=1。T=NΔt。

2 System Generator

System Generator是高性能、高效的DSP算法建模工

设复正弦信号加高斯白噪声为:

式中,a为信号的幅度,Φ0为信号的初相位,fc为信号的频率;Δt为采样间隔,N为采样数;w(n)为复加性高斯白噪声。

对x(n)做FFT变换得 DFT频谱X(k),设谱线中的最大谱线绝对值为|X(k0)|,参考文献[4]中给出了利用最大谱线和次大谱线进行插值频率估计的方法(即Rife方法):具,是DSP算法与 FPGA的桥梁[7-8]。其作用如图 1所示,可在Matlab/Simulink环境下对算法以及系统进行建模,并生成相应的工程,再调用ISE进行仿真、综合、实现。

图1 System Generator的作用

Xilinx为System Generator提供了大量的信号处理模块(如 FIR滤波器、FFT)、纠错算法、存储器以及数字逻辑功能,可以在设计环境下直接调用,快速构建DSP系统。同时还支持.m文件和HDL导入[7-8]。

虽然System Generator中只有Xilinx提供的模块可以在FPGA中实现,但利用Simulink中丰富的资源可方便地生成测试向量,同时快速对结果进行准确直观的分析。考虑到资源消耗,FPGA中实现的算法以定点算法为主,定点算法的精度和范围很有限,容易发生溢出或者计算误差过大,导致算法失败[5-6]。采用传统的基于HDL和IP核的设计方法,如果早期分析得不完全,在设计后期进行修改是一件费时费力的事情,而且极易发生错误。而在System Generator环境下,采用基于模型的设计方法可以方便地实现和验证定点算法,发现问题后也容易进行修改。

3 Rife算法的FPGA设计

从第1节的Rife算法介绍可知,Rife算法以FFT运算为核心,通过频谱峰值与次峰值的插值运算计算频率值。FFT算法是一种块运算,逐帧进行,需要提供帧的起止边界。本设计中采用恒虚警模块提供帧的起止信号。FPGA中实现的Rife频率测量算法主要包含如下功能模块:快速傅里叶变换模块(FFT)、取模模块、峰值检测与锁存模块、Rife计算模块和控制模块。系统整体框图如图2所示。

图2 整体系统框图

System Generator工具中提供了FFT模块,其通过参数化配置,支持从 8点到 65 536点的基 2、基 4 FFT运算,其在FPGA中的实现对应着LogicCORE中的FFT核。使用该模块主要需要关心start信号、dv信号和输入输出信号。从恒虚警模块来的start信号通过一个上升沿指示转换开始,此时在时钟的同步下逐点将待转换数据输入,当输入的信号点数达到设定的采样点时开始FFT计算。恒虚警模块在没有检测到信号的情况下会输出0,故当信号点数小于FFT所需的点数时会自动插0。

经过一段时间的延时,dv输出高电平,指示转换完成。此时会逐点输出转换完成的频谱信号,同时xk_index输出频谱点对应的索引值。

Rife算法需要DFT频谱的幅度信息,而FFT模块输出的为I、Q两路复信号。|u|绝对值模块完成频谱的绝对值运算。在FPGA中实现诸如的运算需要占用大量的资源,其中开根号运算可采用System Generator提供的CORDIC模块进行近似运算,降低了资源的消耗。同时I2+Q2的运算可通过MCode模块完成,MCode实现了Matlab函数的有限子集,用于快速开发DSP算法,同时可生成HDL代码,用于FPGA工程应用中。

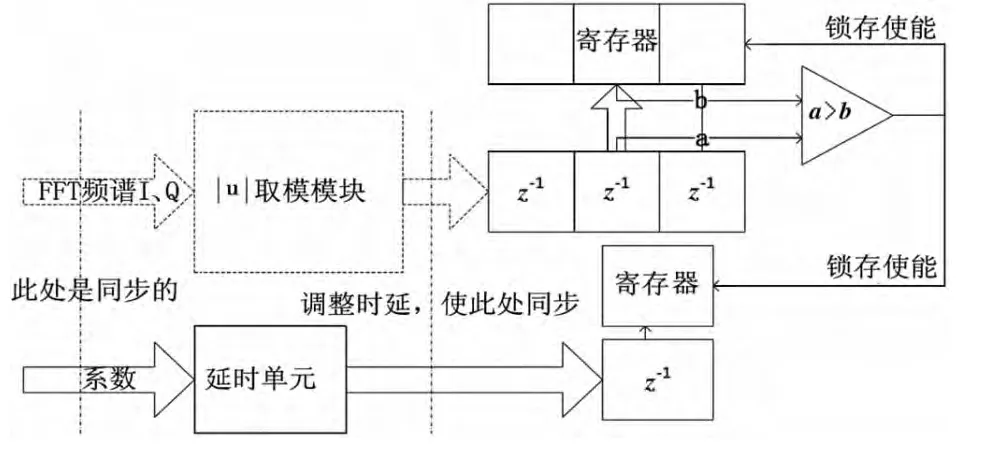

Rife算法中的峰值提取对时序要求很严格,它需要在记录下频谱峰值的同时记录下峰值对应的系数。System Generator在进行高层设计的同时还保留了底层的基本逻辑单元,可通过其构建对时序要求严格的逻辑。峰值提取模块主要包括移位寄存器、锁存器和比较器,比较器比较当前值和锁存器中的值,当发现当前值大于锁存器的值时,输出锁存使能信号,锁存当前的幅度和系数值。锁存的幅度和系数值必须对应,FFT模块输出的I、Q数据和系数是准确对应的,而当I、Q信号经过幅值计算模块后会产生时延,需要延时单元补偿时延。本设计中通过Simulink提供的多通道示波器测量了幅值测量模块的时延值,然后通过延时模块进行了补偿。具体结构如图3所示。

图3 峰值提取模块框图

图4中的Rife计算模块是本设计的核心,用于实现式(2)中的计算。图3中的峰值检测与锁存电路在锁存峰值的同时还会锁存峰值前后点的值,图4中的结构与式(2)对应,通过比较器比较峰值前后点的大小来选择插值对象。对于式中r的正负,本设计中通过可控加减法器进行实现。当r=-1时,进行减法运算;r=1时,进行加法运算。

图4 Rife计算模块框图

4 实现结果

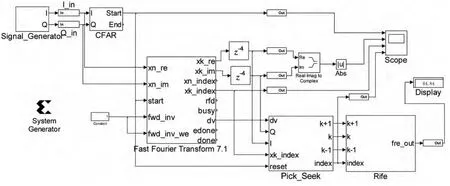

本设计硬件平台选用Xilinx公司Virtex系列中的XC6VLXT550T,系统的采样点为 128点。在 System Generator/Simulink环境中按照图2的框图进行设计,得到图5所示的算法实现图。图5中,In与Out边界内部的模块为由System Generator提供,可用硬件实现,边界之外的模块由Simulink提供。利用Simulink中的信号源产生一个叠加高斯白噪声的正弦信号,作为系统的测试激励信号,采用Simulink中的示波器观察各点信号,用Display模块显示频率值。从图5中可以看出测量的频率值为64.84。

图5 Rife算法 System Generator实现顶层图

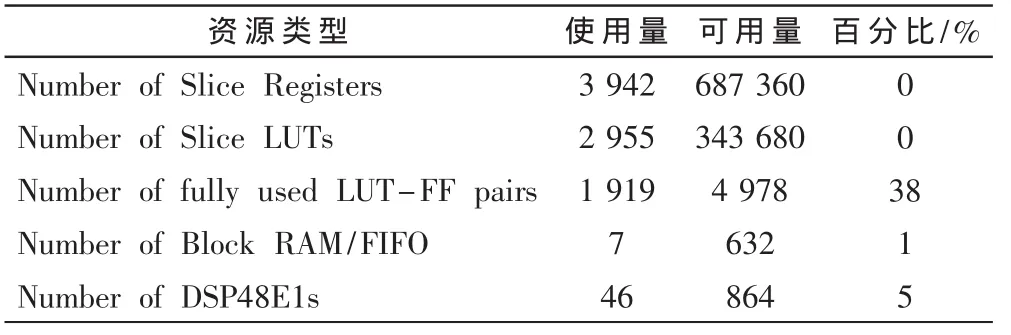

System Generator中设计的系统可用于更高层设计中,其支持生成HDL网表、NGC网表,甚至直接生成.bit文件用于FPGA的配置。其在生成网表的同时可以选择生成testbench,用于第三方的软件仿真。本设计中选择生成NGC网表。生成结果资源消耗如表1所示,综合后系统的最大运行频率为121.087 MHz。

表1 模块生成资源消耗

图6 ISE中的仿真结果图

将System Generator中生成的模块导入到ISE设计环境中。运用ISE集成的仿真软件Isim进行仿真分析,仿真结果如图6所示,图中高亮部分为频率测量值,可见其值与System Generator环境中的仿真结果相同,从而验证了设计的正确性。

本文中利用System Generator工具的便利性,在FPGA中实现了高精度频率估计Rife算法。省去了繁琐的HDL编程,从而可将更多精力集中于算法本身,同时利用Simulink环境的资源快速对设计进行验证,最后在ISE环境中完成设计并进行了验证。

[1]胡来招,电信.雷达侦察接收机设计[M].北京:国防工业出版社,2000.

[2]宋民,张琦,高梅国.一种大带宽高分辨力数字信道化接收机[J].电子信息对抗技术,2006,21(1):14-17.

[3]胡来招.瞬时测频[M].北京:国防工业出版社,2002.

[4]RIFE D C,VINCENT G A.Use of the discrete Fourier transform in the measurement of frequencies and levels of tones[J].Bell Syst.Tech.J,1970,49(2):197-228.

[5]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[6]TSUI J.Digital techniques for wideband receivers(Second edition)[M].杨小牛,译.北京:电子工业出版社,2002.

[7]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[8]Xilinx System Generator for DSP user guider v14.3[Z].USA:Xilinx Inc,2012.

[9]郝小江,黄昆.FIR数字滤波器设计及其FPGA实现[J].微型机与应用,2013,32(19):22-24.