嵌入式媒体服务器语音编解码算法集成与优化

2014-06-03李昊然谷源涛

李昊然,谷源涛

(清华大学 电子工程系,北京100084)

视频会议系统因其便捷、高效、经济、安全等特点,在政府、军事、商贸、医疗、教育等部门有着广泛的应用和需求。随着通信技术和计算机技术的不断发展,实现高集成度、低成本的嵌入式视频会议系统方案已成为可能[1]。

在基于TMS320DM8168达芬奇多核处理器的嵌入式视频会议媒体服务器的语音编解码器解决方案中,视频流的编解码处理可以使用芯片内部的专用高清视频协处理器(HVICP2)高效完成[2]。而语音流的编解码处理需要在DSP中自行设计编解码处理算法完成。此外,还需要提供一种支持ARM端远程控制并调用DSP端算法的解决方案。

本文讨论G.722编解码器在DM8168上的C674x DSP核的实现和优化策略,并将实现的G.722编解码算法封装为标准的xDM模块。此外,本文还介绍一种ARM端调用DSP执行该算法的方案:利用达芬奇技术的特性,通过远程处理器执行(RPE)机制,在ARM端成功调用DSP上的编解码模块。实验和测试结果表明,该算法和集成方案可以满足视频会议媒体服务器中的语音编解码处理的功能需求。

1 视频会议媒体服务器系统方案

本设计中,嵌入式视频会议媒体服务器主芯片选用德州仪器公司新近推出的达芬奇系列多媒体处理芯片TMS320DM8168。该芯片上集成了1个1.2 GHz的ARM Cortex A8、1个 1 GHz的浮定点兼容的 C674x DSP、3个高清视频图像协处理器 (HDVICP2)以及大量的外设单元。其中片上集成的3个HDVICP2处理器可以进行3路独立的1 080 p、60 f/s的H.264编码或解码,或者更多路低分辨率、低帧速率的编码或解码。DSP则用来做定制算法的开发。在嵌入式视频会议媒体服务器的系统设计中采用ARM+HVICP2+DSP的异质多核架构,既能够保持系统构建的灵活性,又能提供强大的处理能力。

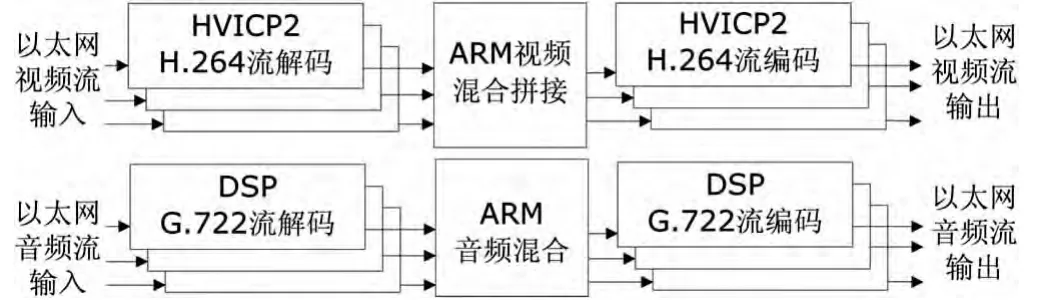

嵌入式视频会议媒体服务器的主要功能是:从会议预先商定的多个网络端口获取来自不同会议终端的视频流,并将遵循H.264编码标准的视频流解码后进行混合拼接,将拼接结果重新编码后通过指定网络端口分别发至各会议终端。语音流的处理类似,媒体服务器将来自各终端的G.722语音流解码后,完成混音叠加,再将不同的混音结果按照G.722标准编码发送至各与会终端。

本系统的处理框图如图1所示。以太网上解包获得的多路H.264视频流的编解码处理全交由片上的HVICP2处理器来完成。ARM端负责系统高层信息流控制和各通道解码后YUV视频流的混合拼接,以及语音流的混音叠加功能。本文将着重介绍DSP端的G.722编解码算法实现、优化,以及在ARM端的调用框架。

图1 视频会议媒体服务器处理框图

2 G.722编码算法和优化方案

2.1 G.722编解码器原理及实现

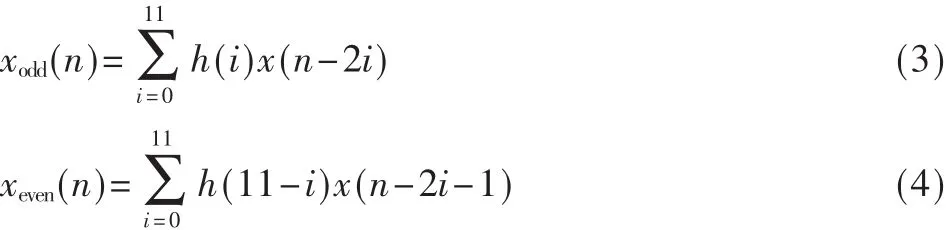

G.722编码器框图如图 2所示,G.722编码器核心部分由正交镜像滤波器QMF(Quadrature Mirror Filter)和2个结构相似的子带自适应脉冲调制编码器(Subband ADPCM)组成[3]。其中,编码器正交镜像滤波器由数字滤波器实现,将0~8 kHz的输入语音信号xin分成高(4 kHz~8 kHz)和低(0~4 kHz)2个采样率为8 kHz的子带信号xH(n)和xL(n):

其中:

式(3)、(4)中的h(i)表示正交镜像滤波器系数。2个子带信号xH(n)和xL(n)分别经过各自的子带自适应脉冲调制编码器后,经合路生成最终的G.722码流I。

图 2 G.722编码器框图

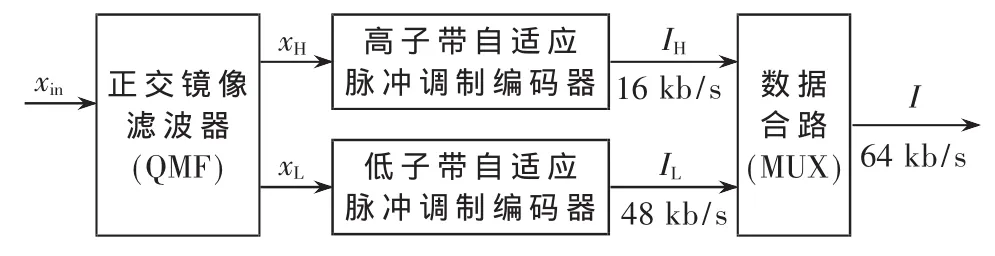

图 3所示为 G.722解码器框图[3],由于解码器的构成与编码器的构成有较强的对称性,在此不再赘述。

图 3 G.722解码器框图

2.2 G.722算法优化方案

在本设计中,系统同时存在多路语音输入,需要实例化多个G.722解码模块。为在保证实时性的同时节省计算资源,有必要研究提升算法性能的方法。由于G.722算法是在DM8168内部集成的C674x DSP内核上实现,所以可以通过改进算法的数据结构和DSP操作顺序,充分利用C674x内核的并行性和按字处理的机制,提高算法执行效率。

G.722编码器和解码器的正交镜像滤波器具有一定的对称性,结合C674x DSP的特点,可以对正交镜像滤波器进行改进。

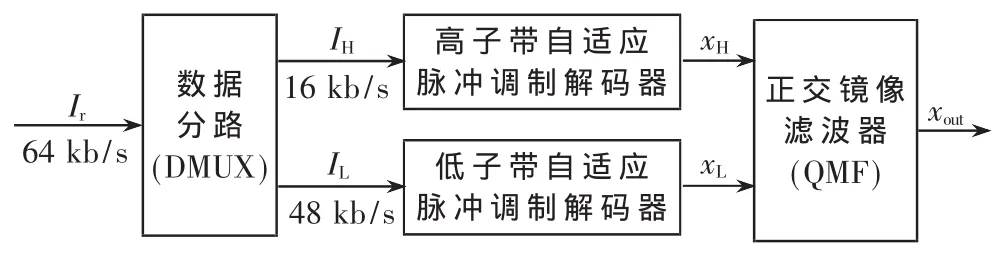

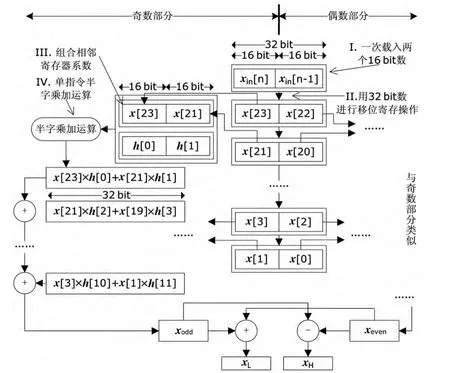

图4 G.722编码正交镜像滤波器优化结构

如图4所示,以编码端为例,编码正交镜像滤波器执行子带采样和滤波,需要按照式(1)~式(4)对输入xin进行滤波处理,生成xL和xH,即两个子带自适应脉冲调制编码器的输入。系统输入的xin为16 bit宽度的有符号整型变量,在内存空间中连续存储,可以直接使用DSP 32 bit内存访问指令,一次载入两个16 bit数据(图4中I)。同时注意到在系统中,奇数序号的移位寄存器单元(x[2k+1])仅影响奇数部分(图4左半部分)滤波器的输出xodd,偶数移位寄存器单元仅影响偶数部分(图4右半部分)滤波器输出xeven,移位寄存器工作时也可以按照32 bit数直接处理(图4中II)。此外,在进行滤波的乘累加运算时,若将两个相邻的16 bit奇数寄存器(如:x[23]和x[21])数据和两个相邻的滤波器系数(如:h[0]和h[1])数据分组后,分别以 32 bit形式存储,则可运用 C674x DSP提供的半字乘加运算DOTP2,用一个指令完成两次乘运算和一个加运算(图4中III、IV)。使用图4的结构可以减少DSP在进行编码正交镜像滤波时的所需的指令数。同样,改进手段也适用于解码部分的正交镜像滤波器。

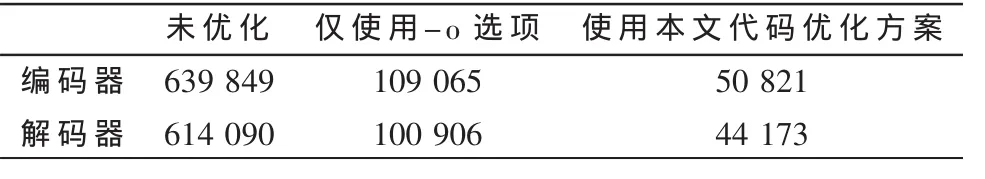

表1列出了几种不同优化情况下,编解码器核心处理函数处理长度为10 ms的单帧语音数据时,C674x DSP上的执行指令数对比。

表1 不同优化条件下的算法核心函数运行指令数

从运行指令数可以看出,结合-o2编译选项和本文提出的代码优化方案后可以大幅度缩减算法执行所需的周期,提高算法性能。

3 G.722语音处理算法集成

3.1 xDM算法标准封装

出于系统开发和集成的考虑,在达芬奇平台上进行DSP算法开发时需要遵循一定的标准规范,即TI提出的DSP算法标准xDAIS。xDAIS标准是一个庞大的体系,TI在此基础上进行扩展,提供一个轻量级的算法标准框架xDM(xDAIS for Digital Media)。使用xDM标准可以较快速地将一个开发者自定义的算法实体集成至达芬奇系统。

本设计中,按照xDMiUniversal接口标准,通过修改数据结构和上层处理调用接口,将G.722语音编解码算法代码分别封装为G722ENC和G722DEC两个xDM算法包。

3.2 远程调用机制

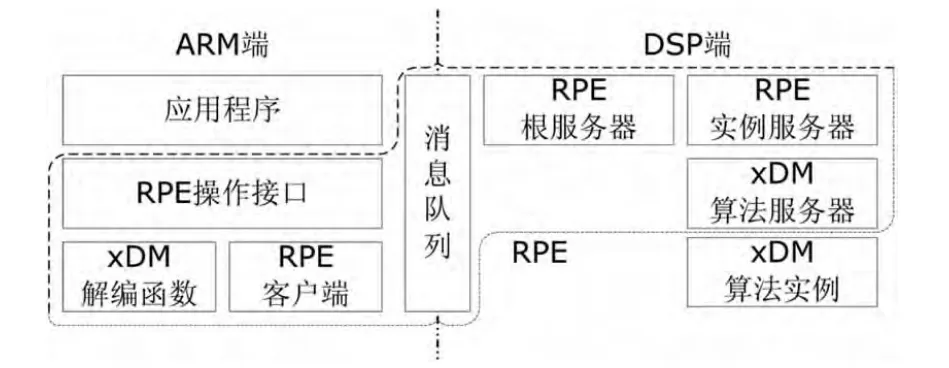

图5 远程处理器执行框架RPE

在达芬奇处理器的软件结构中,ARM负责运行嵌入式Linux操作系统,主控系统信流,调度资源并分配任务。在如上以ARM为主核的机制下,为使ARM能够调度DSP执行特定的算法操作,需要一种跨内核的算法调度机制。基于TI提供的Codec Engine(CE)方案是实现该跨核调度机制的一种方法[4]。然而,在本视频会议系统中,由于多路视频处理的需要,底层选取的多通道处理框架 McFw(Multichannel Framework)与 Codec Engine并不兼容。因此,本设计方案选取了远程处理器执行框架RPE(Remote Processor Execution)来实现ARM对DSP的跨核调度功能。

如图5所示,虚线框内是RPE框架。RPE客户端可以通过xDM解编函数将RPE操作接口执行的操作传输到消息队列;DSP端的RPE根服务器和RPE实例服务器将检查消息队列并控制xDM算法服务器,创建或调用某个特定的xDM算法实例。所以ARM调用DSP执行算法的实质是:ARM端通过本地调用RPE操作接口,RPE通过底层的消息队列机制传输操作消息,由xDM解编函数完成地址转换和参数传递,控制DSP端RPE服务器框架加载并执行指定的xDM算法实例。

3.3 编解码器集成性能测试

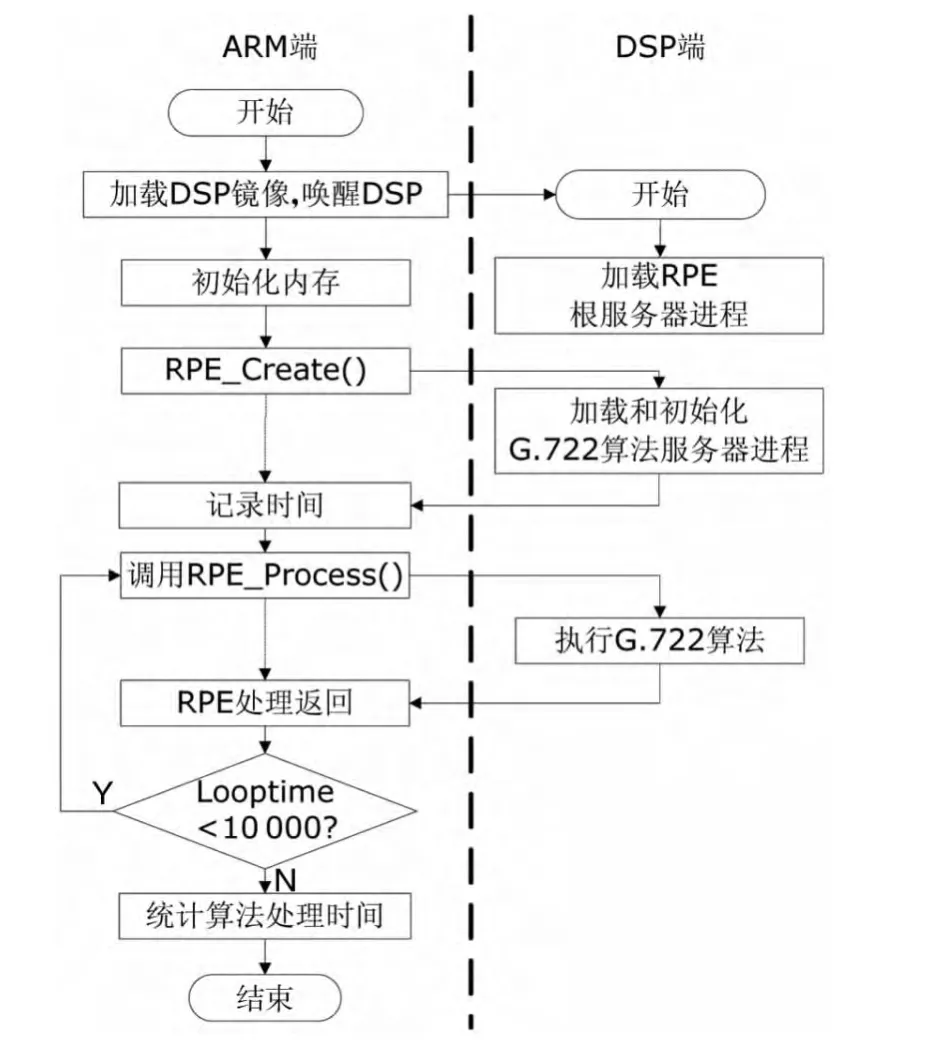

实际系统中需要在ARM端完成对G.722编解码器的调用,同时统计RPE框架和DSP语音数据处理的实际性能,以确保系统对语音处理的实时性。测试中选取的语音测试向量单帧缓存长度为10 ms,对应的编码器和解码器输入数据缓存长度分别为320 B和80 B。ARM端通过RPE机制分别调用G.722编解码模块处理对应长度缓存的10 000帧数据,统计计算RPE调用和G.722编解码所需的总时间以及处理单帧所需的平均时间。测试方法如图6所示。

图6 算法测试流程

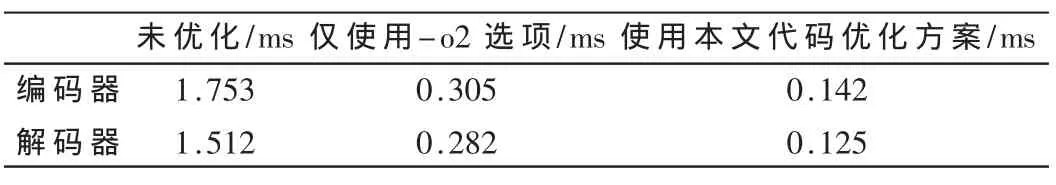

表2展示了编码器和解码器在不同优化条件下的处理单帧语音数据所需时间的统计结果对比。

表2 ARM端调用G.722算法所需单帧处理时间统计

实际测试结果表明,使用本文提出的代码优化方案后编解码处理效率有明显提高,所需计算资源减少。而且处理单帧数据所需时间远小于数据间隔(10 ms),可以满足系统实时性的要求,在多线程的处理处理条件下,可以更大程度上节省DSP的计算开销。

利用TMS320DM8168达芬奇处理器构建嵌入式视频会议媒体服务器时,视频流编解码处理可以由专用的视频协处理器HVICP2完成,而语音G.722编解码器则需要利用片上资源自行设计实现。本文介绍了G.722编码器和解码器在片内DSP核上的实现,并根据TI C674x DSP核的特点改进了正交镜像滤波的流程,提升了算法运行效率。同时还介绍了G.722编解码器的xDM算法封装技术,通过RPE架构,成功在ARM端应用程序调用DSP执行G.722编解码。编解码实验和嵌入式视频会议系统实际运行测试表明,该集成框架和编解码算法处理数据速度快,精度高,完全能够满足嵌入式视频会议系统中多路语音实时编解码处理功能的要求。

[1]TALLA D,GOLSTON J.Using DaVinci technology for digital video devices[J].IEEE Journals&Magazines,2007(40):53-61.

[2]Texas Instrument Incorporated.TMS320DM816x DaVinci video processors(Rev D)[R].Dallas:Texas Instruments Inc.2013.

[3]ITU.Recommendation ITU-T G.722:7 kHz audio-coding within 64 kbit/s[S].Geneva,2012.

[4]Kong Xiangping,Lin Hezhi,Huang Lianfen.Implementation of G.729 codec based on DaVinci technology[C].International Conference on Multimedia and Information Technology,Chiang Tailand,2008:11-40.

[5]陈发堂,郭丽强.ARM+DSP嵌入式系统 BootLoader在LTE中的实现[J].电子技术应用,2013,39(5):25-28.