SOPC型芯片的侧信道安全性分析*

2014-02-09胡江溢杜新纲孙乐昊胡晓波

胡江溢,杜新纲,孙乐昊,胡晓波

(1.南京南瑞集团公司,江苏南京211106;2.国家电网公司营销部,北京100031;

3.武汉大学,湖北武汉430072;4.北京南瑞智芯微电子科技有限公司,北京100192)

SOPC型芯片的侧信道安全性分析*

胡江溢1,杜新纲2,孙乐昊3,胡晓波4

(1.南京南瑞集团公司,江苏南京211106;2.国家电网公司营销部,北京100031;

3.武汉大学,湖北武汉430072;4.北京南瑞智芯微电子科技有限公司,北京100192)

侧信道分析方法已成为不同类型密码芯片的主要威胁,现有国际上及国内针对侧信道分析提出的测试平台主要基于智能卡和FPGA芯片两种,且这些测试平台只针对某种特定芯片进行安全性测试。面对软件、硬件及软硬件协同的密码芯片设计,文中提出一种基于SOPC芯片的侧信道测试平台,可以同时在一块芯片上模拟以上三种类型的密码芯片设计,极大降低了测试成本。同时,文中针对AES加密算法,对软件、硬件及软硬件协同设计下的密码实现安全性进行较详细分析,其分析结果对密码芯片设计者是一个有力的辅助。

侧信道分析 SOPC芯片 密码芯片

0 引 言

现如今,嵌入式系统软件和硬件的联系越来越紧密,其应用对功能和性能的需求也越来越高[1]。SOPC型芯片通过把ARM处理器嵌入到传统的FPGA芯片中,形成一个软硬件协同的芯片平台,能够充分发挥软硬件各自的优势,有效缓解了市场日益增长的需求。但是芯片在运行过程中往往会泄露与敏感数据相关的功耗、电磁辐射等信息[2],所以作为密码芯片而言,其抗侧信道分析能力格外重要。美国联邦信息处理标准FIPS 140-3[3-4]定义了5个级别的安全要求,其中明确了安全芯片必须具备抗侧信道分析能力。SOPC型芯片作为一种新型加密

芯片的载体,有必要对其抗侧信道能力进行分析和评估。

1 SOPC上的AES加密算法设计实现

1.1 AES加密算法

AES算法[5]是一种分组算法,其明文长度固定为128比特,密钥长度则可以128,192或256比特。对于长为128比特的明文,AES会将它视为以8比特为单位的4×4的矩阵,操作都会在这个矩阵上进行。在加密的过程中,AES首先进行密钥扩展(Key Expansion)操作,产生每一轮的轮密钥;之后进行轮变换,AES每一轮的加密循环(除最后一轮外)均由4个不同的操作组成:

1)S盒变换(SubBytes)通过一个非线性的替换函数,每一个字节被替换成对应的字节。

2)行移位(ShiftRows)将矩阵中的每一行进行循环移位。

3)列混合(MixColumns)对矩阵的每一列进行线性变换,产生混合的效果。

4)子密钥加(AddRoundKey)矩阵的每一个字节都与该轮相应的轮密钥进行异或运算。

AES最后的一个加密循环中省略MixColumn步骤。根据不同的密钥长度,AES加密循环的轮数也有所不同,密钥长度分别为128,192或256比特时,循环次数分别为10,12或14。具体流程见图1。

图1 AES加密流程Fig.1 Flow diagram of AES algorithm

1.2 Xilinx的SOPC芯片结构

本文使用了Xilinx公司推出的ZYBO开发板作为研究平台。ZYBO开发板上搭载有Zynq-7000平台[6],该平台将专用的嵌入式处理器PowerPC、Cortex-A9硬核处理器嵌入到FPGA芯片中,形成一个SOPC型的FPGA芯片,如图2所示。

图2 Zynq-7000平台结构Fig.2 Structure of Zynq-7000 platform

这种结构使得一块芯片上同时具有多核处理器的处理系统(PS,Processing System)和可编程逻辑(PL,Programmable Logic)。此外,Xilinx还引入了AXI接口协议,用来描述处理器系统和可编程逻辑之间的数据传输方式。AXI总线作为一种高性能、高带宽、低延迟的片内总线,在经过开发人员简单地配置之后,可以实现芯片内部器件的互联,并且解决了ARM核与FPGA通信的瓶颈问题。

1.3 SOPC编程工具和设计流程

Xilinx公司提供了基于Vivado的一整套软件和硬件协同处理和设计的工具[6]。硬件设计主要使用Vivado HLS工具。HLS可以把开发人员编写的C语言代码转换成硬件描述语言,从而快速地完成HDL设计输入、综合、仿真和实现,以及处理器与可编程逻辑接口的配置。软件设计主要使用Xilinx SDK工具,在这个工具中,开发人员可以完成软件代码的编写、编译和链接过程。此外,Xilinx SDK工具能将软件代码生成的ELF文件代码插入到生成的FPGA比特流文件中,供开发板下载使用。

1.4 SOPC软硬件协同设计结构

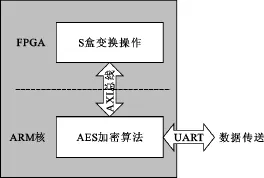

根据SOPC型芯片内部构造的特点,本文采用了如图3所示的软硬件协同的AES算法结构。芯片通过内部的UART模块接收从上位机发送过来的16个字节的明文数据;数据在处理器上完成AES (除S盒变换之外)正常的加密操作;S盒变换的操作在FPGA中进行,整个操作以查找表的方式实现, S盒查找表存储在FPGA芯片的BRAM资源中; ARM核与FPGA通过芯片内部的AXI总线完成数据交换;加密的结果再次通过内部的UART模块回传给上位机。

图3 AES算法的软硬件协同设计结构Fig.3 Structure of co-designed AESalgorithm

2 侧信道分析方法

2.1 PA分析原理

侧信道分析方法是一种利用设备运算过程可能泄露的物理信息(如功耗、声音、电磁辐射等),分析并获取设备敏感信息的方法。常见的侧信道分析方法主要分为差分功耗分析(DPA,Differential Power Analysis)[7]和相关功耗分析(CPA,Correlation Power Analysis)[8]两种。

DPA会确定一种选择函数,然后根据猜测密钥将采集到的功耗曲线划分为两个不同的集合。对两个集合中的数据分别计算其平均功耗曲线,将平均功耗曲线作差得到采集数据的差分功耗曲线。若差分曲线上会出现明显的尖峰,说明此时猜测密钥与真实密钥相同。

CPA是对DPA方法的一种改进,CPA会对已知明文和猜测密钥进行计算,形成一个中间值矩阵,之后按照相应的泄露模型(汉明重量、汉明距离等)得到假设功耗曲线。由于假设功耗曲线是对设备实际功耗曲线的一种预测,两者存在一定的相关性,所以通过比对两条曲线可以分析出目标密钥。

2.2 曲线预处理

在实际采集的过程中,功耗曲线由于种种原因(电路噪声信号较大,门电路延时不固定等)会出现时域上无法对齐的现象。对于没有对齐的功耗曲线直接实施侧信道分析方法,其分析效果往往并不理想。为此,在实施正式的侧信道分析之前,我们需要把采集到的功耗曲线进行预处理。

常见的曲线预处理方法主要有曲线静态对齐和傅里叶变换两种方法。曲线静态对齐方法首先确定分析区间,然后会将采集到的功耗曲线所有位置与分析区间内的基准曲线依次进行匹配。选定位置后,分析者平移功耗曲线以确保在相同的时间点上,功耗曲线与基准曲线所对应操作相同。

而傅里叶变换FFT则是一种将功耗曲线从时域上转换到频域的方法。根据信息理论可知,信号经傅立叶变换,其总能量保持不变,符合能量守恒定律。因此,利用傅里叶变换可以在把功耗信号从时域变换到频域的同时,使得信号依然存在且不受到时域信号中随机时延的影响,即DPA和CPA的时域信号差异在频域信号中一样能够得到体现[9]。

2.3 安全性评测指标

本文研究的重点主要集中于SOPC型芯片的抗侧信道分析能力,根据相关论文和研究成果[10-13],选择了以下4种评价指标:曲线消耗(CT,Consumption of Trace)、攻击时间(AT,Attack Time)、攻击成功率(SR, Success Rate)以及猜测熵(GE,Guessing Entropy)。

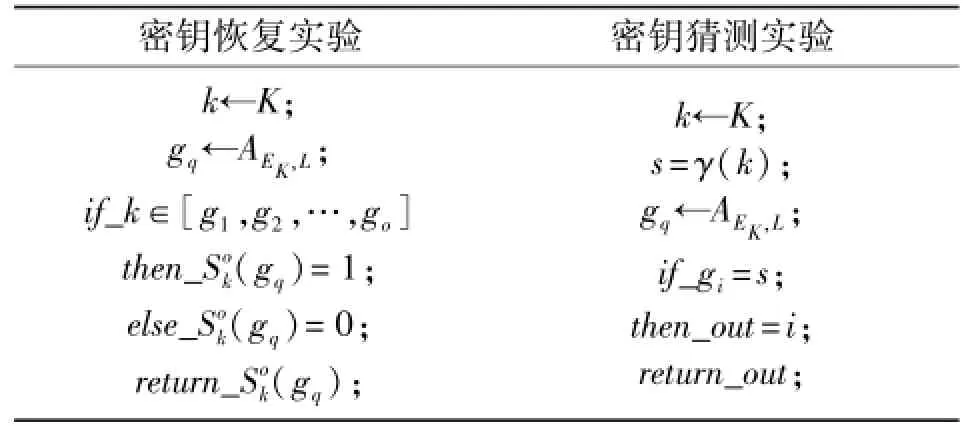

对于侧信道分析,本文定义实际加密操作为EK={Ek(.)}k∈κ,K为密钥,(EK,L)表示实际运算的与泄漏函数L的关系。一般而言,攻击者会将密钥拆分成子密钥进行攻击,子密钥空间远小于原始密钥空间。假设攻击者所进行的攻击为AEK,L,时间复杂度为τ,空间复杂度为m,攻击需要的功耗曲线数为q,对应的数据集合为1q=[l1,l2,…,],候选密钥集合为gq=[g1,g2,…,](如果子密钥长度为8,则为256)。在攻击中,攻击者可能会选取多个密钥作为攻击结果,如对于CPA攻击者则选择相关性系数前o个最大值对应的子密钥作为攻击结果,将这样的攻击结果集合定义为[g1,g2,…,go],最佳攻击结果即为g1。这样的密钥恢复实验称为o阶密钥恢复实验。

(1)曲线消耗

攻击成功意味着最佳攻击结果g1与目标密钥相同,而曲线消耗是指g1为目标密钥且稳定时所消耗的最少曲线数量。

(2)攻击时间

攻击时间是最基本的评价指标,即从攻击开始到攻击结束所消耗的时间,是攻击效率的直观的体现。

(3)攻击成功率

攻击成功率和猜测熵相比之下比较复杂,为了更加清楚地说明两个指标的含义,本文定义如表1的两组实验:对o阶子密钥恢复实验为,密钥猜测实验。

表1 密钥恢复与猜测实验对比Table 1 Comparison of key recovery and guess

根据上文的说明,对于攻击结果集合[g1,g2,…,go]和子密钥的候选集合S,o阶攻击成功率为:

(4)猜测熵

猜测熵决定了抵抗有针对性的密码猜测攻击的能力,主要用来衡量完成一次攻击的剩余工作量。根据密钥猜测实验,将猜测熵定义为:

当攻击成功率不高时,猜测熵直接说明攻击者的平均剩余工作量。

2.4 针对SOPC加密芯片侧信道分析

对于一个嵌入式应用而言,其许多功能既可以由软件完成也可以由硬件完成,而我们知道硬件的运行速度快,软件的开发成本低,所以SOPC型芯片可以兼顾软件和硬件的优势,实现嵌入式应用的最优化。然而要想实现软硬件的协同设计,处理器和FPGA之间必须进行数据的传输和交换,从而有可能产生侧信道信息的泄露问题。

如图4所示,本文采用了软硬件协同的AES算法的设计方案。待查表的数据(以AES第一轮加密操作为例,data1=plaintext⊕key)从处理器通过AXI总线传输到FPGA中。之后,FPGA将查表的结果(data2=Sbox(plaintext⊕key))通过AXI总线返回到处理器中进行后续的操作。包含有密钥的敏感信息在片内的AXI总线上不加保护地进行传输,很有可能存在侧信道信息的泄露,本文着重对这个可能的侧信道信息泄露点进行分析。

图4 SOPC型加密芯片的侧信道泄露点Fig.4 Side-channel leakage point of SOPC crypto chip

3 实验及分析

3.1 实验平台的介绍

本文实验使用Xilinx公司的ZYBO开发板作为AES算法的实现平台,来分析软硬件协同设计的

AES算法可能的侧信道信息泄露情况。

实验平台如图5所示,可分为三大模块。SOPC型芯片模块由ZYBO板构成,能够正常运行AES算法。ZYBO板通过串行接口与上位机相连,完成接发数据的功能;通过GPIO端口为示波器提供采集数据的触发信号。侧信道信息采集模块主要有示波器和近场探头组成,采集芯片周围的电磁辐射信号,并传输给上位机。通用PC模块由上位机和侧信道分析程序组成,能够控制示波器和ZYBO板工作,并对采集到的数据进行分析。本次实验中,上位机控制ZYBO执行AES算法10000次,并控制示波器采集完整的10个轮次的加密操作。

图5 实验平台示意Fig.5 Structure of experimental platform

3.2 实验结果的分析

本文对实验平台采集得到的功耗曲线进行了分析。这里我们以AES算法第一轮加密操作的第一个字节的S盒变换为例说明侧信道分析结果。图6是该字节的DPA分析的差分曲线。从图6中,可以明显地看到曲线出现明显的尖峰,对应第一轮密钥的第一个字节0x00。

图6 AES第一轮第一个密钥字节k1的DPA差分曲线Fig.6 DPA differential curve ofk1in the first round

根据上面的说明,差分功耗曲线上存在尖峰则说明此时的猜测密钥和正确密钥相同。由此可知, DPA对该AES算法设计的侧信道有效,也就是说这种软硬件协同的AES算法设计存在着侧信道信息的泄露问题。

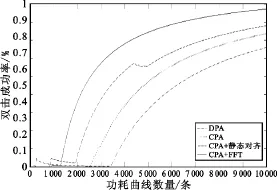

整个实验中,本文还尝试了CPA、静态对齐之后CPA和傅里叶变换FFT之后CPA的密钥恢复效果(AES算法第一轮加密操作的第一个字节的S盒变换)。图7和图8分别是在不同分析方法下的攻击成功率和猜测熵对比图,两幅图横坐标表示使用的功耗曲线条数,纵坐标分别对应了攻击成功率和猜测熵。可以看到,随着曲线条数增加,攻击成功率呈上升趋势,猜测熵呈下降趋势,说明了侧信道分析方法的有效性。

图7 不同分析方法的攻击成功率Fig.7 Success rate under differentanalyses

图8 不同分析方法的猜测熵Fig.8 Guess entropy under different analyses

4 结 语

本文针对应用前景广阔的SOPC型芯片,首次实现了ARM处理器与FPGA芯片之间数据总线上的侧信道信息分析工作。对于嵌入式应用而言,为了充分提升板卡的性能,系统开发者需要进行合理的软硬件的协同设计,而速度、成本以及安全是其考

虑的关键因素。本文在ZYBO开发板上对软硬件协同设计的AES算法进行了侧信道信息的分析。实验结果表明,常规的侧信道分析方法可以有效地提取芯片内部数据总线上的敏感信息,并且选择合适的预处理方法,能提高分析的效率。

[1] 熊光泽,詹瑾瑜.嵌入式系统软/硬件协同设计技术综述[J].计算机应用,2006,26(04):757-760.

XIONG Guang-ze,ZHAN Jin-yu.Survey on Techniques of SoC Hardware/Software Co-design[J].Journal of Computer Applications,2006,26(4):757-760.

[2] 王松,陈曼,韩炼冰,等.FPGA上抗侧信道攻击的密码算法实现[J].通信技术,2014,47(09):1100-1103.

WANG Song,CHEN Man,HAN Lian-bin,et al.Side-Channel Resistance Implementation for FPGA[J].Communications Technology,2014,47(09):1100-1103.

[3] National Institute of Standards and Technology.FIPS PUB 140-3,Security Requirements for Cryptographic Modules[S].USA:NIST,2014:39-40.

[4] Ravi S,Raghunathan A,Kocher P,et al.Security in Embedded Systems:Design Challenges[J].ACM Transactions on Embedded Computing Systems(TECS), 2004,3(3):461-491.

[5] 张焕国,王张宜.密码学引论[M].武汉:武汉大学出版社,2009:69-89.

ZHANG Huan-guo,WANG Zhang-yi.Introduction to Cryptology[M].Wuhan:Wuhan University Press, 2009:69-89.

[6] 何宾.Xilinx All Programmable Zynq-7000 SoC设计指南[M].北京:清华大学出版社,2013:15-20.

HE Bin.Xilinx All Programmable Zynq-7000 SoC design guide[M].Beijing:Tsinghua University Press,2013: 15-20.

[7] Kocher P,Jaffe J,Jun B.Differential power analysis [C]//Advances in Cryptology—CRYPTO'99.Berlin Heidelberg:Springer,1999:388-397.

[8] Brier E,Clavier C,Olivier F.Correlation Power Analysis with a Leakage Model[M].Cryptographic Hardware and Embedded Systems-CHES 2004.Berlin Heidelberg: Springer,2004:16-29.

[9] Agrawal D,Archambeault B,Rao JR,et al.The EM side—channel(s)[M].Cryptographic Hardware and Embedded Systems-CHES 2002.Berlin Heidelberg: Springer,2003:29-45.

[10] MacéF,Standaert FX,Quisquater JJ.Information Theoretic Evaluation of Side-Channel Resistant Logic Styles [M].Berlin Heidelberg:Springer,2007:427-442.

[11] Regazzoni F,Cevrero A,Standaert F X,et al.A Design Flow and Evaluation Framework for DPA-Resistant Instruction Set Extensions[M].Cryptographic Hardware and Embedded Systems-CHES 2009.Berlin Heidelberg:Springer,2009:205-219.

[12] Standaert F X,Archambeau C.Using Subspace-based Template Attacks to Compare and Combine Power and Electromagnetic Information Leakages[M].Cryptographic Hardware and Embedded Systems-CHES 2008.Berlin Heidelberg:Springer,2008:411-425.

[13] Veyrat-Charvillon N,Gérard B,Standaert F X.Security Evaluations beyond Computing Power[C]//EUROCRYPT.Berlin Heidelberg:Springer,2013:126-141.

胡江溢(1960—),男,博士,高级工程师,主要研究方向为电力营销管理技术,信息安全;

HU Jiang-yi(1960-),male,Ph.D., senior engineer,mainly engaged in powermarketing management technology and information security.

杜新纲(1966—),男,硕士,高级工程师,主要研究方向为电力营销管理技术,信息安全;

DU Xin-gang(1966-),male,M.Sci.,senior engineer, mainly engaged in power marketing management technology and information security;

孙乐昊(1992—),男,在读本科,主要研究方向为计算机技术;

SUN Le-hao(1992-),male,undergraduate,majoring in computer technology;

胡晓波(1977—),女,学士,工程师,主要研究方向为应用密码学,密码芯片。

HU Xiao-bo(1977-),female,B.Sci.,engineer,majoring in applied cryptography,crypto chip.

Side-Channel Security Analysis of SOPC Chip

HU Jiang-yi1,DU Xin-gang2,SUN Le-hao3,HU Xiao-bo4**

(1.NARIGroup Corporation,Nanjing Jiangsu 211106,China;2.China State Grid Corp Marketing Department,Beijing100031,China;3.Wuhan University,Wuhan Hubei430072,China;

4.Beijing NARISmartChip Microelectronics Company Limited,Beijing100192,China)

Side-channel security analysis now becomes themajor threatof different cipher chips.The exist testing platform of side-channel analysis athome and abroad ismainly based on the smart card and FPGA chip,and this platform merely evaluates the security of certain chips.Duo to thatno test platform could evaluate the software,hardware and software and hardware co-designed cipher chip,the side-channel test platform based on SOPC chip is proposed,and the proposed platform could simulate the design of above three different cipher chips at the same time on a chip,and thus greatly reduce the testing cost.Moreover, aiming at AESencryption algorithm,this paper analyzes in detail the security of these three different implementations,and the analysis result is beneficial to cipher-chip designers.

side-channel analysis;SOPC chip;cipher chip

TP309.7

A

1002-0802(2014)12-1445-06

10.3969/j.issn.1002-0802.2014.12.020

2014-09-20;

2014-11-13 Received date:2014-09-20;Revised date:2014-11-13

北京市科技计划(No.Z111104062210001),国家自然科学基金(No.61472292,No.61202386)

Foundation Item:Project supported by Beijing Science and Technology Plan(Z111104062210001);National Natural Science Foundation of China(No.61472292,No.61202386)