IC-725A短波电台本振频率的高稳定度改进*

2014-01-16葛勤革张曙霞蒋宇中张涛涛

葛勤革 张曙霞 蒋宇中 张涛涛

(1.海军司令部信息化部 北京 100841)(2.海军工程大学电子工程学院 武汉 430033)

1 引言

开展短波信道传播特性探测,研究电离层与电磁波的相互作用是研究无线电波的传播过程、电离层特性及其状态的重要手段,同时也为空间物理、航空航天、国防军工等现代科技领域的发展提供理论基础[1]。为缩短短波信道探测系统硬件的研发周期,在硬件的设计中尽量使用市面现有设备。其中,短波电台选用IC-725A,它是ICOM比较经典的短波电台之一,短波全波段收发,内部布局合理;具有语音压缩功能;射频增益控制可增加弱信号时的接收灵敏度,减少强信号时引起的失真;内置数字式S/RF测试仪表;双变换超外差式接收系统,曾经列装部队。尽管IC-725A性能较好,但缺点是本振的自频偏较大。根据实测,两部不同电台的32MHz本振输出基准频率偏差可达100Hz。这个频差对点短波通信来说是可以容忍的,然而,对于短波信道测量来说却是致命的。因此,有必要对IC-725A短波电台的本振信号源进行改进,以满足测量对精度的要求。

基于PLL的频率合成技术能够避免大量使用滤波器,十分有利于集成化和小型化,产生的信号长期稳定度和短期稳定度都很高,所以其应用也相当广泛[2~5]。PLL是一个能够跟踪输入信号的闭环自动控制系统[6],是一种利用反馈控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,PLL会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”。原子钟是基于物质内部微观运动的量子跃迁而实现的标准时间频率信号发生器,是当代第一个基于量子力学原理做成的计量器具[7]。铷时钟作为原子钟的一种,其稳定度高、体积小、重量轻、寿命长、价格便宜,应用场合十分广泛[8~9]。因此,本文采用PLL频率合成技术,利用铷时钟提供基准参考频率,对短波信道探测系统中的IC-725A短波电台的本振信号源进行高稳定度改进。

2 短波信道探测系统的工作原理

短波信道探测系统主要由数据发送与采集板、低噪声直流电源、计算机终端、短波电台和天线等组成。数据发送与采集板包括数字信号处理器模块、复杂可编程逻辑器件(CPLD)时序控制模块、模数/数模转换器模块、电台工作模式和频率控制模块、GPS接收机模块、GPS导航电文接收模块、高速通用串行总线模块、时钟模块[10]。短波信道探测系统收发硬件电路完全相同,通过不同的软件实现发和收的功能。系统启动前,待发送数据以WAVE格式存储在PC中,系统启动以后,用户可根据需要选择发送数据,数据经USB模块实时传输给DSP,缓存在DSP的片外存储区,经DAC后由短波电台经天线发射出去。每个频率点的散射波由天线接收后,从接收机串行输出到ADC进行采样,并实时传输给DSP,缓存在DSP的片外存储区,再由DSP经USB实时传输到PC端进行显示和存储。在Matlab中,通过编程实现短波信道冲击响应的估计、散射函数的计算等工作。

3 高稳定本振频率源的电路设计

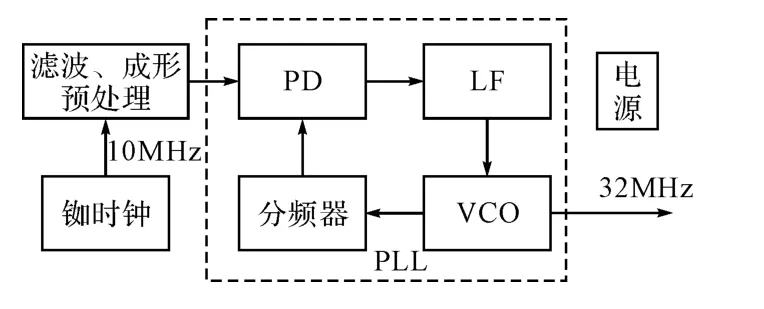

高稳定本振频率源电路为收发短波电台提供基准工作频率,使接收端采集得到的信号中由收发系统引入的频差接近零。高稳定本振频率源电路包括PLL环路、铷时钟、滤波提纯电路和电源模块,其原理框图如图1所示。PLL主要由PD、LF、压控振荡器(VCO)和反馈回路(分频器)组成[11~12]。PD对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。LF将输入信号中的高频成分滤除,保留直流部分送至VCO。VCO输出一个周期信号,其频率由输入电压所控制。反馈回路将VCO输出的信号送回至PD。本设计中PLL的PD由CPLD实现,VCO由32MHz压控晶振实现,LF由放大器、电阻、电容实现。铷时钟提供10MHz的基准频率给PD,为提高频率的纯度,铷时钟的输出信号在送往PD之前要先进行滤波提纯和成形预处理,滤波处理电路主要由变阻器和40MHz晶振组成。电源模块由电压转换电路和滤波电路组成,主要包括15V~5V转换电路(78M05)、5V~3.3V转换电路(AMS1117/3.3V)和滤波电路。其中,3.3V主要给CPLD提供工作电压,5V给PLL中的其它电路提供工作电压。

图1 PLL模块的原理框图

3.1 PD的设计

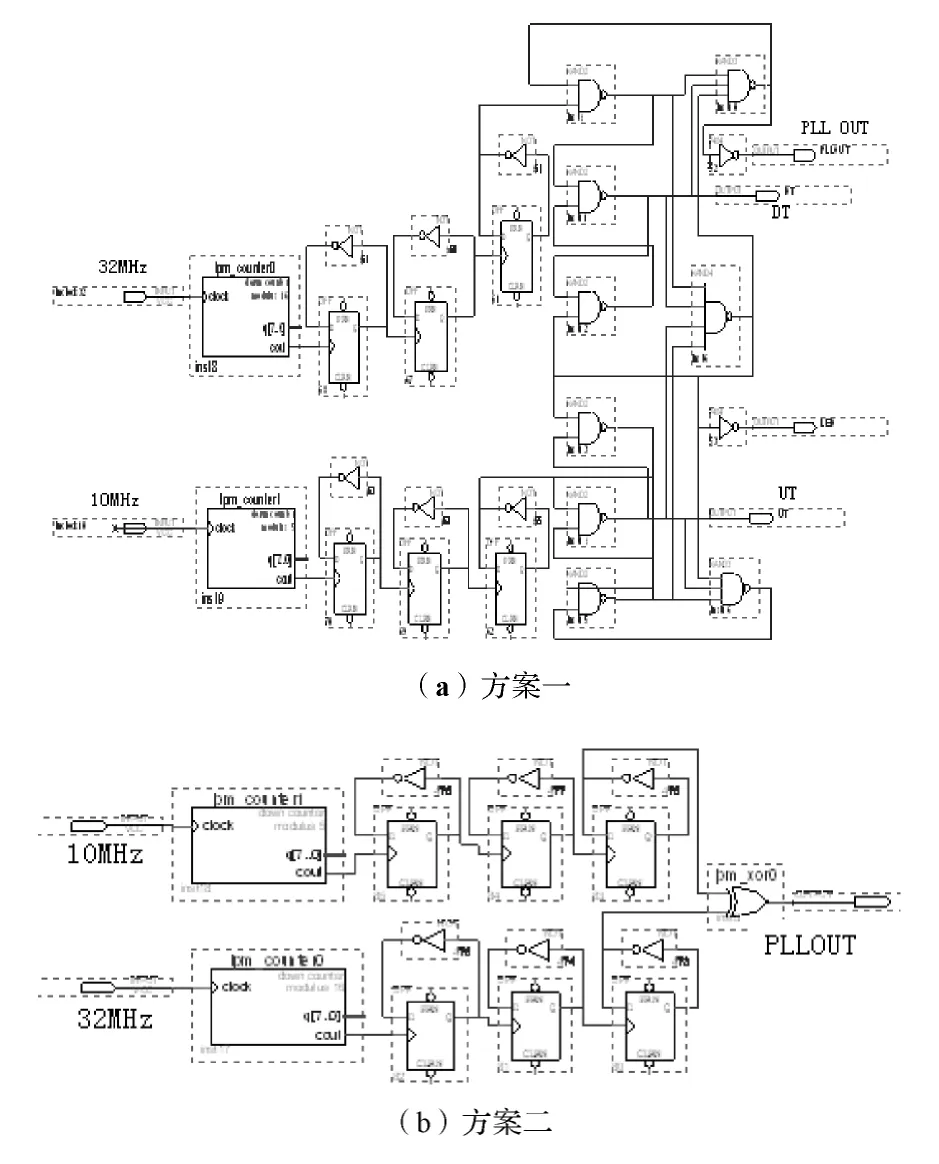

PD是PLL的重要部件之一,有多种逻辑电路实现形式[13],本文给出由CPLD实现的两种方案。方案一如图2(a)所示,32MHz和10MHz标识的端子分别为CPLD的外部引脚的inclock32和inclock10,PLLOUT、DT、UT分别对应CPLD的外部引脚的PLLOUT、DT和UT。PLLOUT为PLL信号的输出端;UT和DT表示差分输出,是PLL信号的另一种输出形式。本设计使用PLLOUT作为PLL的输出端。该方案除了有鉴相的功能以外还具有鉴频的功能,特别是当VCO的自频偏较大时,用方案一比较可行,原因在于此类鉴频鉴相器对VCO频率的拉动能力较强,有利于PLL快速锁定,但是缺点也很明显,即延时较大,如果环路滤波器通带较窄可能导致环路工作不稳定。方案二如图2(b)所示,逻辑简洁,优点是时延小、反应快,但是对VCO的拉动能力较弱,适用于VCO自偏较小,精度较高的应用场合,例如温补型晶体VCO。如果VCO选择高品质产品,采用方案二可以达到非常好的效果。在工程实现中,还可以使用测量环路瞬态控制曲线的方法来实现最优方案的选择,例如在VCO输入端接一个模拟电子开关到地,给电子开关送一个短时脉冲使环路瞬间失锁,记录LF的控制电压输出可以很有效地分析出各种不同方案的优劣,甚至LF参数的正确与否。

图2 PD电路设计方案

3.2 LF的设计

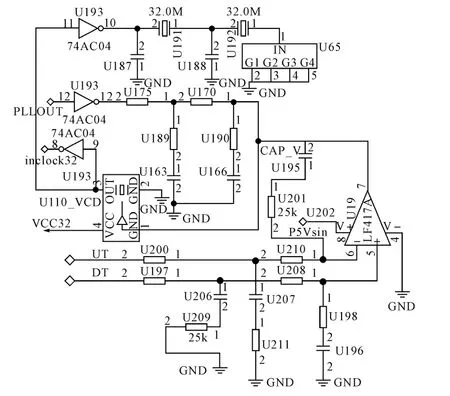

图3所示为针对3.1节中PD的两种实现方案的LF,实现时我们根据不同的VCO作相应的选择。由电阻U170、U189、U190和电容U163、U166组成LF的第一种方案,由放大器LF412A、电阻(U198、U201、U208、U209、U210、U211)、电容(U195、U196、U206、U207)组成LF的第二种方案。U110_VCO为VCO模块,从市面上购买。

图3中的PLLOUT输入端接图2(a)或图2(b)中PD的PLLOUT输出端,经74AC04反相后进行低通滤波,滤波后去控制VCO;图3中的UT和DT分别接图2(a)中PD的UT和DT输出端,经LF滤波后去控制VCO。VCO的输出信号一路经反相后送至PD输入端,一路经反相后送至由晶振(U191、U192)和电容(U187、U188)组成的窄带滤波器,滤除杂波后送往短波电台。

图3 VCO和LF电路设计

4 高稳定度频率信号的注入方法

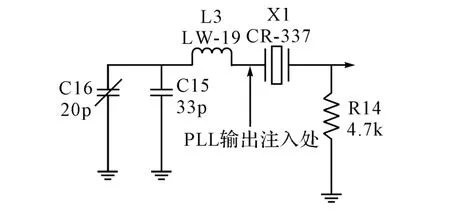

高稳定度的32MHz本振频率信号产生后,一个很重要的问题就是如何将之注入到电台中,而不影响电台的总体性能指标。我们的方法是保持电台原有的振荡电路不变,在电台32MHz晶体附近引入适当电平的高稳定度的32MHz信号(如图4所示),利用晶体振荡器的受迫振荡效应,让电台自身的振荡器工作在外接信号频率上,这样做的优点是对电台的改动极小,也不必考虑电台本振输出信号的电平问题,比本振替换法优越的多。这种方法的关键问题是,注入的信号电平必须恰当。我们的经验是将VCO的输出经74AC04整形,再经两级32MHz无源晶振滤波注入电台,幅度在0.1V左右,用74AC04整形目的是增加驱动能力。

图4 高稳定度频率信号的注入示意图

5 电路实现与测试结果

高稳定本振频率源电路的PCB板的设计工作采用VeriBest完成,主要分两步:第一步,在Design Capture中完成原理图设计;第二步,在VeriBest PCB中进行元器件的布局和布线。VeriBest软件具有良好的自动推挤式布线功能和引脚自动互换功能(对CPLD芯片),对CPLD的引脚配置十分便利。在制PCB板时,将本文设计的LF的两种实现方案同时制在板上,以第一种方案为主,第二种方案备用。研制成的高稳定本振频率源电路板如图5所示。

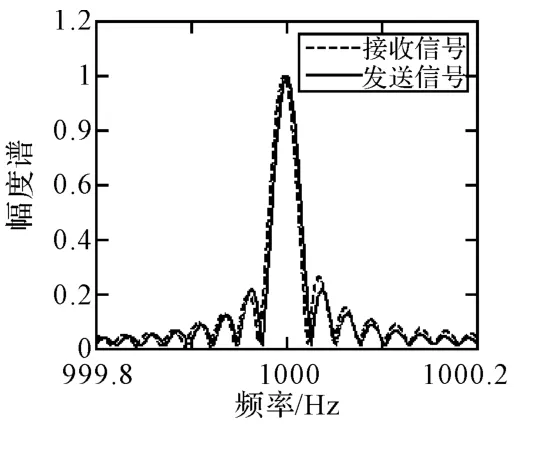

采用1000Hz单音信号对改造后的短波电台的本振信号频率在短波信道探测系统平台上进行测试,在PLL锁定后,发、收两部不同电台的频差如图6所示。从图6可以看出,改造后两部IC-725A短波电台的本振信号的频差几乎为零,计算机计算的频差结果在10-4Hz数量级,完全能够满足短波信道探测对频率精度的要求。

图5 高稳定本振频率源电路板

图6 改造后不同电台频差测试结果

6 结语

短波信道探测系统的良好性能是实现短波信道传播特性高精度探测的保障。本文针对短波信道探测系统中IC-725A短波电台原有本振频偏较大的问题,采用PLL频率合成技术,利用恒温铷时钟提供基准参考频率,对IC-725A短波电台的本振信号源进行高稳定度改进,并用电路实现。测试结果表明,改造后两部IC-725A短波电台的本振信号的频差在10-4Hz数量级,完全能够满足短波信道传播特性探测对电台频率精度的要求。

[1]刘月亮,蒋宇中,张四起.短波信道探测中多普勒频移的计算[J].计算机应用研究,2012,29(3):1070-1072.

[2]王新浪.频率合成技术发展与应用[J].现代导航,2012(2):119-122.

[3]SONG Chun-yun.Chaos Characteristics Analysis about Transient Signals of FH Radio with PLL Synthesizer[C]//International Conference on Multimedia and Signal Processing,China:IEEE Press,2011:17-20.

[4]David Murphy,Qun Jane Gu,WU Yi-Cheng,et al.A Low Phase Noise,Wideband and Compact CMOS PLL for Use in a Heterodyne 802.15.3cTransceiver[J].IEEE JOURNAL OF SOLID-STATE CIRCUITS,2011,46(7):1606-1616.

[5]Youngjong Ko,Kiwoo Park,Kyo-Beum Lee,et al.A New PLL System using Full Order Observer and PLL System Modeling in a Single Phase Grid-Connected Inverter[C]//8th International Conference on Power Electronics-ECCE Asia,Korea:IEEE Press,2011:803-808.

[6]季轩,毛陆虹,王子青,等.应用于SoC的全数字锁相环ASIC设计[J].电路与系统学报,2011,16(5):8-13.

[7]黄杰,丁鼎,李万林,等.电力系统铷原子频标单元的设计与实现[J].电力系统通信,2011,32(220):30-34.

[8]邓韬,林建辉,张兵.基于铷原子振荡器的DDS精密时钟源设计[J].中国测试,2012,38(2):89-92.

[9]李廷军,林雪原,董文洪,等.利用铷钟实现组合导航系统研究[J].通信学报,2006,27(8):144-147.

[10]刘月亮,蒋宇中,张伟.短波信道探测系统DSP端软件设计与实现[J].电子技术应用,2011,37(12):133-136.

[11]樊孝明,林基明.锁相环解调的Chirp-UWB接收机仿真研究[J].电子技术应用,2011,37(5):121-125.

[12]胡天琨,叶建芳.基于MCU的锁相环锁定时间测量系统设计[J].现代电子技术,2012,35(6):22-24.

[13]黄智伟.锁相环宇频率合成器电路设计[M].西安:西安电子科技大学出版社,2008.