应用于GPS导航基带芯片的SPI IP核的设计和验证

2013-09-14曹磊李晓江马成炎

曹磊 李晓江 马成炎

(1.中国科学院微电子研究所,北京 100029;2.杭州中科微电子有限公司,杭州 310053;3.嘉兴联星微电子有限公司,嘉兴 314000;)

0 引言

随着SOC的规模不断扩大,集成的IP模块不断增多,设计一款可复用的IP核对于减少设计复杂度、缩短SOC开发周期、提高流片成功率都是重要的一环。SPI(Serial Peripheral Interface)串行通信总线具有配置灵活,结构简单等优点,被广泛应用于各位处理器和嵌入式系统当中。因此,对于SPI IP核的设计已经成为业界的设计热点之一,但现有设计功能还不够完善。文献[1]设计了SPI Master模块,不具有SPI Slave功能;文献[2]设计了一款基于FPGA的SPI总线,但是不支持四线工作模式,并且对设计本身的结构和特性叙述不多;文献[3]的设计实现了多功能化的SPI IP核,但是不支持DMA功能,所设计的SPI Master也没作流水考虑,数据传输率受到限制。本文总结上述设计中存在的问题,提出了一种基于APB总线的高速可复用的SPI IP核实现方法,使所设计的SPI接口具有更高的实际可操作性,并且已经在流片回来的芯片上得到了验证。

1 SPI协议及时序概述

SPI是由Motorola公司首先在其MC68HCXX系列处理器上定义的一种高速的、全双工的、同步的通信总线,通常只占用四根芯片管脚,分别为MOSI:串行数据输出线,当SPI模块为主模块时,它输出数据;当SPI模块为从模块时,它接收数据;MISO:串行数据输入线,当SPI模块为主模块时,它接收数据;当SPI模块为从模块时,它输出数据;SCK:同步串行时钟,由SPI主模块产生;nCS:从机片选线,低电平有效,由主模块产生。协议规定了SPI的主、从两种工作模式,工作在主模式的SPI模块负责产生串行时钟SCK和对从模块的片选信号。

图1 SPI外设接口的四种数据传输时序

SPI模块为了和外设进行数据交换,根据外设的工作要求,其输出串行同步时钟SCK的极性CPOL和相位CPHA可以进行配置,因此SPI有四种传输时序,其共同特点是每位数据的发送/接收需要一个SCK周期,每次传输整数倍个8位数据。当CPOL=0时,串行时钟的空闲状态为低电平;当CPOL=1时,串行同步时钟的空闲状态位高电平。而时钟相位CPHA则决定了数据采样的数据沿,当CPHA=1时,在串行同步时钟的第二个跳变沿数据被采样;当CPHA=0时,在串行同步时钟的第一个跳变沿数据被采样。SPI模块的四种

接口时序如图1所示。

2 SPI IP核的设计

2.1 SPI IP核系统结构及主要功能

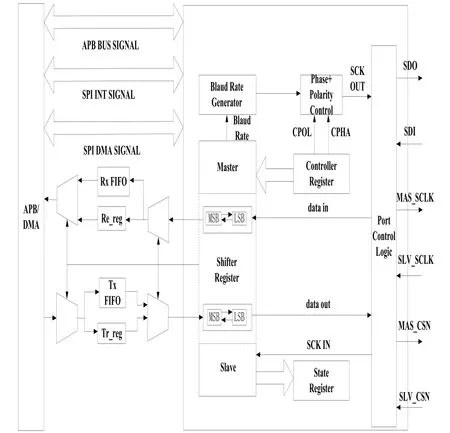

该IP核应用于国家导航基带项目,基于APB总线进行设计。CPU或者DMA模块可通过APB总线完成对该SPI模块的寄存器配置、数据读写及中断处理等操作。所设计的SPI电路主要包括:SPI控制寄存器SPCR、数据发送模块TRANSMITTER、数据接收模块RECEIVER、发送/接收同步FIFO、状态寄存器SPSR。其总体结构图如图2所示。

图2 SPI IP核系统结构

如图2所示,所设计的SPI IP核实现了传统SPI协议的四线结构。同时满足SPI的四种接口时序,通过控制寄存器的CPOL和CPHA位来控制。增加了两个8位深度、32位宽度的同步可选FIFO,用以提高传输速率。每次发送/接收的比特数可在8bits、16bits、32bits选择,并且首尾比特位的发送/接收顺序也可选。考虑到部分应用中可能需要三线结构的SPI核进行半双工工作,本设计可只使用SDI数据线作三线工作方式。

2.2 主要模块的设计

本次设计主要采用自顶向下的设计方法,首先完成设计说明文档,划分好各子模块和系统架构,再进行Verilog代码的编写,主要实现的功能和设计中部分问题的解决方法如下。

2.2.1 存储器模块

所设计的SPI核主要包括一个32位的控制寄存器,实现Master/Slave功能的切换、中断模式/DMA模式的切换等功能的控制;一个32位的状态寄存器,记录发送/接收中断、同步FIFO空满标志等状态;两个8X32的同步FIFO,可选择是否使用。

2.2.2 时钟分频模块

当SPI被用作Master时,将会根据控制寄存器SPI_DIV位所设置的分频数值来对APB总线时钟进行分频,用以产生所需要的同步串行时钟SCK。本设计可完成对APB总线时钟进行最高4096分频,默认分频值是二分频,所采用的分频公式为:fpclk= fSCK*2SPI_DIV+1。

2.2.3 SPI Master模块

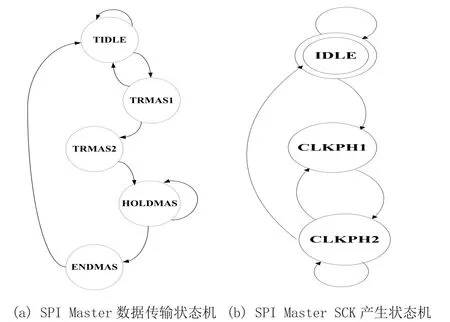

通过控制寄存器MSTR位的配置,可将SPI IP设定在Master工作模式。在此工作模式下,SPI会自主产生nCS片选信号和SCK时钟信号,同时完成SPI四种时钟时序的产生逻辑。相比较传统的SPI Master,本次设计不仅仅再局限于每次8比特的传输量,增加了16比特、32比特可选配置。并且,相比较于文献[4]每二次的传输都要间隔几个总线时钟用来取数据,会影响传输速率。对此,考虑到SCK一般都比APB总线时钟周期大,可以在每组数据传输到最后一个比特时,轮询发送FIFO,查看是否为空,持续半个SCK周期。若发送FIFO非空,则立即将下一组待发送数据提前准备好,结束轮询。这样可以实现传输的连贯性,减小本身设计造成的传输延迟,增加传输速率。所设计的SPI Master模块的状态机如图3所示。

图3 SPI Master模块有限状态机

SPI在发送数据时,所发送的数据要和模块产生的串行时钟SCK保持同步,这就要求了在每次SCK后半周期的跳变沿时,发送数据才能变成下一比特。这也使得两个状态机在逻辑上出现交叉控制,相互协同工作,同时保证在SCK一个时钟周期的第一个时钟沿采样接收数据,第二个时钟沿改变发送数据。

TIDLE:当每次传输结束或者进行复位后,状态机处于这一状态。在该状态下,若控制寄存器配置成Master模式并且出现传输请求,则跳转到TRMAS1状态。

TRMAS1:该状态只保持一个APB总线周期,用于向FIFO或者发送寄存器产生读指令,然后直接跳转到TRMAS2状态。

TRMAS2:该状态也只保持一个APB总线周期,用以将待发送的一组数据寄存到传输移位寄存器中,在HOLDMAS状态下作移位发送。

HOLDMAS:保持该状态,直到发送最后一个比特位并且没有待发送的数据,期间要不断轮询SCK产生状态机和FIFO空满标志位。

ENDMAS:保持一个APB总线时钟,用以产生传输结束中断或者DMA请求信号。

CLKPH1:根据所配置的时钟分频数值,对应于一个同步串行时钟SCK周期的前半周期。

CLKPH2:根据所配置的时钟分频数值,对应于一个同步串行时钟SCK周期的后半周期,在传输到最后一比特且没有下一组待发数据时,跳回到IDLE状态。

2.2.4 SPI Slave模块

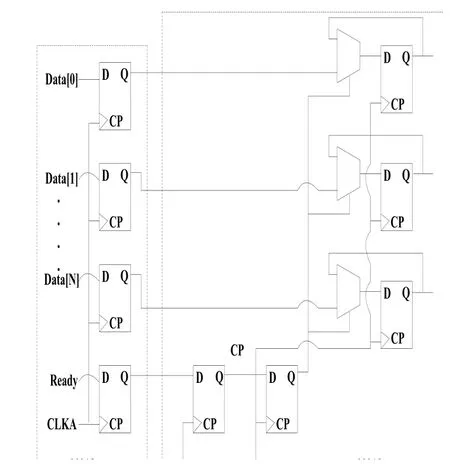

相比较于Master模式,当SPI作为Slave使用时,不需要自己产生同步串行时钟SCK,由外部输入SCK时钟。从空闲状态到传输状态的触发条件,也是来自于主设备的nCS片选信号。由此,可以看到Slave的传输受到Master的控制,当Master没有同步串行时钟输入时,Slave需要重新返回到空闲状态,并产生相应的状态标志位,其状态机主要参考Master模式设计。另外,因为SCK时钟是由Master产生输入到Slave,Slave本身还有来自APB的总线时钟,这样当在SCK时钟域下,完成接收数据的串行转并行和发送数据的并行转串行后,需要将保存好的接收数据传输到APB时钟域下,和从APB时钟域读取下一组待发数据,这样就需要在Slave内部作异步时钟处理操作,用以避免出现亚稳态现象。所采取的方法如图4所示。

图4 SPI Slave异步时钟处理设计

在SCK时钟域和APB时钟域之间,每次交换的都是多比特数据,不能采用传统的单比特同步方法。在本次设计中,使用的是类似于握手协议的处理方法[5],当一次传输完成,SCK时钟域内会产生单比特的标志信号送到APB时钟域下,经过两级时钟采样再作为控制信号,再将SCK时钟域下接收的数据转移到APB时钟域下,同时将APB时钟域下准备好的下组待发数据转移到SCK时钟域下。这样就可以满足异步信号的建立和保持时间冲突问题,避免亚稳态的产生。

3 仿真验证和综合结果

本设计,首先用Synopsys公司的VCS仿真软件,用Verilog HDL语言编写顶层的Testbench,并在该顶层内编写测试变量,进行功能仿真。然后,利用Synopsys公司的Design Compile软件进行综合,得到网表和延时文件再回到VCS软件中进行时序仿真。最后,再采用Altera公司EP3SL150F1152 FPGA芯片搭建的验证平台上,配合导航芯片ATGB03的其他模块,完成实测。在验证无误的情况下,已经成功流片并且流片回归测试运行正常,完全符合设计要求。

3.1 软件仿真验证

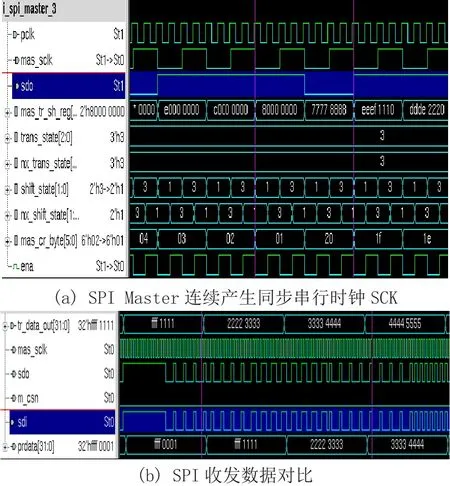

该部分的测试代码设计思路是,在建立的顶层Testbench模块内[6][7],实例化两个SPI模块SPI_M和SPI_S,分别设置成主模块和从模块,完成数据的收发测试。图5所示为VCS软件上局部时序仿真图。分别对应着SPI Master模式下,相邻发送数据可以产生连续的同步串行时钟SCK;以及从SPI Master中发送的数据进过SPI Slave模块接收存储后,能正确的通过APB总线进行读取。

图5 SPI IP核仿真结果

从图5(a)中可以看到,每次最高可以完成32比特的传输,并且当mas_cr_byte=0x01时,传输到最后一个比特,会自动开始下一组数据的发送,不需要再延迟几个APB时钟周期。内部设计的两个状态机继续保持在传输状态,大大提高了传输效率。在图5(b)中,SPI Master中的数据tr_data_out,在进过并转串处理,从sdi端传输到SPI Slave模块。SPI Slave模块对串行数据完成采样存储到接收FIFO后,从APB总线读取到的接收数据prdata和所发送的数据tr_data_out一致。

3.2 综合结果

使用Synopsys公司的Design Compile软件,对所写的SPI IP进行综合,所得到的report_area如 图6所 示。在SMIC 0.13工艺下,模块的总面积为37566.1,约合7513逻辑门。在将APB总线时钟设置在60MHz情况下,SPI IP运行在20MHz仍能完成数据的传输,达到了设计目的。

图6 SPI IP在SMIC 0.13工艺下的综合结果

4 结束语

本文设计一种应用于GPS导航芯片的可复用SPI IP核,它具有功能完善、速度快、可重用性高等特点,并通过了仿真验证、逻辑综合和FPGA平台测试,证明了其设计的可靠性和实用性,目前已经成功应用到已经量产的ATGB03 GPS导航芯片上,具有实际的商业价值。

[1] 李大江,崔建明. 一种基于FPGA的可配置SPI Master接口设计实现[J].电子技术应用. 2010.10(36):60-62.

[2] 汪永琳,丁一. 一种3线半双工SPI接口设计[J]. 半导体技术. 2010.5(35):482-484.

[3] 郭林,刘文杰,李跃辉. 基于FPGA的可复用SPI总线实现[J] .2012.4(155):34-37.

[4] Jianlong Zhang, Chunyu Wu, Wenjing Zhang The design and realization of a comprehensive SPI interface controller [J]. IEEE 2011.2:4529-4532.

[5] 谢修祥,王广生 异步多时钟系统的同步设计技术[J]. 电子工程师. 2005.5(31):36-38.

[6] Bergeron Janick. Writing testbenches: functional verification of HDL models [M] .[S.L]:Kluwer Academic Publishers.2003.

[7] 高谷刚,罗春. 可复用SPI模块IP核的设计与验证[J].单片机与嵌入式系统应用. 2004(11):5-8.