高速低功耗电压比较器机构设计研究

2013-07-03河南工业贸易职业学院郑州451191

(河南工业贸易职业学院,郑州 451191)

0 引言

随着时代的发展,系统芯片集成度越来越高,功能多种多样,可以满足不同需求,以此同时产生的问题也同益剧增,例如对能量的消耗问题同渐突出。供电电压虽然下降,但并没有遏制功耗的增长,研究显示功耗反而增加了两倍。由于芯片面积越来越小,功率密度越来越大,不仅对封装工艺提出了高要求,散热系统设计业成为了设计难点。因此越来越多的研究聚焦于减小芯片的功耗,低功耗最显而易见带来的既是较长的使用寿命[1]。

由于集成电路实现超深亚微米级,同时特征电压也随之降低,可以实现小于1V,伴随发展而来的是全新的问题,主要表现在噪声和短沟道等效应对功耗的增加,如何在性能和功耗之间设置最佳平衡点成为了亟待解决的问题。在深亚微米级别,很多因素和效应会造成高速低功耗数据转换器(以下简称ADC)设计难度大大增加。故为了解决这些问题,本文设计研发了一种全新的比较器,可以实现低功耗的需求。它的结构内核基础为latch锁存器,运用了开关运算放大器技术,不仅实现了高速低功耗,并且有很高的精度和传输速度。

1 国内外研究概况

片上系统(System On Chip,以下简称SOC)的数模混合集成需要定制在单硅片上。高指标高性能数模转换器是SOC的重要组成部分,在目前的信号与系统行业中,高指标高性能数模转换器已经成为了市场的宠儿。其中比较器是核心模块,起到了最为关键的作用,它的性能对整体的精度、速度、功耗有着及其重要的影响。但传统的比较器存在很多缺点,例如不能同时满足速度和功耗的高要求,必须进行优化改进。

纵观国内外,发展的趋势是实现低功耗、低延迟和高速度[2]。

2006年8月,Analog Device Incorporation推出ADCMP60x比较器系列产品。它可以实现2.5V~5.5V电源范围内的完全R-R性能,延迟时问介于Ins和35 ns之间,适用于高速低功耗应用,其突出特点为可以再低电压状态下工作,不会出现电压过低而造成的死区现象。

2006年10月,Austria micro systems推出AS1970-75比较器系列产品。它的突出特点是功耗低,可以达到8.5 u A,并提供1到4路输入可选,输入偏置电流仅为1pA。因为仅仅需要两节AA电池驱动,它在便携式设备领域取得了广泛的应用。

2007年8月,National Semiconductor Corporation推出了LMH7322比较器系列产品。它最令人惊艳的特点是达到了全行业最低功率,典型值仅为21mA,传播延迟极低,其数值为500ps。在相同的工况下,驱动电压每增加50mV,散射只增加2.5ps,及其适用于节能环保领域。

2 比较器性能和基本电路结构

2.1 比较器技术指标

我们通过比较器的正输入减去负输入的值来作为评价指标,值大于0时,输出高电平,小于0时输出低电平,为了方便表示,我们用缩写VOH和VOL分别进行表示,其传输曲线如图1所示。与此同时,我们用VP表示同相输入电压阈值,用Vn表示反相输入电压阈值。VOH代表输出电平最大值,VOL代表输出电平最小值。

图2所示为有限增益比较器的传输曲线。

VIH代表输出达到上限所需要的输入电压,VIL代表输出达到下限所需要的输入电压,其输入变化定义为比较器的精度。比较器特性包括静态特性和动态特性两大方面。如下所述为比较器各个参数定义。

差分输入电压范围:指两个信号输入端允许最大电压。

输入共模范围:指比较器能连续分辨的输入电压差值。

分辨率:指能够输出正确数字所需要的最小差分输入信号。

输入偏置电流:指无信号输入时的电流平均值。

响应时间:指比较器的时域特性即对于差分输入的响应时问。

传输延迟时间:又名比较速度,指输入信号与输出信号之间的时问差。

摆率:指输入电压达到上限时,即传输延迟时问不会再随输入电压增大而变化是的电压变化率。

输入偏移电流:指改变输出状态的输入电流绝对差值。

反冲噪声:又名回踢噪声,指输出信号由于电荷馈通对输入信号的反冲。

输出电压摆幅:指比较器的输出正负电之差。

输入失调电压:指由于MOS管几何尺寸误差产生的偏移电压。

2.2 比较器总体设计

比较器的分类规则有很多种,根据系统是否闭环可以分为开环和闭环式;根据功耗高低可以分为高功耗式和低功耗式;根据PCB板原理电路可以分成开环式和再生式;根据输出结构形式可以分为一端输出结构式和两端输出结构式[3]。

2.2.1 离散时间比较器

离散时间比较器主要有两种类型,分别为开关电容式和可再生式。

Latch比较器的另一个名字是可再生式比较器,它的位置通常在反馈的最后一级,而且往往设置为正反馈,以便可以通过前置放大器后端启动来提高整体性能。

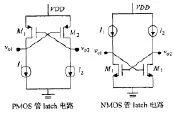

Latch的一般结构如图3所示。

图3 Latch结构示意图

Latch的正反馈原理非常简单,总结来说就是通过单位增益来实现正反馈。它的工作模式有两种:1)终止发出正反馈信号,同时输入信号传递到输入端;2)正常发出正反馈信号,同时输入信号传递到输入端,根据输入值来实现高低电平的不同。最常见的辅助器件为NMOS管,等效电路分析模型如图4所示。

图4 NMOS latch的小信号电路模型

2.2.2 高速比较器

高速比较器的目的是最大限度降低其传输延迟时间,这是可以把比较器分为数个级联电路,如图5所示,我们假设先决条件为每一级增益为A0,同时用l/t来代表单极点的值,在这种逻辑下,输入变化值高于Vin,就会激发电路,使得每级电路都可以放大输入信号。从图中可以看出,放大器会受到前几级信号的摆率限制。因此,对于前几级电路,带宽非常重要,对于后几级电路,高摆率非常重要。故在整个链路里,前几级和后几级电路设计是不相同的[4]。

图5 级联比较器概念描述

3 高速低功耗比较器机构设计

本文提出的设计指标如表1所示。

表1 设计指标

3.1 比较器结构的选择

为了实现最优性能,本文采用了如下方案即在比较器前置放大器中应用开关运算放大器技术。这样可以实现时钟信号控制前置运算放大器输出,需要连接在前置放大器和锁存器之间的开关,总体速度就不会再被高阻信号影响,降低了比较器输入端的回踢噪声[5]。

3.2 比较器建模

比较器建模的设计关键是合理设计有限增益,输入失调电压,传输延迟时间等参数对应的元器件。本文应用了可以提高增益的含有预放大级的比较器,并采用了最小沟道长度来提高反相器速度,进而提高比较器速度[6]。

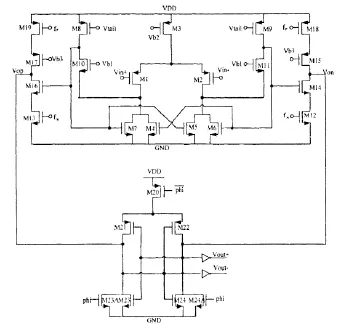

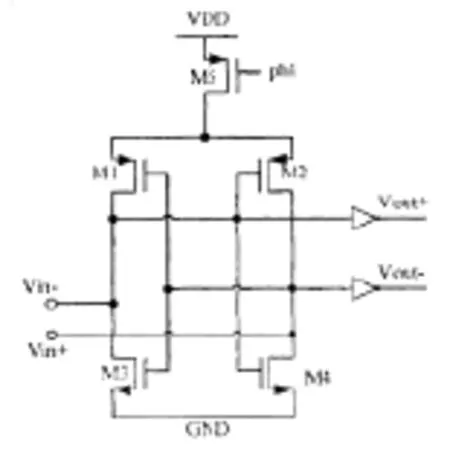

3.3 比较器结构设计

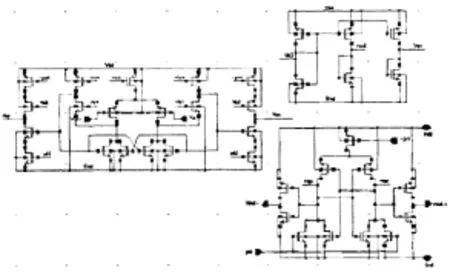

本文提出的基于开关运算放大器技术的新型比较器结构是建立在低电压算放大器的动态锁存器基础之上的。电路原理图如图6和图7所示。其中图6所示开关开启与闭合应用了双路非交叉时钟控制方法,这种双路非交叉原理示意如图8所示,主要起作用的零件为前置的晶体管M23A和M24A,由于它们可以实现输出置位,所以被用在放大阶段[7]。图7中动态锁存功能的实现是双路非交叉时钟控制方法的关键,主要依靠NMOS管和PMOS管CROSS功能,互补的同时作用于放置在后部的反向器,最终达到所需结果,并且缩短响应时间,极大的提高效率。

图6 开关运放比较器

图7 动态锁存器

图8 双向非交叠时钟原理图

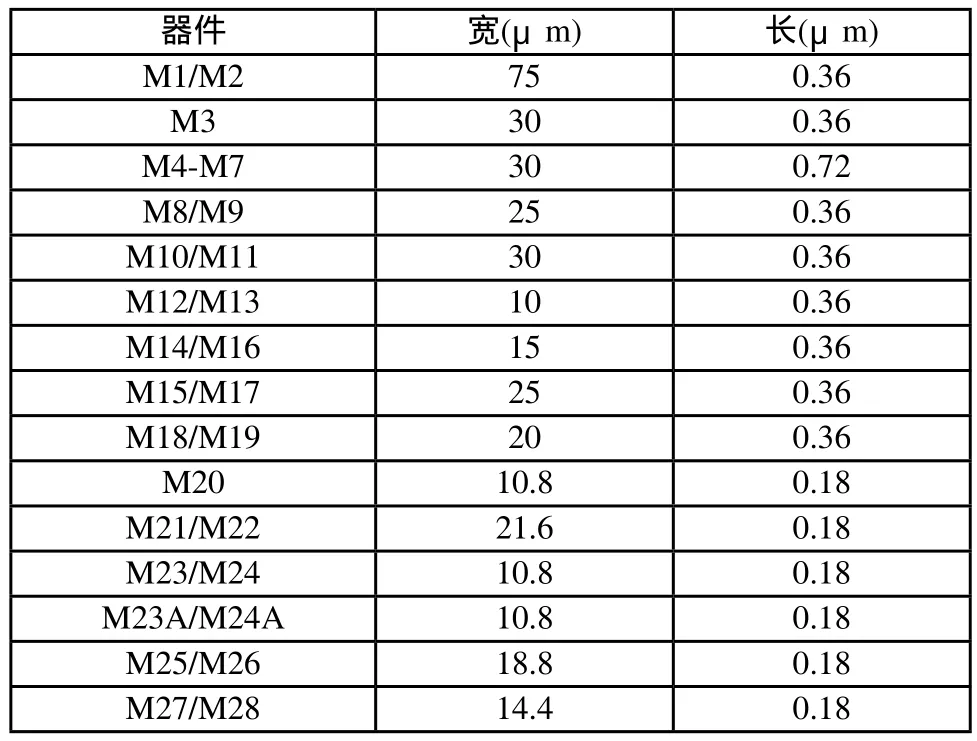

3.4 电路参数的确定

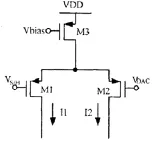

表2所示为开关运放比较器的电路设计参数。其中晶体管Ml/M2的长度没为最小值两倍是为了降低沟道长度,交叉耦合负载M4-M7的长度设为最小值4倍是为了实现最快再生速度。本文采用如图9所示的偏置电路结构以简化比较器电路结构设计。

表2 开关运放比较器的电路参数

图9 比较器的偏置电路

3.5 输入电容分析

如图10所示,为了D/A转换电路的性能和保持采样电路不受输入电容的影响,所以要对比较器的输入电容进行分析。为解决以上问题,本文采用了增加单极点运算放大器的方法,这样既实现了D/A转换,又稳定了保持采样电路,实现了缓冲功能,是的性能不受波动影响。它可以实现低输入电容,高输入电阻,以便使得比较器的响应时间和速度达到技术指标。

图10 前置放大器的输入级:PMOS差分对

4 仿真分析

在经过一系列的仿真分析之后,试验结果表明该高速低功耗电压比较器可以实现逐次逼近数模转换功能,性能效率高,稳定性好。如图11所示为整个比较器的电路结构,如图12所示为比较器的测试电路,其中,我们可以看出,整个比较器一共有前置放大器,Latch锁存器和偏置电路三大部分。

图11 整个比较器的电路结构

5 结论

应用本文的研究成果,基于INTEL 210nm的DSP CAPP工艺技术,可以实现1.8V直流电源供电条件下,12比特频率下,1 MS/s速率下的逐次逼近式高速低功耗比较器应用。通过原理图分析研究设计,经过仿真分析等步骤证明该比较器的设计是符合设计指标和要求的,并且达到了高速低功耗标准。

在结构设计上,通过采用latch结构动态比较器降低功耗,采用由开关控制前置放大级电路提高比响应速度,实现了速度和功耗之间的完美动念特性平衡。仿真分析阶段,通过搭建Confidence集成仿真环境,采用业内成熟的SPECTRE软件,应用SPSS和MATLAB工具软件进行辅助计算,试验结果一致表明电路设计实现了预期目标,前后仿真结果吻合,并且其优势明显:功耗低(0.9mw),采样频率低(25MHz),面积小(0.0018 mm2)。

图12 比较器的测试电路

在未来的工作中,可以进一步着眼于功耗和速率的优化,这其中还有很大的潜力可以挖掘,所以在未来的研究里还需要更加深入的开展相关工作。

[1] 邹强.VLSI设计方法实施[M].北京:科学出版社,2006.

[2] L.James,Blue and L,Quake. Low-power deadline for wiff and web unit. IEEE Jarnal of Manufacturing Circuits.2007,30(01):1410-1430.

[3] Jerry MJ. Stability analysis of a compliant modulator.IEEE Transaction on Electro circuit 12.1998.21: 231-240.

[4] 曲静婷,阳春鸾.高性能比较器失调补偿设计.南开大学.2005:l0-21.

[5] 熊永力.A/D转换器设计技巧.浙江大学,2008年P5-10.

[6] Sony E. Mary Caslon, Robot. CMOS analyses and Design.HARVARD UNIVERSITY ASION. OCT.1995.359-366.

[7] 葛明辉.高精密结构模数转换器设计.北京科技大学.2001:21-27.