双抽头CCD 图像整合优化设计

2012-10-30李洪法薛旭成郭永飞朱宏殷

李洪法 ,薛旭成,郭永飞,朱宏殷,2

(1.中国科学院 长春光学精密机械与物理研究所,吉林 长春130033;2.中国科学院 研究生院,北京100039)

1 引 言

随着电子耦合器件( Charge Coupled Device,CCD) 在光电成像领域应用范围的扩大,应用系统对CCD 的功能和性能要求越来越高,CCD 逐渐向大尺寸、小像元、高速度的方向发展。为了适应上述发展要求,许多CCD 在输出数据时采用了多抽头的结构形式[1-2]。这种结构形式的CCD 输出的图像呈多段式,如果直接使用,则最终的图像将呈条段式,这与实际使用不相符合。另一方面,通常这种结构CCD 的多个抽头间的数据输出方向相反。因此,实际应用这种CCD 时,需要对其输出的图像数据进行重新整合。本文提出了一种利用XILINX VIRTEX 系列现场可编程门阵列( FPGA)的内部Block RAM 实现多抽头CCD 图像数据整合的方法。

2 基本原理

某系统使用的线阵CCD 共有4 096 个像元,采用双抽头输出的工作模式,其图像输出原理示意图如图1 所示。

图1 两抽头CCD 的图像输出示意图Fig.1 Output sketch of double-tap CCD

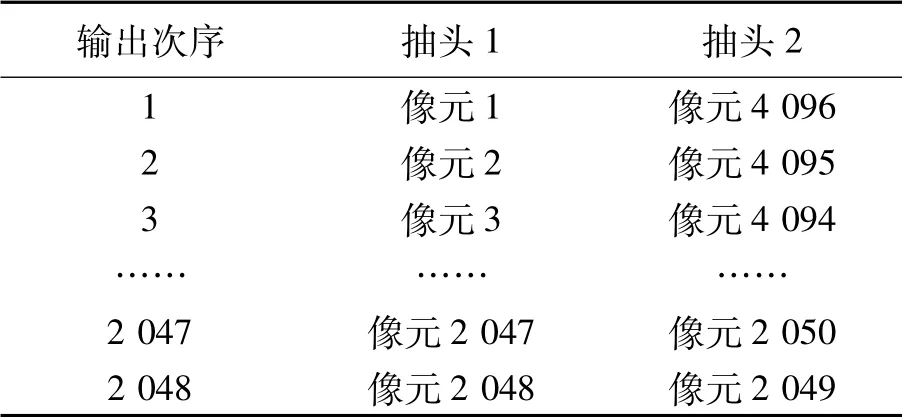

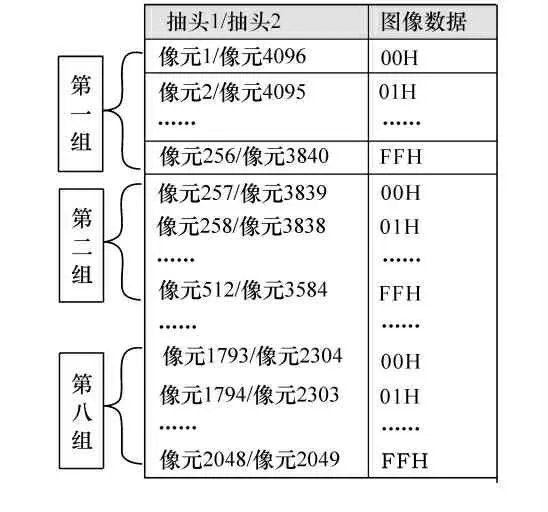

表1 CCD 各像元的输出次序Tab.1 Pixel sequences of CCD output

当CCD 完成对景物积分后,该行的图像数据从位于CCD 两侧的抽头1 和抽头2 同时输出。每个抽头输出2 048 个像元的数据。但是抽头1 输出的图像是正序,而抽头2 输出的图像是逆序,即抽头1 依次输出像元1 ~像元2 048,抽头2 依次输出像元4 096 ~像元2 049[3]。两个抽头输出的图像像元顺序如表1所示。

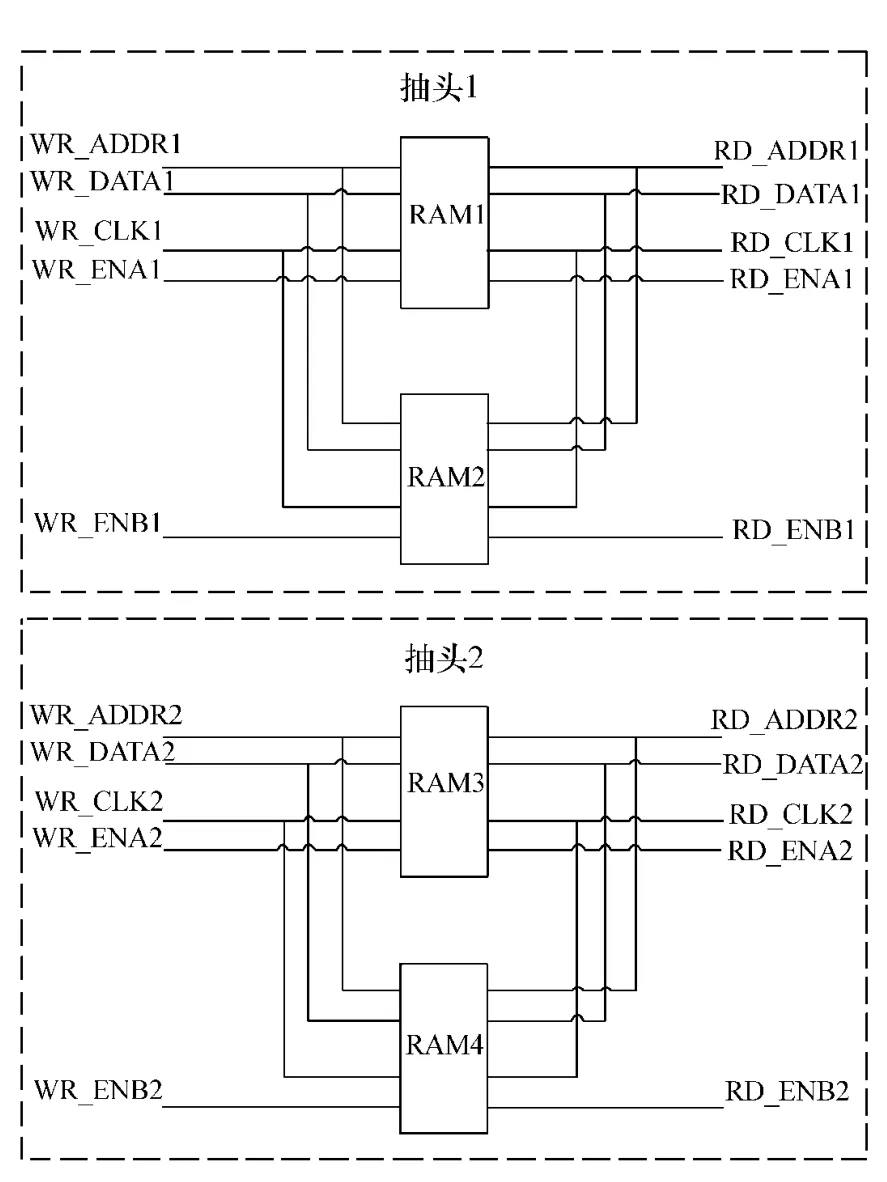

由于该CCD 是多抽头输出,其顺序和正常景物的顺序不一致,因此需要对其进行二次整合后再使用[4]。整合的要求是按CCD 的实际像元位置将两个抽头的数据合并为一路输出,即把两个抽头的图像数据合并为一路按像元1 ~像元4 096顺序输出图像[5]。通常利用乒乓原理对两个抽头的数据进行缓存处理[6],其实现结构如图2 所示。

图2 传统的乒乓操作整合结构Fig.2 Conformal structure of traditional Ping-Pang

在图2 中,RAM1 和RAM3 分别用于缓存抽头1 和抽头2 的第1 行图像数据,RAM2 和RAM4分别用于缓存抽头1 和抽头2 的第2 行图像数据。如果输入的图像数据以8 bit 进行量化,则对于第2 小节中的CCD而言,RAM1 ~RAM4 都是容量为2 Kbit 的双口RAM,因此在这种工作结构下,完成图像数据的整合共需要8 Kbit 的双口RAM。

图2 中RAM 使用的工作原理如下:

(1) 在第N个行周期,将CCD 的第N行数据分别缓存进RAM1 和RAM3 中;

(2) 在第N+1 个行周期,在将CCD 的第N+1 行数据分别缓存进RAM2 和RAM4 中的同时,将之前缓存在RAM1 和RAM3 中的第N行图像数据进行整合输出至输出端口;

(3) 在第N+2 个行周期,在将CCD 的第N+2 行数据分别缓存进RAM1 和RAM3 中的同时,将缓存在RAM2 和RAM4 中的第N+1 行图像数据进行整合输出至输出端口;

(4) 在第4 个行周期以及后面的行周期中,重复上述步骤2 和步骤3 即可,直至停止数据采集。

采用上述方法可以实现对多抽头CCD 图像数据的整合,但是它的缺点是占用的RAM 资源量较大,输出有延滞,这在一些对资源要求比较高的系统中是不合适的[7]。根据CCD 两个抽头输出的图像数据的特点,本文对上述RAM 使用结构进行了改进。

图3 改进乒乓后的数据整合结构Fig.3 Conformal structure of improved Ping-Pang

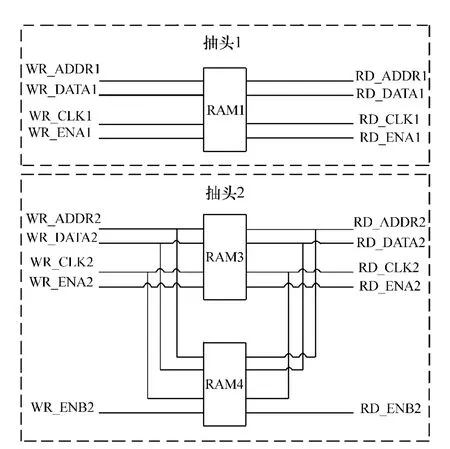

由于抽头1 的图像数据与抽头2 同时输入,但在输出时抽头1 的图像数据比抽头2 的数据先输出,且抽头1 的数据在输入时和输出时没有改变[8],因此可以通过调整工作时序使得采用一片RAM 即可完成抽头1 的数据缓存。改进后的RAM 结构如图3 所示。

图3 中,抽头1 占用了一片容量为2 Kbit 的RAM,抽头2 用了两片容量为2 Kbit 的RAM,合计共占用6 Kbit 大小的RAM,和改进前相比节省了25%的存储空间[8]。

抽头1 数据的像元顺序在输入时和输出时一致,而且输出时先于抽头2 输出。因此,如果写入速率为CLK1X,读出速率为CLK2X,则只要在写入端完成一半的图像数据写入后,即可在完成写入数据的同时也完成对抽头1 数据的读取。为了保证FPGA 内部对RAM 操作时有可靠的建立时间和保持时间,对抽头1 数据完成了1025 个像元数据存储后再进行读取,详细过程如下:

(1) 在第N个行周期中,在RAM1 和RAM3的写入端,将CCD 数据以CLK1X 的速率分别缓存进RAM1 和RAM3 中; 在RAM1 输出端,在写完第1 026 个像元的数据后,以CLK2X 的速率将RAM1 中存储的抽头1 数据按顺序进行输出。将RAM1 中的数据读完后,将RAM3 的数据按规定的顺序进行输出。

(2) 在第N+ 1 个行周期中,在RAM1 和RAM4 的写入端,将CCD 数据以CLK1X 的速率分别缓存进RAM1 和RAM4 中; 在RAM1 输出端,在写完第1 026 个像元的数据后,以CLK2X的速率将RAM1 中存储的抽头1 数据按顺序进行输出。将RAM1 中的数据读完后,将RAM4 的数据按规定的顺序进行输出。

(3) 在第N+2 个行周期以及后面的行周期中,重复上述步骤1 和步骤2 即可。

3 仿真实验与结果分析

为了验证改进后的RAM 结构,采用XILINX的VIRTEX 系列FPGA 搭建了一个软件平台[9]对其进行仿真验证,如图4 所示。其中自校图形产生模块用来模拟从CCD 输出的两个抽头的数据,图像整合模块采用第2 节中介绍的RAM 结构实现将输入的数据按照指定的顺序重新整合[10],并将整合后的数据输出,由此形成该仿真软件的顶层原理图,如图5 所示。

图4 仿真软件方框图Fig.4 Block diagram of simulation software

在图5 中,自校图形产生模块zjtx 模拟CCD的抽头1 和抽头2 的输出图像,两个抽头的图像格式相同。由于系统中所使用的CCD 共有4 096个像元从两个抽头分别输出,因此每个抽头上有2 048个像元数据输出。自校图形是数据由00H逐渐增加至FFH 的数据段 ,根据上面的分析可知,每个抽头上这样的数据段共有8 组,如表2所示。

表2 自校图形模块输出格式Tab.2 Output format of self-check image module

图5 图像整合的顶层原理图Fig.5 Top scheme of image conformity

图像整合模块由RAM1,RAM34,hecheng 和xzout 等子模块构成。由于图3 中的WR_ENA2和WR_ENB2 互相对立,即当WR_ENA2 有效时,WR_ENB2 无效;当WR_ENA2 无效时,WR_ENB2有效。因此可以将这两个信号作为RAM 的写地址线使用,即可以将图3 中的RAM3 和RAM4 两片RAM 更新为图5 中的一片RAM—RAM34。这样,自校图形模块产生的两抽头数据在hecheng子模块的控制下,在RAM1 和RAM34 两片RAM之间可进行乒乓存储和读取。最后,通过xzout 子模块输出整合后形成的有序图像流。

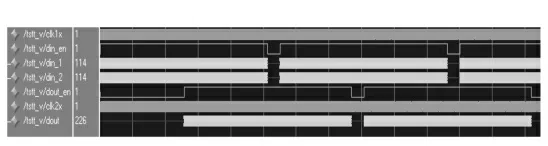

图6 ModelSim 仿真结果Fig.6 Simulation result of ModelSim

图7 整合后行头数据( 局部)Fig.7 Conformed data at the beginning of line

图8 整合后抽头接缝处数据( 局部)Fig.8 Conformed data at the join of two taps

在上述输入图像数据格式下,利用ModelSim软件对上述模块进行了仿真。仿真结果如图6 所示。将其进行局部放大后,如图7 ~图9 所示,分别是整合后行首、抽头接缝以及行尾处的局部放大图。从图中可以看出,输出图像实现了对输入的两抽头数据按照CCD 像元1 ~4 096 的顺序重新整合,完成了工作目标。

图9 整合后行尾数据( 局部)Fig.9 Conformed data at the end of line

4 结 论

针对硬件资源占用率要求较高的CCD 图像数据采集系统,提出了一种基于XILINX VIRTEX系列FPGA 的内部BLOCK RAM,利用改进的RAM 结构实现了对双抽头CCD 输出图像数据的整合。与传统的乒乓操作方法相比,该方法可以节省25%的RAM 资源占用,大大降低了软件对系统硬件资源的要求,有利于实现系统的集成化、小型化和轻量化,也有利于降低系统的成本。该方法在实际的工程中得到了成功应用,从运行结果看,该方法是有效和准确的。

[1] 胡琳.CCD 图像传感器的现状及未来发展[J].电子科技,2010,23(6) :82-85.HU L. Current situations and future developments of CCD image sensors[J].Electronic Sci.&Technology,2010,23(6) :82-85.( in Chinese)

[2] HIDESHI A. Device technologies for high quality and smaller pixel in CCD and CMOS image sensors[C]//Proceeding of the Technical Digest International Electron Devices Meeting,2004:989-912.

[3] THEUWISSEN A J P. The hole role in solid-state imagers[J].IEEE T. Electron Devices,2006,53(12) :2972-2980.

[4] 王明富,杨世洪,吴钦章.大面阵CCD 图像实时显示系统的设计[J].光学 精密工程,2010,18(9) :2053-2059.WANG M F,YANG SH H,WU Q ZH. Design of large-array CCD real-time display system[J].Opt. Precision Eng.,2009,17(8) :2053-2059.( in Chinese)

[5] 徐欣,于红旗,易凡,等.基于FPGA 的嵌入式系统设计[M].北京:机械工业出版社,2004.XU X,YU H Q,YI F,et al. Embedded System Design Based on FPGA[M]. Beijing:China Machine Press,2004.( in Chinese)

[6] 周贤波,冯龙龄.基于DSP 和FPGA 图像采集技术的研究[J].光学技术,2006,32( 增) :141-143.ZHOU X B,FENG L L. A study on image acquisition technology based on DSP and FPGA[J].Opt. Technique,2006,32( S) :141-143.( in Chinese)

[7] 梁冰,易茂祥,颜天信.高性能线性CCD 开发平台的研制[J]. 合肥工业大学学报( 自然科学版) ,2010,33( 10) :1579-1581.LIANG B,YI M X,YAN T X. Design of high-performance linear CCD development platform[J].J. Hefei University Technol.,2010,33(10) :1579-1581.( in Chinese)

[8] DUAN J H,DENG Y L,LANG K. Development of image processing system based on DSP and FPGA[C],ICEMI'07. 8th Int Conf on Electronic Measurement and Instruments,Aug 16-18 2007,Xi'an,China,2007:2791-2794.

[9] ZHANG F. A high-speed method of CCD image data storage system[J].IEEE Advanced Computer Control,2010,2(6) :45-48.

[10] ZHAO Y F,WANG Q Y. Digital image storage system based on 1M60 digital CCD[J].Electronics&Control,2007,14(5) :179-183.

[11] 王文华,何斌,任建岳.线阵CCD 成像系统自校图形设计[J].光学 精密工程,2009,17(8) :2011-2016.WANG W H,HE B,REN J Y. Design of self-check figures in linear CCD imaging system[J].Opt. Precision Eng.,2009,17(8) :2011-2016.( in Chinese)