基于FPGA的MSK调制器设计与实现

2012-09-27谢丽君谭立志

谢丽君,谭立志

(1.长沙职业技术学院 湖南 长沙 410003;2.株洲职业技术学院 湖南 株洲 412001)

基于FPGA的MSK调制器设计与实现

谢丽君1,谭立志2

(1.长沙职业技术学院 湖南 长沙 410003;2.株洲职业技术学院 湖南 株洲 412001)

介绍了MSK信号的优点,并分析了其实现原理,提出一种MSK高性能数字调制器的FPGA实现方案;采用自顶向下的设计思想,将系统分成串/并变换器、差分编码器、数控振荡器、移相器、乘法电路和加法电路等6大模块,重点论述了串/并变换、差分编码、数控振荡器的实现,用原理图输入、VHDL语言设计相结合的多种设计方法,分别实现了各模块的具体设计,并给出了其在QuartusII环境下的仿真结果。结果表明,基于FPGA的MSK调制器,设计简单,便于修改和调试,性能稳定。

MSK;FPGA;差分编码器;数控振荡器

在QPSK调制技术中,假定每个符号的包络都是矩形,已调信号的包络是恒定的,此时无论基带信号还是已调信号其频谱都是无限的。但是实际的信道总是有一定的带宽的,因此在发送QPSK信号时通常要通过带通滤波器进行限带。限带后的信号已经不能再保持包络恒定,相邻符号间发生相移时,限带后包络会明显变小,甚至出现包络为0的现象。这种现象在非线性信道中是不希望出现的,虽然经过非线性放大器能够减弱包络起伏,但是这样却使信号的频谱扩展,其旁瓣会干扰邻近频道的信号,造成限带时的带通滤波器失去作用。

正是为了解决这个问题,我们引入了在非线性限带信道中使用的恒包络调制方法———最小移频键控(MSK)调制技术[1]。

1 实现原理

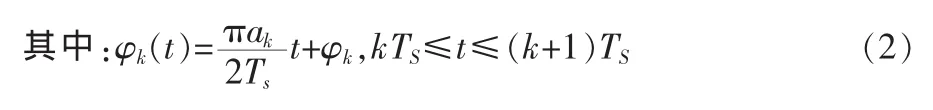

MSK就是一种能产生恒定包络、连续相位信号的调制方式[2]。它是二进制连续相位移频键控(CPFSK)的一种特殊情况,即调制指数 (移频系数)h=0.5,相位在码元转换时刻是连续的。 MSK 信号可表示为 :

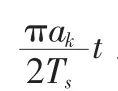

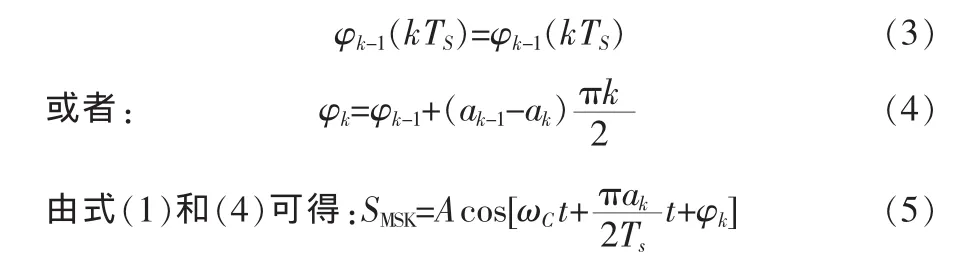

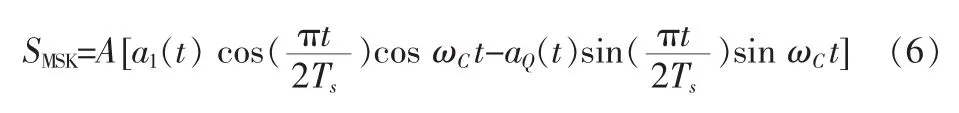

由式(5)和MSK相位网格图可看出,φk为截矩,其值为π的整数倍,利用三角等式并注意到sinφk=0,有:

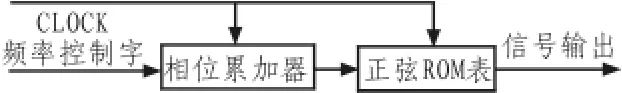

根据以上分析,可以得出MSK调制器的框图如图1所示。

2 主要模块的FPGA实现

2.1 串/并转换的实现

图1 MSK调制器方框图Fig.1 The MSK principle

顺序输入的二进制信息经过串/并变换器,变换成速率减半的双比特序列,可采用两个D触发器来实现,其原理如图2所示。其中DFFinst和DFFinst3构成一个两位移位寄存器,将串行输入信号变成并行输出信号;DFFinst4和NOTinst8构成二分频器,实现速率减半;DFFinst1和DFFinst2为锁存器,使信号同步输出。图 3为串/并变换器 S_P的仿真结果,其中AB为变换后的双比特码元。由图可以看出,当输入DataAB为01010101时,在延时约80 ns后,输出DataA为0000,DataB 为 1111[3]。

2.2 差分编码器的实现

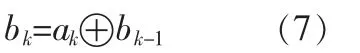

差分编码器的功能[4]就是实现绝对码变换为相对码,在相码中,1、0分别用相邻码元电平是否发生跳变来表示。若用相邻电平发生跳变来表示码元1,则称为传号差分码,记做NRZ码。绝对码-相对码之间的关系为:

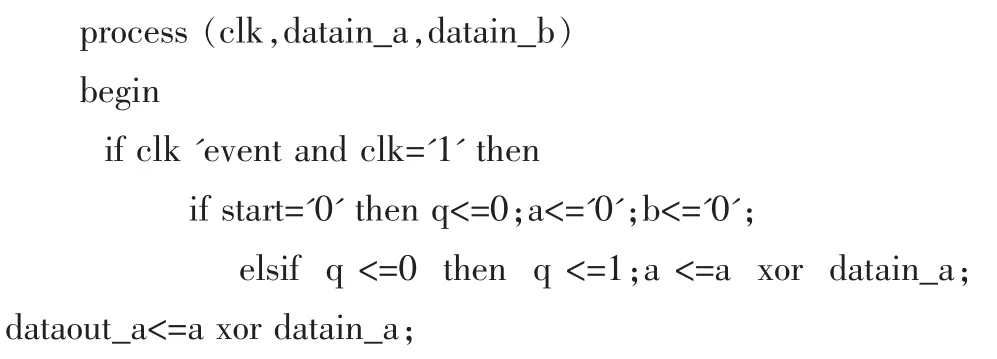

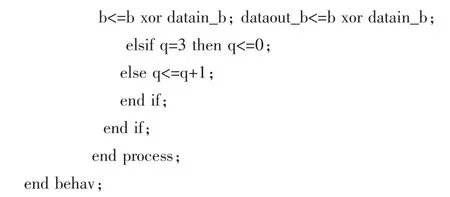

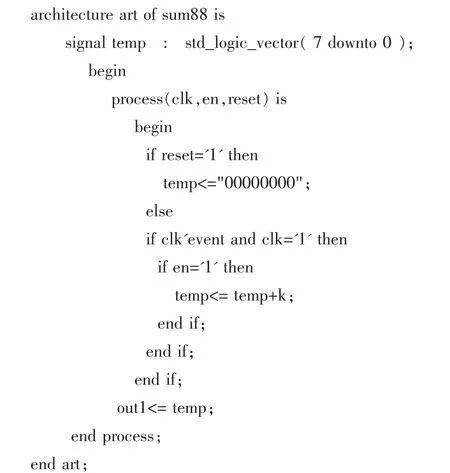

采用VHDL设计的主体代码[5]如下:

图2 串/并转换原理图Fig.2 The series-parallel conversion principle

图3 串/并转换仿真波形图Fig.3 The simulation diagram of series-parallel conversion

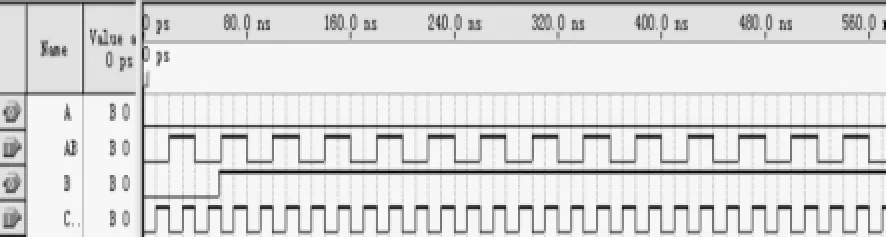

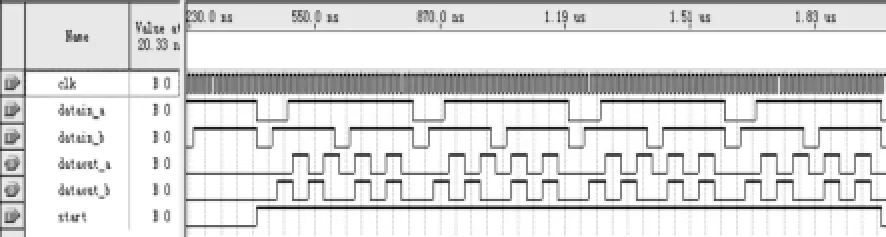

经编译后生成元件,其波形仿真图如图 4所示,由图可以得到:当start为低电平时,两路输出信号都为0;当start信号为高电平时,对输入信号 (datain_a)有:datain_a=011111111001,此时dataout_a=010101010001,对输入信号(datain_b) 有 :datain_b=011110111101, 此 时 Dataout_b=010100101001,由此可以得出,元件QDSP_PL实现了由绝对码到相对码的变换。

图4 绝对码到相对码变换仿真图Fig.4 The simulation diagram of absolute code change to relative

2.3 NCO的实现

2.3.1 NCO的实现原理

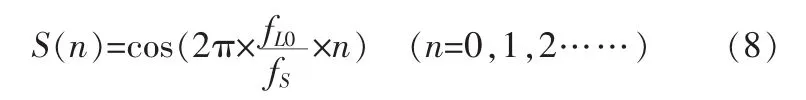

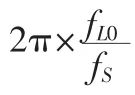

数控振荡器在数字中频中相对来说是比较复杂的,也是决定数字中频性能的主要因素之一,NCO的目标是产生一个理想的正弦波或余弦波,如式(8)。

图5 NCO原理框图Fig.5 NCO principle diagram

2.3.2 相位累加器的FPGA实现

相位累加器由N位加法器与N位寄存器级联构成。每来一个时钟fc,加法器将频率控制字K与寄存器输出的累加相位数据相加,再把相加后的结果送至寄存器的数据输入端。相位累加器输出的数据就是合成信号的相位,当相位累加器累加到最大值时会产生一次溢出,完成一个周期的动作。溢出频率就是NCO输出的信号频率。可用VHDL语言实现相位累加器的设计,其主要代码如下:

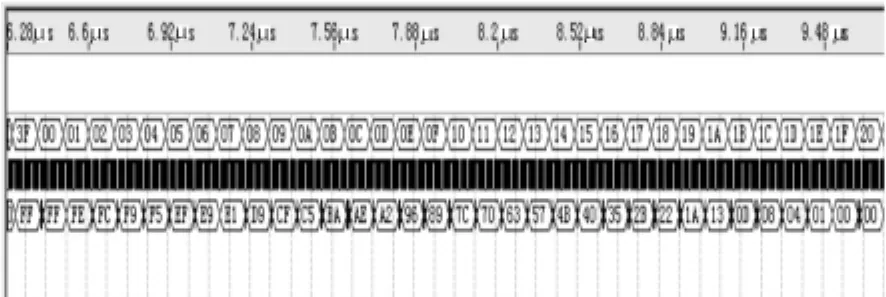

8位相位累加器的仿真波形如图6所示。由波形图可以看出,当k=08时,在每一个有效脉冲的作用下,输出的数值比前一个输出的数值大8;当k=09时,输出的数值比前一个输出的数值大9;结果证明,该程序实现了相位的累加。

2.3.3 正弦ROM表的FPGA实现

用相位累加器输出的数据作为波形存储器的取样地址,完成相位序列(相位码)向幅度序列(幅度码)的转换。这里用ROM构造一个查找表。N位的寻址ROM相当于把一个周期的正弦 波形信号离散成具有2N个幅值的序列,若波形ROM有D位数据位,则2N个幅值以D位二进制数值固化在FPGA的ROM中,按照给定地址的不同可以输出相应相位的正弦信号的幅度编码。

图6 8位相位累加器的仿真波形如图Fig.6 The diagram showing the stimulated wave of 8 bit Phase-accumulator

本文ROM表采用64个采样点。其波形仿真如图室7所示,从图中可以看出,地址位从00H变化到20H时,输出信号值从FFH变到00H,正好为正弦波的四分之一个周期,结果证明:通过查询该ROM表,可以生成不同频率的正弦波。

图7 正弦波形的仿真图Fig.7 The diagram showing a quarter of the stimulated sin wave

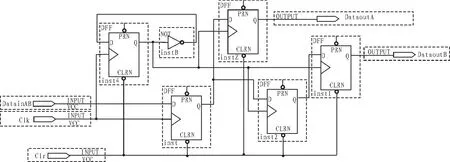

把上述各部分所生的symbol在QuartusII7.2提供的BlockDiagram/SchematicFile中用Graphic Editor编辑连接起来,就形成了图1的虚线所示的部分,编译后进行整体模块仿真,经过器件编程,可将整体模块程序烧写到合适的FPGA芯片中,再配以相应的D/A器件及其他外围电路,调试后即完成设计。

3 结束语

用FPGA来实现MSK信号调制器,电路简单,设计灵活,便于修改和调试,可靠性高。特别是对数控振荡器的设计,正弦函数的ROM表格,直接采用VHDL的CASE语句实现,避免了调用ROM块,降低了系统的设计规模,减少了系统对逻辑资料的需求;另外,Altera公司的QuartusII7.2应用软件具有较强大的开放性和综合性,它可以利用其它各种EDA资源以及先进的设计方法,使其功能更加完善和强大。它可以实现从简单的接口电路设计到复杂的状态机,甚至 “Sys-temon Chip”。它的可编程特性带来了电路设计的灵活性,缩短了产品的“Time ToMarket”。

[1]吉利萍.MSK调制技术研究[J].计算机工程应用技术,2009(18):4919-4920.

JI Li-ping.Research of MSK modulation technology[J]Computer Application Technology,2009(18):4919-4920.

[2]王兴亮,达新宇,林家薇,等.数字通信原理与技术[M].西安:西安电子科技大学出版社,2002.

[3]周维龙,姚晓玲.基于FPGA的QPSK调制器的设计与实现[J].湖南冶金职业技术学院学报,2008(4):99-101.

ZHOU Wei-long,YAO Xiao-ling.Design and realization of QPSK modulation based on FPGA [J].Journal of Huan MetallurgicalProfessionalTechnologyCollege,2008(4):99-101.

[4]刘国华,李二喜.基于FPGA的QDPSK调制器的设计与实现[J].电子设计工程,2011(19):22-25.

LIU Guo-hua LI Er-xi.Design and realization of QDPSK modulation based on FPGA[J].Electronic Design Engineering,2011(19):22-25.

[5]段吉海,黄智伟.基于CPLD/FPGA的数字通信系统建模与设计[M].北京:电子工业出版社,2006.

[6]杨威,左月明,刘洋,等.利用FPGA实现DDS信号发生器的研究[J].山西农业大学学报:自然科学版,2007,27(3):329-332.

YANG Wei,ZUO Yue-ming,LIU Yang,et al.The research on using FPGA to realize DDS signal generator[J].Shanxi Agric Univ:Natural Science Edition,2007,27(3):329-332.

Design and realization of MSK modulation based on FPGA technique

XIE Li-jun1,TAN Li-zhi2

(1.Changsha Professional Technology College,Changsha410003,China;2.Zhuzhou Professional Technology College,Zhuzhou412001,China)

The advantage of MSK is introduced,the implementation principle is analyzed.A high-preformance MSK digital modulator’s implementation method based on FPGA is proposed;The system is divied into serial/parallel conversion,differential encoding,NCO,phase shifter,multiplication circuit and adder using Top-to-Down design; And achieved the specific design of each module by schematic and VHDL;The simulation and experiment of FPGA design were given with QuartusII.Result shows the MSK modulator based on FPGA,simple in design,convenient to modify or debug,and it operates stable.

MSK;FPGA;differential encoding;NCO

TP29

A

1674-6236(2012)06-0016-03

2011-12-30稿件编号:201112167

谢丽君(1973—),女,湖南长沙人,讲师,高级技师。研究方向:电工电子和电气控制。