一种高线性度CMOS栅压自举采样开关

2012-08-10邓茗诚

杨 扬,王 军,邓茗诚

(西南科技大学 信息工程学院,四川 绵阳 621000)

0 引言

模数转换器是将模拟信号转换为数字信号的接口电路。它是连接模拟信号和数字处理电路的桥梁。随着数字信号处理技术和DSP处理器的发展。模数转换器也必须向高速高精度发展,而此类模数转换器通常采用流水线结构。采样保持电路作为流水线模数转换器的核心单元,其性能指标直接决定整个模数转换器的性能。随着采样速度和精度的不断提高,传统的采样开关已经无法满足要求。栅压自举采样开关具有良好的采样精度和线性度,已经成为采样开关的首选。本文首先分析了影响(MOSFET,Metal-Oxide -Semiconductor Field Effect Transistor)采样开关性能的非理想因素,接着提出了一种新型的栅压自举采样开关,最后通过仿真验证,结果显示这种开关的线性度高[1-4]。

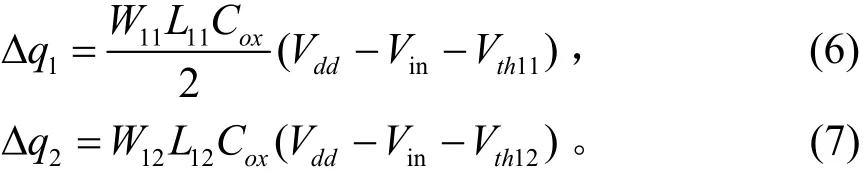

1 影响采样开关性能的非理想因素

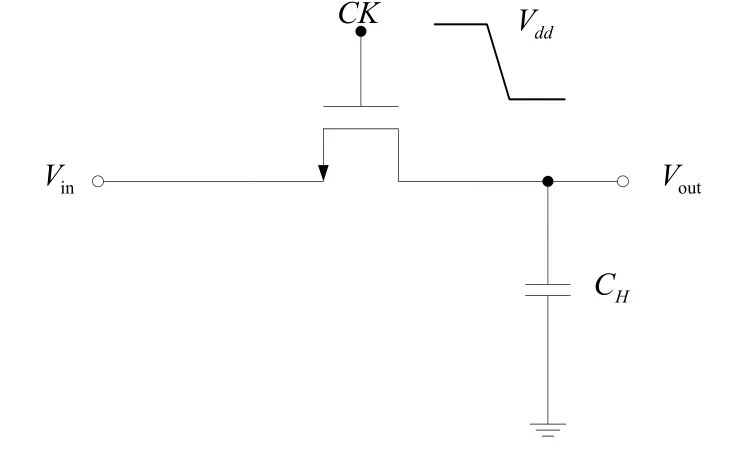

最简单的MOSFET采样保持电路只需要一个N型MOSFET和负载电容HC 就可以实现,如图1所示。CK为高电平时N型MOSFET开关导通,outV 跟随inV进行采样,对负载电容HC 进行充电。CK为低电平时N型MOSFET开关截止,HC 保持为采样电压,完成一次采样保持过程。

1.1 开关导通电阻

开关在导通情况下可以等效为一个阻抗为onR的电阻,在开关设计中开关导通电阻的非线性在很大程度上影响着开关的线性特性。N型MOSFET采样开关的导通电阻可由式(1)表示:

图1 简单的采样保持电路

1.2 沟道电荷注入

当开关导通时,沟道中的电荷可以表示为:

当开关断开后,沟道中的电荷通过源、漏端流出。注入到右边的电荷使得保持在HC 上的采样值发生了变化。假设注入到采样电容HC 上的电荷占沟道中的电荷的比例为k。则由沟道电荷而引起的采样值的变化为:

因此电荷注入而引起的误差与输入电压inV相关,这样就会造成采样保持电路的非线性误差。

1.3 时钟馈通效应

时钟跳变也会通过栅漏或栅源电容耦合到HC上。由时钟馈通效应而引起的采样值的变化为:

2 采样开关设计

栅压自举采样开关是用在采样保持电路前端以提高采样电路信号线性度的开关电容电路,它通过采用预充电的电容稳定开关管的过驱动电压,因而可以获得良好的线性度[7-8]。

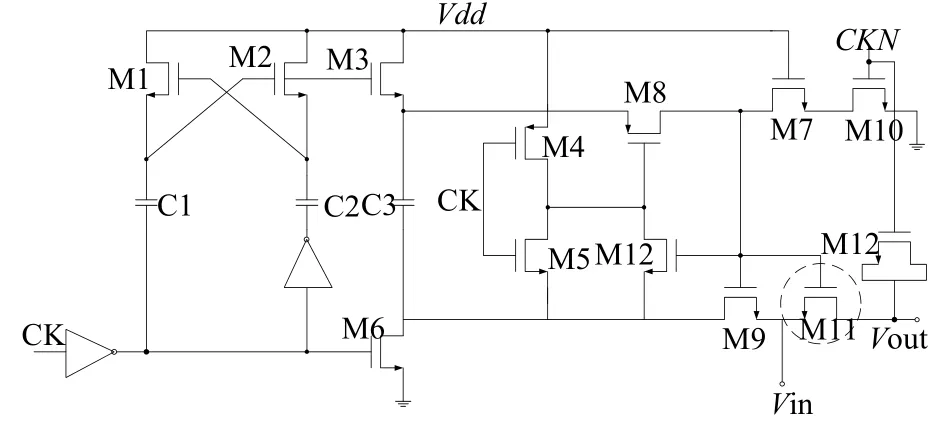

图 2为本文所设计的栅压自举采样开关,M11在单个时钟CK的控制下实现采样开关的功能。

工作原理如下:CK为低电平时,M10导通,M11的栅极通过M7和M10接地,M11断开。同时,M3和M6导通,对C3充电直至其电压等于Vdd,M8和M9在C3充电的时候保持断开,对M11进行隔离。CK为高电平时,M3、M6断开,M8和M9导通,这样C3上电压就被加到M11的栅源两端,存储在电容C3上的电荷保持不变,使得M11栅源保持Vdd的压差。即对M11来说=,不受输入信号的影响。

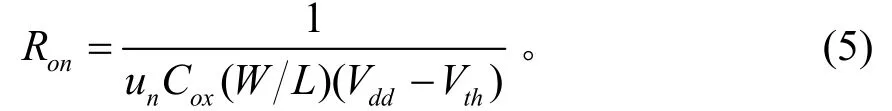

根据式(1),此时导通电阻为:

图2 栅压自举采样电路

可以看出与式(1)相比,导通电阻onR 变成一个与输入信号inV 无关的电阻,线性度得到了很大的提高。

此外,M12是虚拟管,用来减小 M11的电荷注入和时钟馈通。其原理如下:当 M11断开后,M12导通,M11沟道中原本会注入到HC 上的电荷将被M12吸收。

3 仿真验证

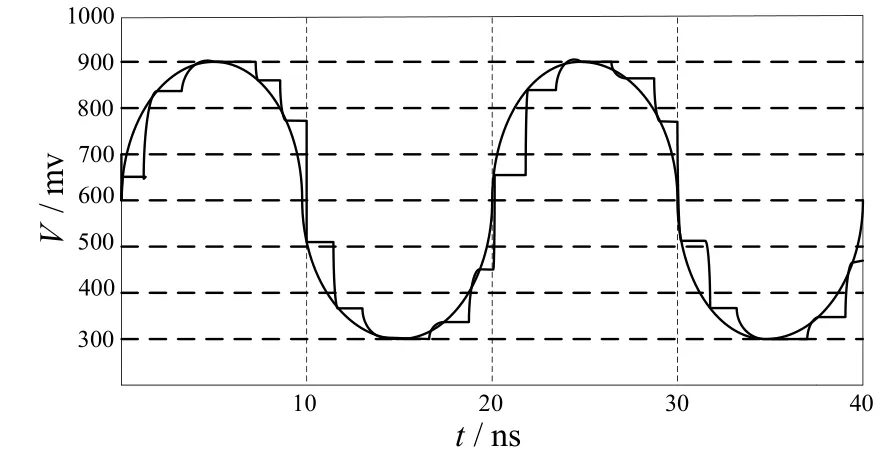

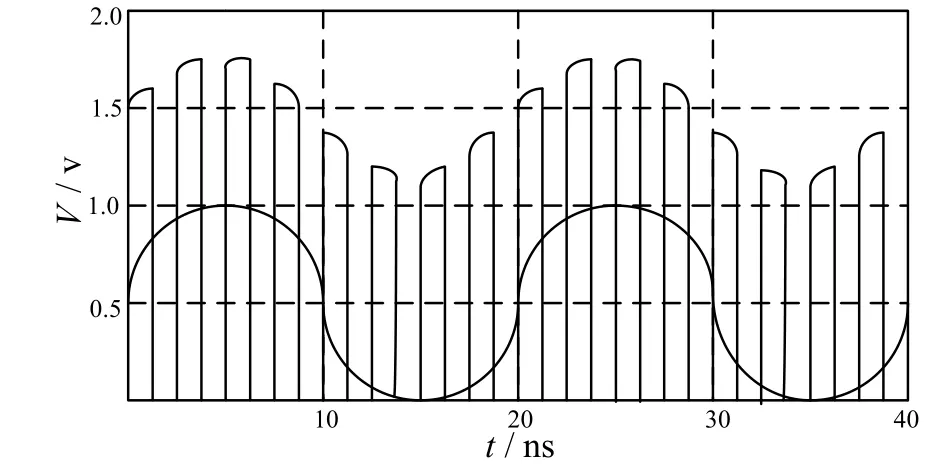

采用华润上华0.13 um标准数模混合工艺,采用 Cadence软件对电路进行了仿真。电源电压为1.2 V,输入信号为50 MHz正弦波,峰峰值为600 mV,采样时钟频率为 500 MHz,时钟上升下降时间为0.1 ns,在温度27℃、TT工艺角下分别对栅压自举采样开关进行了仿真。

图3是栅压自举采样波形的采样波形。栅压自举采样开关的采样精度高,波形理想。

图3 栅压自举采样开关输入输出波形

图4是栅压自举采样开关输入信号变化时,采样开关栅压变化的仿真波形。采样开关的栅压随输入信号变化而等量改变,所以采样开关导通时,栅源电压基本保持不变,不受输入信号幅度的影响,线性度高。

图4 栅压自举采样开关的栅源电压仿真波形

4 结语

分析了影响MOSFET采样开关的非理想因素,提出了一种高线性度栅压自举自举采样开关。采用预充电的电容稳定开关管的过驱动电压,消除了采样开关因输入电压引入的非线性以及沟道电荷注入的影响。仿真结果表明所涉及的的栅压自举采样开关可以应用于高速高精度模数转换器中。

[1] 胡晓宇,周玉梅.一种用于 14bit50MHz流水线模数转换器的 CMOS采样开关[J].半导体学报,2007,28(09):1488-1493.

[2] 唐江波,王宁章,卢安栋,等. 一种高增益低功耗 CMOS LNA设计[J].通信技术,2011,44(04):175-178.

[3] 秦国宾,王宁章. 2.4GHz CMOS线性功率放大器设计[J].通信技术2010, 43(09):170-173.

[4] 王伟峰,夏立诚,王文骐. 高速宽带应用的毫米波 CMOS集成电路[J].信息安全与通信保密,2007(06):70-73.

[5] RAZAVI B.Design of Analog CMOS Integrated Circuits[M].陕西:西安交通大学出版社,2003.

[6] ALLEN P E, HOLBERG D R. CMOS Analog Circuit Design[M].北京:电子工业出版社,2010.

[7] ANDREW M A, PAUL R G. A 1.5V 10bit 14.3 MS/s CMOS Pipeline Analog to Digital Converter[J]. IEEE J Sol sta cire, 1999,34(05):599-606.

[8] DESSOUKY M, KAISER A. Input Switch Configuration Suitable for Rail-to-rail Operation of Switched Opamp Circuits[J]. Elec Lett, 1999,35(01):8-10.