基于FPGA的实时直方图统计设计

2012-06-25徐书文

张 科,徐书文,葛 珊

(中国电子科技集团公司第三研究所,北京 100015)

1 直方图统计方法简介

直方图可以提供图像灰度分布的统计特征,是图像处理的基本方法之一。直方图统计方法常应用于图像增强、图像压缩和图像分割等图像处理基础理论分析和应用中,也广泛应用于遥感、遥测、成像跟踪与制导等军事领域中。

随着DSP[1]应用技术的发展,利用DSP完成实时直方图统计的方法主要有3种:1)专用DSP芯片;2)DSP+片内DRAM结构;3)DSP+片外DRAM结构。

第一种专用DSP芯片是指通过简单外围控制设置完成固定直方图统计功能的电路;第二种DSP+片内DRAM结构是指DSP芯片自身具有大容量片内DRAM,并有专用的视频接口,通过DSP编程实现直方图统计功能,如图1所示;第三种DSP+片外DRAM结构是用片外DRAM做帧存,采用乒乓切换控制数据存储。当1个帧存写数据时,DSP对另一帧存进行读操作,通过DSP编程实现直方图统计功能[2-4],如图2 所示。

图1 DSP+片内DRAM结构

图2 DSP+片外DRAM结构

使用专用DSP芯片实现直方图统计时,速度快、实时性好,可以达到像素时钟的速度。但是这种专用DSP芯片只能用于直方图统计,不能改作其他用途,而且体积大,不利于小型化。对于DSP+片内DRAM结构和DSP+片外DRAM结构,是通过DSP编程实现直方图统计的,实时性稍差,并且实现直方图统计功能占用了DSP运行时间和资源。但是,这2种结构灵活性很好,通过改变DSP程序就可以改作其他用途。

本文介绍了一种采用基于FPGA[5]实现实时直方图统计功能的设计方案,该设计方案不占用DSP资源,实时性可以达到像素时钟的速度;通过改变程序,可以改作其他用途。这就是说,采用FPGA实现实时直方图统计设计方案既继承了上述3种结构的优点,同时又克服了上述3种结构的缺点。

2 逻辑结构及原理

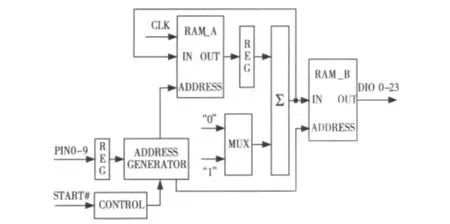

对于灰度级为[0,L-1]范围的数字图像,其直方图是离散函数h(rk)=nk,这里rk是第k级灰度,rk∈[0,L-1],nk是图像中灰度级为rk的像素个数。直方图直观地反映了1幅图像灰度的分布情况,是图像分割算法中常用的方法。灰度直方图的特点是横坐标为灰度值rk,纵坐标为像素数nk。在FPGA设计中实现直方图统计,首先要考虑图像灰度值和统计值的映射关系,在这里采用了双RAM结构,用图像灰度rk作为RAM的地址,RAM中的数据对应像素数nk,从而实现在存储器中灰度和像素数的对应关系,基于FPGA的实时直方图统计原理如图3所示。在图3中,CLK为像素时钟;START#为直方图统计起始信号;PIN 0-9为10位的像素灰度数据输入;DIO[23..0]为灰度对应像素数的统计结果。图中RAM_A用于完成直方图统计像素数的读取、累加和回写,RAM_B通过外部CPU配置读使能和读地址,用于读取直方图统计最终结果。

图3 基于FPGA的实时直方图统计原理框图

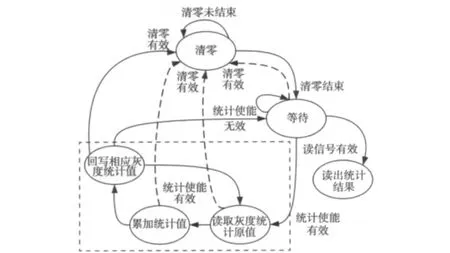

FPGA的软件编程采用VHDL语言,在QuartusII9.0集成开发环境综合,FPGA软件设计采用mealy型有限状态机。为了实现1个像素灰度值的直方图统计在相应的像素周期内完成,需要在1个像素时钟周期内分别实现RAM数据的读出、累加、写入,因此,这里选用4倍频像素时钟作为直方图统计的同步时钟。从设计的逻辑完备性考虑,需要考虑各种状态转换的情况,防止出现由于外部信号时序冲突导致的未知状态而不能跳转。直方图实现过程中可能出现的各种状态及跳转关系如图4所示。

图4 直方图统计状态转换图

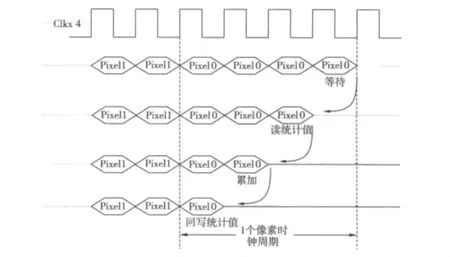

从图4中可以看到,整个设计有4个状态,即清零、等待、直方图统计、读出统计结果,各状态转换由外部控制信号触发。其中,清零信号的优先级最高,其次是统计使能信号,读信号在统计结束后有效,等待状态为中间空闲态。直方图统计状态中还有4个子状态,即空闲(等待)、读取灰度统计原值、累加统计值、回写相应灰度统计值,这4个子状态以4倍频像素时钟为同步时钟进行流水操作,如图5所示。

图5 灰度统计值累加时序

该设计中像素灰度位宽为10 bit,因此RAM地址需要1024个;直方图统计模块像素灰度统计数值位宽为24 bit,即1幅图像的像素数最大可以达到16 Mbit,RAM需要的缓存空间为1024×24 bit=24576 bit,满足一般实时图像分辨力的要求。依据上述直方图设计分析,FPGA芯片选用Altera公司CycloneⅡ系列器件EP2C5Q208I8N芯片,该芯片属于Altera公司低成本的FPGA系列,容量中等。EP2C5Q208I8N的主要资源包含:1)内部逻辑单元多达4608个,最大系统门数约合9万门以上;2)RAM资源共计119808 bit,可以由用户配置为FIFO,DPRAM等模块;3)2个锁相环;4)13个18×18的嵌入式乘法器;5)IO管脚数为142。

针对该设计,该款FPGA芯片资源有较多冗余,具有可扩展性。如果需要处理更高分辨力的图像,可依据该设计提供的方法选用资源更丰富的FPGA芯片。

3 设计仿真及验证

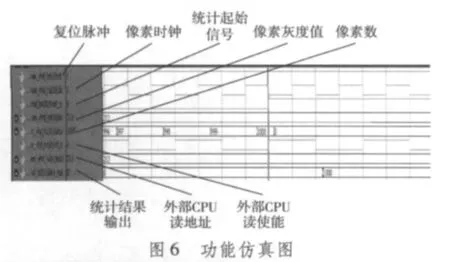

该设计采用Modelsim软件进行功能仿真,为了便于验证,仿真时选取连续相同灰度进行统计,仿真结果如图6所示。图6中rst为清零脉冲信号;clk为像素时钟;start_n为直方图统计起始信号;pin为像素灰度值;data为回写双RAM的灰度统计值;rd_n为微处理器读取统计结果的读信号;add为微处理器读取统计值的相应灰度值;data_out为微处理器读出的统计数据。start_n选通了1000个像素时钟周期,因此,像素统计结果为1000个。

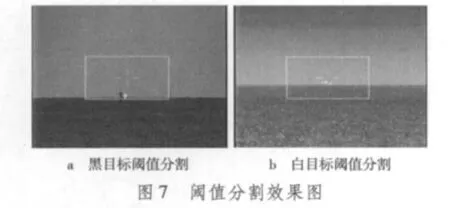

该设计还在某设备的阈值分割电路中得到应用,阈值分割电路采用目标灰度直方图实时统计进行分割门限的实时计算,从而实现目标的实时分割,如图7所示。在图7中,波门内十字线下部的白色标记为分割出的目标部分。

4 结论

本文提出了一种基于FPGA的实时直方图统计设计原理和方法,并经过软件仿真和实际应用硬件电路的验证,实验结果证明该设计不仅实时性强,占用系统资源少,满足设计需求,而且,采用VHDL语言编程,程序的可移植性强,可以方便地移植到更大规模的FPGA芯片中,为数字图像的直方图实时统计处理提供了1种实用的方法。

[1]韩文俊,张艳艳,任国强,等.基于双DSP的实时高清H.264视频编码器实现[J]. 电视技术,2010,34(5):33-35.

[2]李弼程,彭天强,彭波.智能图象处理技术[M].北京:电子工业出版社,2004.

[3]阿森顿.VHDL设计指南[M].葛红,黄河,吴继明,译.北京:机械工业出版社,2005.

[4]Harris Semiconductor.HSP 48410 datasheet[EB/OL].[2011-10-10].http://www.datasheets.org.uk/HSP48410/Datasheet-028/DSA00501738.html.

[5]王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):32-35.