基于PC104和FPGA的数据采集系统的研究和实现

2012-05-23孙树敏张海涛李广磊毛庆波

程 艳 ,孙树敏 ,张海涛 ,李广磊 ,袁 帅 ,赵 鹏 ,毛庆波

(1.山东电力集团公司电力科学研究院,山东 济南 250021;2.山东彼岸电力科技有限公司,山东 济南 250101)

0 引言

电力系统的无功补偿和无功平衡,是保证电网电源质量的基本条件,对保证电力系统的安全稳定与经济运行起着重要作用。尤其是对于并网的风电场来说,所安装的动态无功补偿装置,是作为调节本风电场无功的电压平衡的最主要的电气设备,它的运行状态和运行效果的优化与否[1],对于风电场的稳定运行有着重要作用,因此有效、准确地监控和测量动态无功补偿装置的运行状态则显得尤为重要。

数据采集系统可以检测风电场并网点、主变低压侧和动态无功补偿装置的三相基波电压、电流,从而分析并网点的电能质量和无功补偿装置的运行状态,并且可以对电压的骤升、骤降进行监测和记录,具有较强的实用性。

数据采集系统采用PC104+FPGA方案[2],数据采集用FPGA和调整同步A/D来实现,经接口芯片 PCI9054[3]通过 PCI总线与 PC104 实现双向数据通信,从而在PC104上进行高速数据处理。

1 采集卡总体硬件设计

数据采集系统采集卡选用了具有低系统占用率、高传输速率特性的PCI总线,以保证采集卡与主机间海量数据高速传输的可靠性[4]。 由于PCI总线复杂的总线逻辑和电气规范,采集卡使用专用PCI总线控制芯片负责与PCI总线连接。根据传输速率的要求以及采集卡需使用DMA传输方式的特点,选用了由PLX公司开发研制的PCI9054芯片。采集卡的核心处理器件是FPGA,数据的实时采集由它控制完成。FPGA选用美国ALTERA公司Cyclone系列芯片,型号为EPlC6Q240C8。由于数据采集要求高度同步,模数转换选取TI的ADS8364芯片。数据采集卡的总体硬件设计结构如图1所示。

图1 数据采集卡的硬件结构框图

1.1 PCI9054的功能设置及硬件连接

PCI9054作为PLX公司研制的32位33 MHz的PCI总线主控I/O加速器接口芯片,实现PCI总线和LOCAL总线之间数据传输,通过外围控制电路实现PC104和外围设备的桥接,该芯片符合PCI规范2.2版本,同时兼容PCI规范2.1,本地端突发传输速率可达峰值132 MB/s,支持复用或非复用的32位局部总线操作。该芯片支持VPD的PCI扩展,支持PCI双地址周期,地址空间高达4 GB。同时具有可选的串行EEPROM接口,8个32 Bit Mailbox寄存器和2个32位Doorbell寄存器。芯片核心采用3.3 VCMOS技术,兼容5 V信号环境,符合低功耗的要求。

PCI9054支持三种数据传输模式:PCI主控方式——允许本地的CPU访问PCI总线上的存储器和I/O接口;PCI从方式——允许PCI总线上的主设备访问本地总线上的存储器和I/O接口;DMA方式——由DMA控制器读PCI存储器内容到本地存储器或将本地存储器的内容写到PCI存储器。根据本装置的要求可以采用PCI从方式与PCI总线数据传输。PCI9054需要1片EEPROM对其内部配置寄存器初始化。在EEPROM中需事先烧入对应寄存器的初始值,在PC启动时,PCI9054很快地自动将EEPROM中值读入对应寄存器,然后PC根据寄存器中的值为PCI9054分配中断号、内存空间、I/0空间等系统资源。FPGA、PCI9054及PCI总线连接框图如2。

图2 PCI信号连接示意图

1.2 FPGA电路的设计与实现

FPGA是整个系统的核心,控制数据采集、A/D转换以及数据的传输[5]。

FPGA基本由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。FPGA继承了ASIC的大规模、高精度、高可靠性的优点,而且可以反复的编程、擦除,开发工具智能化,功能强大,支持软硬件协同设计,可以完成某些告诉复杂设计,提高系统的工作频率与效能,同时克服了普通ASIC设计周期长、投资大、灵活性差的缺点,逐步成为复杂数字硬件电路设计的理想首选。

采集卡中FPGA功能:拥有内嵌锁相环,利于FPGA内部的时钟管理,提高系统的稳定性;拥有充足的RAM单元,使开辟较大的FIFO空间成为可能,从而延长FIFO间切换存储过程中产生中断的间隔时问。

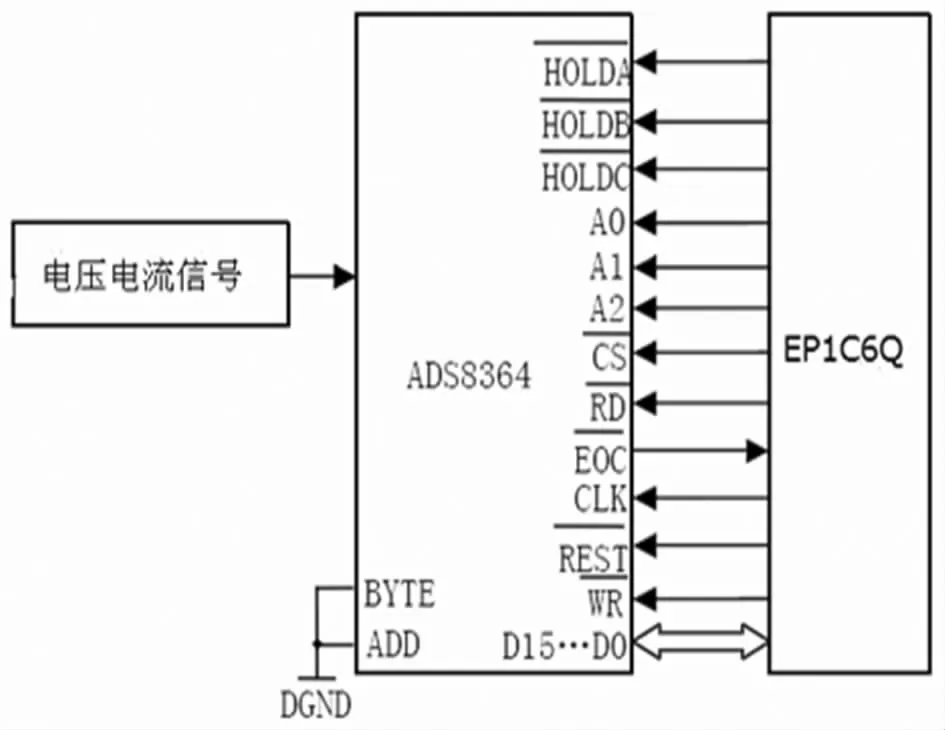

ADS8364是高速、低功耗、六通道同时采样和转换的十六位模数转换器并行输出。采用+5 V工作电压,50 kHz时拥有80 dB共模抑制的全差分输入通道,使其在噪声较大的环境中明显优于其他A/D芯片。ADS8364最大时钟频率可达5 MHz,可在20个时钟周期内完成采样/转换。芯片还包括6个4 μs连续近似的模数转换器,6个差分采样放大器,带REFIN和REFOUT引脚的内部+2.5 V参考电压。以及高速并行接口,又有高达200 kbps的通道吞吐率。ADS8364拥有A、B、C三组6个模拟输入,每个输入端有1个ADCs可以成对同步工作,3个保持信号用来指定通道进行采样、转换或者保证几个通道能同时进行采样、转换。

ADS8364与FPGA的接口连接如图3所示。

图3 ADS8364与FPGA连接示意图

3 个保持信号(HOLDA,HOLDB,HOLDC)启动指定通道的转换。 当3个保持信号同时被选通时,启动转换,转换完成后,把转换结果将保存在6个寄存器中并产生EOC信号。A/D转换精度为16位,最高位为符号位,数据输出方式可以由BYTE,ADD与地址线A2、Al、A0的组合控制。

图4 ADS8364的工作时序图

ADS8364的工作时序图见图4,在ADS8364的开始转化信号HOLDX保持至少20 ns的低电平时才能保证有效。当转换结果被存人输出寄存器后,引脚EOC的输出将保持半个时钟周期的低电平。FPGA为ADS8364提供CLK和HOLDX信号,当转换完成后接收EOC信号,通过置RD和CS为低电平可使数据读出到并行输出总线。FPGA—EPlC6Q240C8内部逻辑电路的设计采用Altera 公司提供的 QuartusⅡ[6]软件完成,采用嵌入IP核可以方便对ADS8364进行控制,用内部RAM组建一个FIFO存储区,把采集的数据存储在FIFO内,可以减少系统中断,当FIFO内的数据达到一定数量后,把向系统申请中断。

1.3 采集卡驱动开发

PCI数据采集卡设计的另一关键问题就是驱动程序的开发[7]。 Windows操作系统为了保证系统的安全性、稳定性和可移植性,对应用程序访问硬件资源加以限制。因此,需要通过设备驱动程序实现应用程序对PCI硬件设备的访问。在Windows 9x/NT中,设备驱动程序必须根据Windows驱动程序模型设计。设备驱动程序的关键是如何完成硬件操作,基本功能是完成设备的初始化、端口的读写操作、中断的设置和响应及中断的调用、以及对内存的直接读写。为简化设备驱动程序的开发,选用了Jungo公司的WinDrive编写工具。用WinDriver实现PCI设备驱动程序的步骤如下。

1)把制作完成的板卡插入PCI插槽,开机用WinDriver的Drive Wizard工具查找并选择所要编写驱动程序 PCI板卡。

2)用Drive Wizard的Generate.INF File产生INF文件,然后添加新硬件。

3)Drive Wizard会自动检测计算机硬件资源,对PCI板卡上的配置寄存器、I/O空间、内存范围、中断、片内寄存器等进行设置。

4)在 Build菜单中选择自动生成源代码,Drive Wizard自动生成文件。

5)在Visual C++6.0中对上面生成的源代码进行编译、链接和运行。

6)编写驱动的动态链接库DLL文件。根据本系统的一些具体的功能要求,在Visual C++6.0中对源代码进行功能添加和代码调整,使得修改和重组后的驱动程序高效、安全地执行,生成动态链接库DLL文件。手续开发的软件通过DLL文件实现与数据采集卡的通信。

2 装置系统软件开发

系统软件开发基于PC104计算机,采用PCM-3362,该PC104的 CPU采用 Intel Atom N450,频率为1.66 GHz,支持DDR内存,最大内存2 GB,基本输入输出系统为AMI 16Mbit Flash bios,支持VGA1和8-bit LVDS,支持嵌入式软件APIS和Utilities,拥有4个 USB2.0、2个RS-232和1个RS-422/485,采用5 V、12 V供电。

在该装置中,采用Visual C++6.0作为软件开发环境,通过调用驱动所提供的DLL文件对数据采集卡进行操作。 读取采集卡采用中断方式,当采集卡FPGA的FIFO中的数据达到一定数量后,会向PCI申请中断,PC104接收到中断信号后,响就中断,把数据读取到PC104的内存,并把数据做FFT变换,计算出电压,电流的频率,大小,相位等信息,利用这些信息做进一步处理,可计算无功功率,有功功率等。所计算的结果可以通过数据库在本地系统存储管理,方便历史数据查询,生成数据报表。在Visual C++可以方便利用socket把数据传送至远端服务器。

3 样机实验

试验样机采用图1所示数据采集系统主电路。交流输入电压为110 kV,输入电流为50 A。

系统采样频率为64kHz,使用快速傅里叶变换,计算出得到相电压为63 522.20 V,电流为49.99 A,功率因数为0.99,得出有功功率为9430.64137kW,无功功率为1 339.692 38 kvar,数据采集系统显示结果如图5所示。

上述实验结果证明了基于PC104和FPGA的数据采集系统的研究的可行性和可操作性,显示结果精度比较高,计算比较精确。

4 结语

提出的基于PC104工控机和FPGA的数据采集系统的实现方法,实现了对风电场动态无功补偿装置的运行状态的检测,完成了电压、电流信号的同步采样和数据传输,能有效的对电能质量进行分析和无功补偿装置的运行状态进行检测,系统的网络通信实现了对系统实时监控,同时试验验证了该数据采集系统算法和操作系统的稳定性和实用性,表明了该系统的研究和实现对电网电能质量的保证、电力系统的安全稳定和经济运行具有重要作用和意义,项目研究的推广具有重要的实用价值。

图5 数据采集系统显示结果