VxWorks下基于ML507嵌入式系统的中断处理

2012-04-23夏伟杰

单 寅,夏伟杰

(南京航空航天大学电子信息工程学院,江苏南京 210016)

VxWorks作为目前较为主流的嵌入式操作系统,被广泛运用于航空与控制等方面,基于某型号飞机的虚拟仪表的GPU板卡,采用VxWorks作为顶层控制,其中采用中断机制与外界通信是一个重要手段,由于硬件环境为Virtex5 FXT型号的FPGA,CPU为IBM公司Powerpc440x5处理器,理解其特有的架构,并编写相应的中断处理程序,对于操作系统的完整移植以及上层程序的正常运行至关重要。

1 Virtex5的中断响应过程

FPGA内嵌的IBM PPC440处理器有两个中断引脚,一个关键异常引脚与一个外部中断引脚。在构建嵌入式系统时共有两种处理中断的方式:(1)外部中断直接引入外部中断引脚。(2)为能处理较多的中断,引入一个外扩的中断处理器XINTC,中断处理器连接PPC440外部中断引脚,中断控制器共可处理共32个优先级的中断,从0号中断开始优先级逐次降低。

1.1 中断控制器介绍

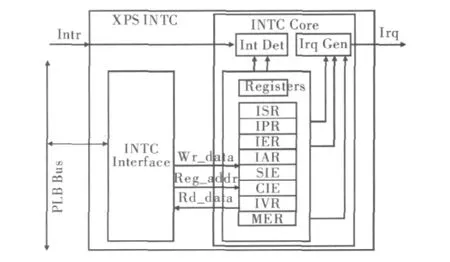

中断控制器由中断核和总线接口组成,中断核可与响应的逻辑接口总线配合,挂接在PLB总线上。图1为中断控制器(INTC)响应中断的原理图。通过PLB总线下INTC Interface向寄存器写值,使能相应中断位。连接在INTC的中断源产生中断信号Intr,被INTC检测到后,因为寄存器相应中断位被使能,就会产生Irq信号给PPC440外部中断引脚[1]。

中断控制器主要有几个重要的寄存器,如图1所示,Interrupt Status Register(ISR),Interrupt Enable Register(IER),Master Enable Register(MER)。MER是一个可读写寄存器,向MER写1才能允许向外输出Irq信号。ISR是一个32位只读寄存器,相应位为1代表相应的中断被使能。IER是个32位的可读写寄存器,向相应位写1可以将ISR相应位置1。

图1 中断控制器原理框图

1.2 INTC驱动的中断处理机制

中断驱动实际上是在内存中构造一个中断向量表,中断控制器的数据结构如下:

typedef struct{

u16 DeviceId;/**中断控制器对应的设备号*/

u32 BaseAddress;/**中断控制器基地址*/

u32 AckBeforeService;/**读取ISR寄存器的值以判断正在触发的中断号*/

u32 Options;/**中断控制器配置*/

XIntc_VectorTableEntry HandlerTable[XPAR_INTC_MAX_NUM_INTR_INPUTS];

}XIntc_Config

HandlerTable[XPAR_INTC_MAX_NUM_INTR_INPUTS]这一结构体数组即为中断向量表,宏XPAR_INTC_MAX_NUM_INTR_INPUTS为系统中所有中断的总数。

在Xilinx提供的BSP中,底层操纵中断控制器的驱动函数为XIntc_Connect和XIntc_Enable,即IntConnect与 IntEnable函数具体实现是 XIntc_Connect与XIntc_Enable,void XIntc_Enable(XIntc* InstancePtr,u8 Id),InstancePtr是中断控制器的地址,Id是想要使能的中断号

……

Mask=XIntc_BitPosMask[Id];

CurrentIER=XIntc_In32(InstancePtr- >BaseAddress+XIN_IER_OFFSET);

XIntc_Out32(InstancePtr- >BaseAddress+XIN_IER_OFFSET,

(CurrentIER|Mask));

通过此操作,给IER寄存器相应位写1,使能相应中断。int XIntc_Connect(XIntc* InstancePtr,u8 Id,XInterruptHandler Handler,void*CallBackRef),Handler是用户自己的中断服务程序,可以是任何操作,CallbackRef是要传递给服务程序的参数。

……

InstancePtr- >CfgPtr- >HandlerTable[Id].Handler=Handler;

InstancePtr- >CfgPtr- >HandlerTable[Id].CallBackRef=CallBackRef;

由此根据中断号Id将参数与程序放入中断注册表中。在BSP的sysInterrupt.c文件中,将这两个函数封装在IntConnect与IntEnable内,提高了程序的可移植性。

2 PPC440中断处理

2.1 PPC440相关寄存器介绍

Powerpc440处理器是一个32位精简指令集的CPU,与异常处理相关的寄存器有IVOR0~IVOR15,这16个寄存器用于存储异常向量入口的偏移地址,其中IVOR4对应的是外部异常,也就是文中所关心的异常。SRR0和SRR1用于保存和恢复机器状态。MSR是机器状态寄存器,用于指示处理器的状态[2]。

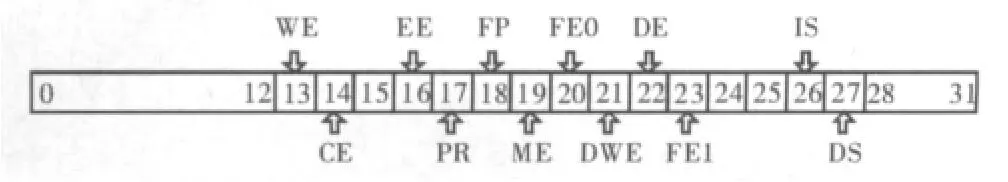

图2为机器状态寄存器(MSR)示意图。CE为关键异常位,EE为外部异常位。这里主要关注的是EE,通过将EE位置1,可以使能外部中断异常。通过查看Powerpc汇编指令集,对MSR寄存器操作的指令为mtmsr和mfmsr,其中mtmsr为读出MSR中内容,mfmsr为向MSR写入内容。在系统开始时初始化异常向量表,首先应将对应的异常向量装入储存异常向量入口的寄存器中。

图2 机器状态寄存器

2.2 异常处理程序

异常只能发生在处理器的内核中,在总线的中断处理中没有异常这个概念。异常是指处理器有意或无意的停止正常的运行,如意外重启、软件中断等。而在PPC440中,所有的外部中断被当做一个特殊的异常来进行处理。当发生异常/中断时,系统自动跳转到异常向量表(Interrupt-handler Table)中。异常向量表将异常/中断与其异常向量相关联,异常/中断通过异常向量表找到自己的向量。通过异常向量在中断控制器中找到对应的处理程序,这样就与前面所说的总线中断控制器对应。通过excIntConnect函数将外部中断与异常处理程序挂接,excIntConnect((VOIDFUNCPTR*)_EXC_OFF_INTR,(VOIDFUNCPTR)ExternalISR),_EXC_OFF_INTR这个宏定义在VxWorks6.5安装目录下Powerpc处理器对应的excPpcLib.h文件中,代表外部异常向量;ExternalISR为异常处理程序,此处理程序主要负责对中断控制器进行发出中断后的操作,具体操作为利用IO函数XIo_Out32和XIo_In32读写各个中断寄存器,中断优先级从高到低检测哪个中断是被激活的,通过向IAR寄存器相应位写1可以清除中断请求。

如图3所示,程序首先进入异常向量表中注册的Xintc_DeviceInterruptHandler,该服务程序是系统层的注册,然后进入HandlerTable,用户自己的服务程序通过BSP中的中断控制器驱动程序注册在这个HandlerTable中。这样就可以完成一次中断的流程。

图3 中断处理流程框图

3 中断服务程序

3.1 中断服务程序设计

由于VxWorks下中断服务程序不能调用可能引起阻塞的函数,所以处理方法是拆分中断服务程序,分为两部分:一部分专门做判断中断类型,禁止中断等,称为中断服务程序;第二部分将多数需要处理的操作,尤其是可能引起任务阻塞的操作放在此执行,称为中断服务任务。两部分间采用VxWorks特有的信号量机制通信。由于获取信号量会造成任务阻塞,中断服务程序中不能获取信号量,但可以释放信号量,从而解除等待在该信号量上的一个任务[3]。

3.2 中断服务程序性能

在调试实时系统过程中,中断程序的性能是一个重要的指标,所以在调试过程中,需要使用时间戳功能。时间戳与sysclk不同,sysclkRate可以看做内核调度的频率,一般默认较低,在本系统中为60,即每秒有60个TICK,如果修改的过高会导致CPU系统占用率过高。而时间戳与CPU的主频相关,与RTOS调度无关。sysTimestamp是通过读取计时器当前计数值来实现高精度定时的。时间戳显示的是一秒内的时间状态,溢出后就会从0开始重新计数,所以首先要确保任务运行在1 s内可以完成,否则一旦时间戳溢出,得出的数据就无意义了[4]。调试时可以使用打印两次时间戳的方式查看任务所用时间,即两次数据之差乘以频率即为任务所用时间。

3 结束语

嵌入式操作系统VxWorks现被广泛应用于各类实际工程中,其中中断处理的性能直接影响整个系统的性能。由于ML507开发板FPGA和PPC440双核的特殊性,理解基于该板卡的中断处理流程是一个难点。通过研究驱动程序的内容,对深入了解硬件与FPGA逻辑的工作原理有帮助。

[1] Xilinx,Inc.DS516[M].USA:Xilinx,Inc,2009.

[2] International Business Machines Corporation.PPC440x5 CPU CORE User's Manual[M].USA:International Business Machines Corporation,2003.

[3] 王韬,杨士中,谭晓衡.基于MPC860和VxWorks的嵌入式中断处理设计[J].电讯技术,2005(1):45-50.

[4] 陈育智,温彦军,陈琪.VxWorks程序开发实践[M].北京:人民邮电出版社,2004.