一种单端10-bit SAR ADC IP核的设计

2012-01-15余昭杰王富昕杨小天

李 靖,余昭杰,高 榕,王富昕 ,杨小天

(1.吉林大学 电子科学与工程学院 集成光电子学国家重点联合实验室吉林大学实验区,吉林 长春130012;2.吉林大学 计算机科学与技术学院,吉林 长春 130012;3.吉林省建筑工程学院 吉林 长春 130118)

随着集成电路和数字信号处理技术的快速发展,我们可以在数字域里实现比模拟域里更高精度,更快速度,更低价格的各种信号处理功能,因此,模数转换器作为模拟系统和数字系统的接口就变得非常重要。而在各种类型的模数转换器当中,逐次逼近型的模数转换器(SAR ADC)因为其低功耗,中等精度和中高分辨率而得到了广泛的应用[1]。而SAR ADC从输入来分,可以分为单端输入和双端(全差分)输入。虽然一个双端SAR ADC电路架构可以获得更好的共模抑制比和和较少的失真,而得到了广泛的应用,但在现实生活中对单端的ADC仍有一定的需求,如光栅尺中绝对码道信号的检测。本文则是在一种常见单端SAR ADC电路架构的基础上[2],对D/A转换器进行了改进,在不增加电容面积的情况下,减小了D/A转换时电容和开关所消耗的能量,减小了电容阵列转换的建立时间。

1 ADC整体电路设计

本文设计的单端SAR ADC的整体架构如图1所示,主要包括以下4个部分:采样保持电路(Sample and Hold)、比较器 (Comp)、10-bit 逐 次 逼 近 寄 存 器 及 控 制 电 路 (SAR LOGIC)、D/A 转换电路(DAC)。

输入电压Vin通过采样保持电路得到采样电压Vsh,Vsh与DAC的输出Vdac通过比较器进行比较,比较结果传递给逐次逼近寄存器,逐次逼近寄存器一方面输出比较结果,另一方面控制DAC的转换开关,以便进行下一位的转换。

1.1 SAR ADC的工作流程

SAR ADC的工作流程如图2所示,它主要可以分为采样、清零阶段和比较阶段。

第一步:采样、清零阶段。采样保持电路中的开关Sa闭合,Vin=Vsh, 属于跟随阶段;DAC 中的电容 C1p~C10P和 C1n~C10n的下级板全部接GND,开关EN闭合,Vdac接GND,DAC处于清零阶段。

第二步:比较阶段。采样保持电路中的开关Sa断开,Vsh为采样得到的电压;DAC中的电容C1p~C10p的下级板接Vref,其余开关不动,而开关EN断开,此时DAC的输出结果:

Vsh与Vdac进行比较,如果Vsh大于 Vdac,则比较器输出为1,即D1=1,而逐次逼近寄存器根据比较结果,将电容C10n(MSB电容)的下级板偏转到Vref;反之 D1=0,C10p的下级板偏转到GND。其余电容保持不变。

图1 本文设计的单端10-bit SAR ADC的整体架构Fig.1 The whole framework of the proposed single-ended 10-bit SAR ADC

图2 本文所提出的SAR ADC的工作流程Fig.2 Flow chart of proposed SAR ADC

第j步:根据上一步比较的结果,得到DAC的输出如下:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即 Dj-1=1,而逐次逼近寄存器根据比较结果,将电容 C(11-j)n的下级板偏转到 Vref;反之 Dj-1=0,C(11-j)p的下级板偏转到 GND。其余电容保持不变。直至j=11,比较结束,进入下一个转换周期。

1.2 DAC电路架构

本文采用的DAC架构如图1所示,主要采用分割二进制电容加权结构[3],由逐次逼近逻辑(SAR)产生的控制信号S0到S11来控制DAC的开关。其中:

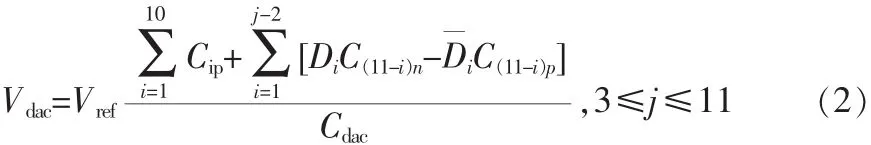

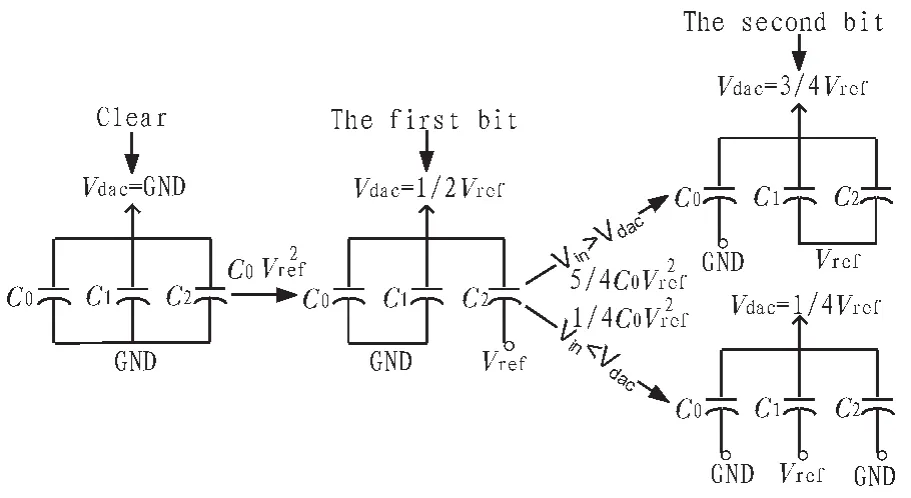

传统的电容阵列在转换过程中效率很低。为了说明这一点,以一个传统的2-bit电容阵列为例,如图3所示,其中C2=2C1=2C0。清零阶段,所有电容全部接GND,没有能量消耗。当清零过后,进行第一位的比较时,MSB电容C2接Vref,而其他电容(C0和 C1)仍然接地,因此电容阵列的输出 Vdac=1/2Vref,其中Vref是参考电压,此时电容从参考电压吸收C0Vr2ef的能量。在进行第二位的比较时,DAC进行两种转换:如果Vsh>Vdac,进行“up”转换,即 C1接 Vref(C1起始接 GND),因此 Vdac=3/4 Vref,则需要从参考电压吸收Eup=1/4C0Vr2ef的能量;相反地,如果 Vsh 图3 传统单端2-bit DAC电容阵列在一次转换过可能出程中所有可能出现的情况Fig.3 All possible cases in one conversion cycle of a 2-bit conventional DAC capacitor array 图4 改进的2-bit DAC电容阵列在一次转换过程中所有现的情况Fig.4 All possible cases in one conversion cycle of a 2-bit proposed DAC capacitor array 从上述可以看出,传统电容阵列在“up”转换时消耗能量最少,而在“down”转换时消耗能量最大,而分割电容阵列相对来说消耗的能量较少。通过仿真可以得知,本文所用的SAR ADC结构由于电容偏转所消耗的平均能量比传统的SAR ADC要节省30%左右。 对于高速应用的ADC来说,一个重要的技术指标就是DAC的建立时间。在“down”转换过程中,传统电容阵列中需要有两个电容进行切换,而控制电容转换的开关在转换过程中的任何不匹配,无论是随机的还是确定的,都可以引起电容阵列向错误的方向进行转换,甚至引起前置放大器的过载。而分割电容阵列在每一位的比较过程中,只有一个电容变化时,对开关信号的歪斜有很好的抵制作用。图5是通过仿真对两个电容阵列的建立时间进行了对比。从仿真结果可以看出,当分割电容阵列和传统阵列开关时间的宽度相同时,分割电容阵列的建立时间比传统阵列的建立时间快了8%左右,而且电容值越大,建立时间缩小的越明显。 图5 本文提出的电容阵列和传统电容阵列的建立时间Fig.5 Comparison of the settling time of the proposed and conventional capacitor arrays 图6 本文设计比较器的整体架构Fig.6 The framework of the proposed comparator 文中采用的比较器结构简化如图6所示,它是由三级预放大和锁存器组成,其中一、二级预放大器结构相同。比较器的失调电压是影响比较器比较精度的一个重要参数,进而影响整个ADC的精度[4],而失调电压是经过放大器放大之后再存储在电容上的,所以放大级的增益不能太大。过大的增益会使输出饱和,这样存储在电容上的电压就不能反映真实的失调电压的值,所以三级预放大器每一极均有较小的增益,这样做还可以获得较大的带宽,提高比较器整体的响应速度。但是比较器的增益过低,则会影响其精度,而锁存器的使用则是为了提高比较器的增益,同时又降低其功耗[5],进而提高比较器的有效精度[6]。 本设计基于Cadence Virtuoso版图编辑工具对SAR ADC进行布局布线和版图绘制。电容阵列采用MIM (metalinsulator-metal)电容,提高了工艺兼容性,减小了成本。在版图布局方面,电容阵列采用对称的布局方式进行布局[7],有效地减小了电容匹配误差。由于本文的逐次逼近寄存器及控制电路是采用verilog编码,并通过Encounter工具生成的数字电路,因此本文将数字电路和模拟电路分开布局,并用电地环进行隔离,以防止相互干扰。电路版图如图7所示,芯片版图面积约为800 μm×340 μm。最后利用Assura软件从版图生成了带寄生参数的网表,并进行了后仿真,以验证电容不匹配及寄生参数等对电路的精度、速度的影响[8]。在采样速度为1-MS/s,信号频率为50 kHz的情况下,后仿真的3种工艺角结果如表1所示。从表1中可以看出,ADC的有效位数为9.3 bit左右,基本达到预期目标,可以正常工作。 图7 SAR ADC的整体版图Fig.7 Layout of proposed SAR ADC 表1 后仿真结果Tab.1 Post-simulation results 文中设计了一种单端10-bit SAR ADC IP核,分析了整个系统的主框架和数模转换电路(DAC)以及比较器。采用XFAB 0.35 μm CMOS 工艺,利用 Cadence Spectre软件,对系统进行了仿真。仿真结果表明在电源电压3.3 V,输入电压范围0~1.5 V,采样速率为1 MHz,输入信号频率50 kHz的情况下,测得有效位数ENOB为9.37 bit,SNR为58.69 dB,SFDR为 72.86 dB,THD为 67.51 dB,SNDR 为 58.16 dB,功耗仅为4 mW。满足设计需求,可以应用于单端输入信号电路中。 [1]LIN Chi-sheng,LIU Bin-da.A new successive approximation architecture for low-power low-cost CMOS A/D converter[J].IEEE Journal of Solid-State Circuits,2002,38(1):54-62. [2]HONG Hao-chiao,Lee Guo-ming.A 65-fJ/Conversion-Step 0.9-V 200-kS/s Rail-to-Rail 8-bit Successive Approximation ADC[J].IEEE Journal of Solid-State Circuits,2007,42(10):2161-2168. [3]Brian P.Ginsburg, Anantha P.Chandrakasan, Fellow.500-MS/s 5-bit ADC in 64-nm CMOS With Split Capacitor Array DAC[J].IEEE Journal of Solid-State Circuits,2007,42(4):739-747. [4]Fotouhi B,Hodges D A.High-resolution A/D conversion in MOS/LSI[J].IEEE Journal of Solid-State Circuits,1979,14(6):920-926. [5]Ahmad Shar.Design of high speed CMOS comparator[D].Linköpings:Electronics System at Linköpings Institute of Technology,2001. [6]YU Li, ZHANG Jin-yong,WANG Lei,et al.A 12-bit fully differential SAR ADC with dynamic latch comparator for portable physiological monitoring applications[J].Bulletin of Advanced Technology Research,2011,5(7):576-579. [7]LIU Chun-cheng,Soon-jyh C,HUANG Guan-ying, et al.A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure[J].IEEE Journal of Solid-State Circuits,2010,45(4):731-740. [8]SUN Lei,DAI Qin-yuan,Lee Chuang-chuan,et al.Analysis on capacitor mismatch and parasitic capacitors effect of improved segmented-capacitor array in SAR ADC[J].2009 Third International Symposium on Intelligent Information Technology Application,2009,2:280-283.

1.3 比较器电路架构

2 版图设计与系统仿真

3 结 论