一种用于光通信的高速LVDS发送器设计

2011-09-04朱忠英陈科明孙玲玲

洪 慧,朱忠英,陈科明,孙玲玲

(杭州电子科技大学电子信息学院微电子CAD所,浙江杭州310018)

0 引言

随着微电子工艺的不断发展和集成电路特征尺寸的不断缩小,无线通信、计算机和因特网等的数据传输速率越来越快,高速率、长距离的有线数据传输已成为目前系统之间数据交换的迫切要求;另一方面,随着电子产品的便携化发展,低功耗成为电子设备一个突出的问题,因而迫切需要一种新的接口技术来提高传输数据,并具有低功耗、低噪声等良好特性。低压差分信号传输技术(Low Voltage Differential Signaling,LVDS)就是一种新的具有低电平电压摆幅、差分信号传输结构的电路,具有驱动电流恒定、低功耗、低EMI、抗噪声干扰等特点,工作频率可达GHz以上[1]。因此,相比其他传输技术,LVDS已成为一种良好的高速率低功耗的点对点通信传输技术,并被用于光通信、LCD显示和芯片间等系统的数据传输[2、3]。但是随着数据传输速率进一步提高,数据信号漂移和抖动将会严重影响LVDS接收器的数据正确性[4]。一旦接收有误,这就需要系统增加大量冗余电路将数据和时钟错误恢复出来,而时钟和数据恢复电路仍然是一个巨大的技术难题[5]。因此,本文设计一种高性能、低功耗和简单的LVDS收发器对于增加系统可靠性和降低系统成本是十分有价值的。

1 LVDS发送器设计原理

本文所介绍的LVDS发送器电路,其基本结构如图1(a)所示。M1~M2管(NMOS)、M3~M4管(PMOS)是4个宽长比较大的MOS开关管。当LVDS发送器电路正常工作时,ina2、ina1信号和inb1、inb2信号相位相差180°。当ina2、ina1信号为高电平,inb1、inb2信号为低电平时,M1和M4导通,M2和M3截止。由于outp和outn之间在外部通过传输线接一个负载电阻(100Ω匹配电阻),此时3.5mA电流源中的电流经过M4管,然后从outn端通过负载电阻流向outp端,最后通过M1管到地。这样在outp和outn端就会产生一个VID=Voutn-Voutp=3.5mA×100Ω=350mV左右的差值电压。反之,当ina2、ina1信号为低电平,inb1、inb2信号为高电平时,3.5mA电流源中的电流从outp端通过负载电阻流向outn端。这样就产生了VID=Voutn-Voutp=-350mV的差值电压。LVDS发送器在正常工作时,其outn和outp端的输出电压波形如图1(b)所示。

图1 LVDS发送器电路基本结构

2 LVDS发送器关键单元电路设计

图2 LVDS发送器电路结构

考虑到LVDS发送器具有较大的驱动电流能力,这也意味着LVDS发送器的驱动MOS管(见图1中M1~M4管)的尺寸较大,这就需要增加一些缓冲电路来提高LVDS发送器的整体驱动能力。LVDS发送器核心电路的基本组成结构如图2所示,一共包括3个部分:电平位移电路、缓冲器和驱动电路。电平位移电路将1.2V CMOS数字电平信号转化为2.5V CMOS数字电平信号;缓冲器将大幅提高CMOS数字信号的驱动能力;驱动电路将根据CMOS数字信号产生相应的LVDS差分信号并输出。

实际应用过程当中,由于非理想传输线和焊盘寄生效应的影响,输出共模电压会产生漂移。为了保证LVDS发送器的差分输出信号的共模电压稳定在一个固定值(1.25V左右)上,电路中必须增加共模反馈电路,其电路图如图3所示。这里采用两个电阻形成电阻分配器来得到输出信号outn和outp的共模电平Vcm,然后将Vcm信号与参考电压Vref进行比较放大,最后将误差信号送回至驱动电路的偏置点,控制驱动电路的电流源。实际工作过程中M1、M2、M3和M4开关管打开和关断时对输出产生很大的电压波动,会对输出共模电压产生很大影响。在设计过程中,通过合理设计共模反馈运放的增益和相位裕度,同时兼顾该运放压摆率和驱动能力,尽可能抑制开关管所产生的开关噪声,最终使输出共模电压的稳定性大为改善而且输出波形抖动也更小。

图3 LVDS驱动单元电路图

3 版图和仿真

LVDS发送器的版图设计要充分器件大电流特性以及金属走线对信号的影响,并尽量减小交叉信号版图的耦合效应;同时还需充分考虑电流源MOS管、差分放大器MOS管以及电阻的匹配问题。基于此,完成了LVDS发送器整体的全定制版图设计。本次设计的LVDS发送器的版图采用0.13μm CMOS工艺,版图面积为130μm×90μm。

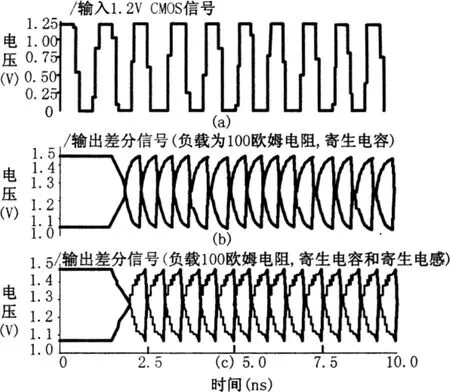

在实际应用中,非理想传输线和焊盘寄生效应会影响LVDS发送器的性能,因而仿真设计过程中必须要考虑这些影响。在这里,通过离散分布模型来等效这些寄生效应,等效负载模型如图5所示。在0.13μm CMOS工艺库下,针对LVDS发送器在电源电压、温度和工艺角变化的情况下进行了仿真。低电源电压和高电源电压分别为1.2V和2.5V,输入0~1.2V CMOS方波信号。在理想情况下,输出共模电压为1.25V,摆幅为350mV的LVDS信号。当考虑非理想传输线和寄生电容的影响下,输出LVDS信号产生一定的波形失真。在两种不同负载情况下的LVDS输出波形(2Gb/s)如图6所示。图6(b)中波形为只考虑焊盘负载情况(CL=2.5pF)下的LVDS输出波形,波形抖动较小,不容易产生误差;一旦考虑非理想传输线电感和封装寄生电感,波形将产生一定的抖动,如图6(c)所示。在本设计中充分考虑这些影响,对电路参数进行了优化,在考虑非理想传输线和焊盘寄生情况下,抖动减小到30mV左右,而且建立时间也大为减小。整体电路最大传输速率可达到2.5Gb/s,整体电路动态功耗为30.5mW,满足低功耗需求。

图5 寄生离散分布模型

图6 两种不同负载情况下的LVDS输出波形(2Gb/s)

4 结束语

本文设计了一种基于0.13μm CMOS工艺且最大传输速率为2.5Gb/s的高速LVDS发送器。该LVDS采用有效的共模反馈电路,抑制输出波形抖动过大影响,降低LVDS输出建立时间,从而使LVDS输出具有更小的过充电压和更稳定的共模输出电平。通过仿真,该LVDS发送器的抖动小于30mV,共模电平基本稳定在1.25V。该LVDS发送器能在最大2.5Gb/s传输速率下正常工作,同时功耗只有30.5mW,满足LVDS实际应用的需求。

[1] IEEEstandard for low-voltage differential signals(LVDS)for scalable coherent interface(SCI)[S].IEEE Std.1596.3 -1996,1996.

[2] Lee Jaeseo,Lim Jae-Won,Song Sung-Jun,etal.Design and implementation of CMOS LVDS 2.5 Gb/s transmitter and 1.3 Gb/s receiver for optical interconnections[C].Sydney:The 2001 IEEE International Symposium on Circuits and Systems,2001:702 -705.

[3] Cai Hua,Li Ping.A novel 2.2 Gbps LVDS driver circuit based on 0.35μm CMOS[J].Journal of Semiconductors,2010,31(10):1-5.

[4] Wang Chua-Chin,Lee Ching-Li,Hsiao Chun-Yang,etal.Clock-and-Data Recovery Design for LVDS Transceiver Used in LCD Panels[J].Circuits and Systems II:IEEE Transactions on Express Briefs,2006,53(11):1 318 -1 322.

[5] Razavi B.Challenges in the design high-speed clock and data recovery circuits[J].IEEE Communications Magazine,2002,40(8):94-101.