一种改进的时钟网络设计方法及实现*

2011-08-29鲍进威喻小虎

鲍进威,田 丰,喻小虎,张 建,欧 钢

(国防科学技术大学 卫星导航与定位中心,湖南 长沙410073)

0 引 言

集成电路经历了小规模集成(SSI)、中规模集成(MSI)、大规模集成(LSI),发展到目前的超大规模集成(VLSI)和特大规模集成(ULSI)阶段,同时随着芯片特征尺寸的缩小、设计复杂性的提高、时钟速度的增快、电源电压的降低、布线层数的增加,使得深亚微米下的大规模集成电路的设计复杂度越来越高,由此引出的一系列新的设计挑战,作为电路系统的时间参考,时钟信号在同步电路系统中占据着重要地位[1],而时钟分布电路的设计是高性能电路设计中最具有挑战性最重要的部分之一。

在Encounter中有两类方案设计时钟分布:一个是时钟树综合(CTS),一个是时钟网格(Mesh)。时钟树是一种通过插入缓冲器(buffer)连接的时钟网络,它的时钟源点定义为时钟输入引脚(或产生的时钟节点)。时钟树综合可以完全依靠全自动的EDA工具最大限度地减少时钟偏差,并通过减少时钟缓冲器数目来降低功耗。而针对时钟网格则有人曾提出过时钟网格+局部树(MLT)的时钟结构[2-3],但是完全用手动来设计 MLT时钟结构将会使设计变得很复杂,使芯片的设计周期变长。同时由于现有的MLT时钟结构的设计一般是通过预留金属层来建立一个网格结构来提供时钟信号的,这样会存在浪费布线资源的问题。本文的重点是对MLT的时钟结构进行优化,将时钟设计的两种方法结合起来,形成时钟网格(Mesh)+局部树自动综合的结构(MLTAS),并将时钟网格嵌入到时钟网络的Stripes中,以节约布线资源。

1 时钟网络设计方法

在物理设计中的时钟设计方法比较有限,最常用是单一的时钟树综合(CTS),而另一种不常用的方法就是时钟网格+局部树(MLT),这两种方法各有利弊。

1.1 单一的时钟树综合(CTS)

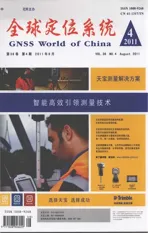

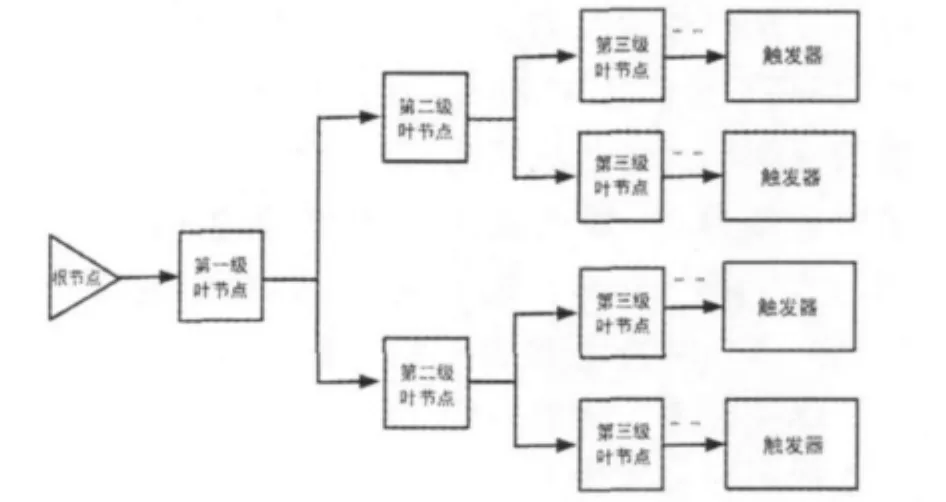

时钟树也称为时钟网络分布,它是指时钟源和时钟所控制的寄存器时钟端之间的一系列的组合逻辑。它的逻辑结构是逐步增大增多的时钟缓冲器和反相器组成的树状结构,因此被形象称为时钟树。其简化模型如图1。

图1 时钟树结构的简化模型

时钟树的结构设计包括三个方面[4]:时钟树的层数,每层的分支数和每个分支的驱动器种类[5-6]。时钟树的设计将影响芯片的时钟偏移和延时的大小。由于每层负载电容不同,所以时钟树的层数越少则不确定性越小,从而时钟偏移越小。分支数越多则需要越多的驱动和连线,将导致面积的增加和由于连线而产生的潜在的时钟偏移不确定性。而分支少会使所需的层数增加,也会导致时钟偏移的不确定性和延时的增大。选择驱动器要保证有足够的驱动能力,但驱动能力大会增大上一层驱动器的电容负载,并导致延时和功耗的增加,所以选择不同层的驱动器时要选择其平衡点,已达到在满足驱动能力的情况下延时最小。

时钟树综合[7]就是根据设计和单元库的物理信息,在时钟路径上插入一个时钟缓冲器和反相器组成的树状结构,使得时钟信号严格按照设计要求到达芯片寄存器的时钟端口。时钟树综合在整个后端设计流程中位于布局之后,布线之前。

1.2 时钟网格+局部树

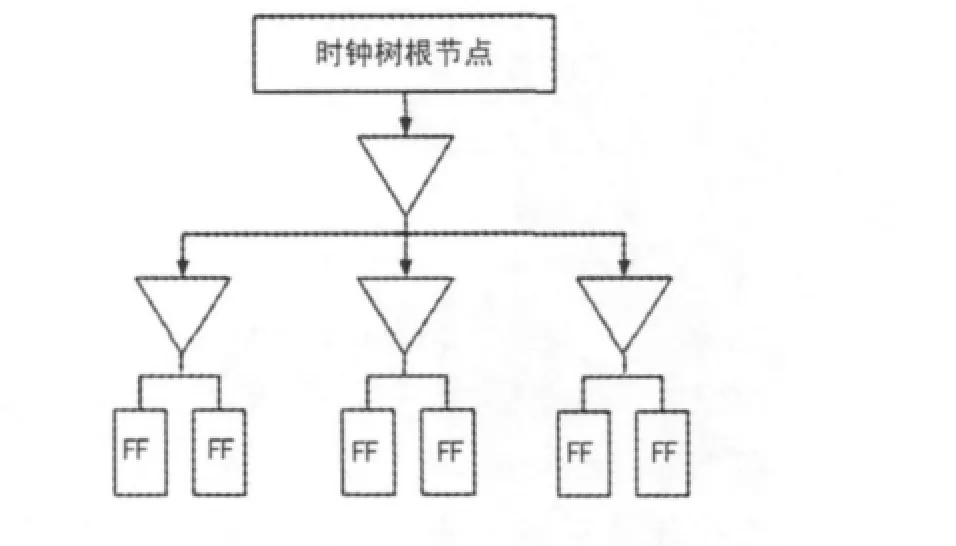

在实际的MLT设计中,时钟分布网络[8]通常被划分为两部分:全局的和局部的时钟网络。全局的网络是将时钟信号从时钟源分配到各个局部区域,通常它有一个对称的结构。然后本地的时钟网络再将时钟分配到各个时钟元素,它通常是非对称的。结构如图2所示。

图2 MLT结构模型

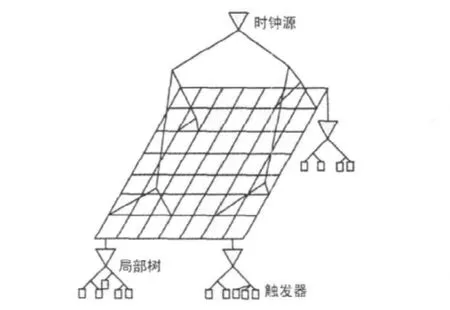

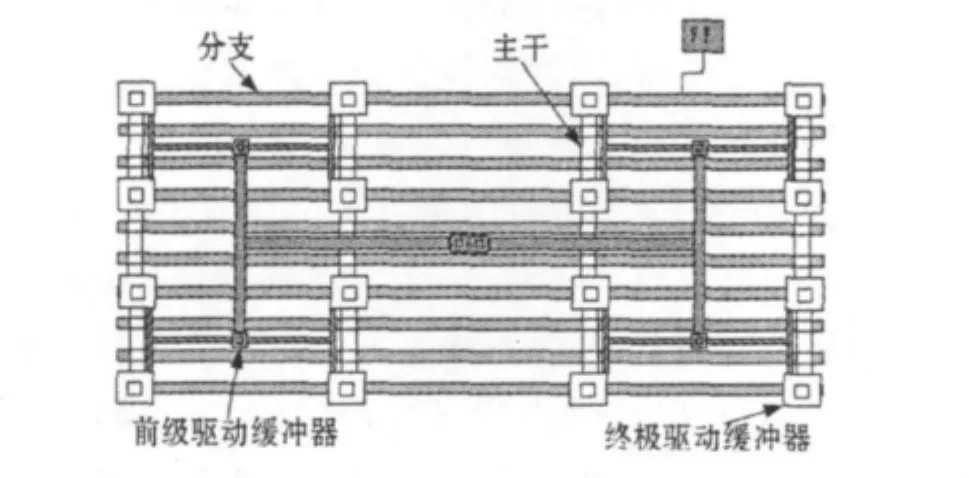

在Encounter中,半自动的时钟网格工具可以被用于构建顶层的网格结构。网格可以被划分为三部分:顶层链,全局网格,局部分布,如图3所示。

顶级链为网格的前级驱动提供合适的输入转换时间,或为网格增加额外的插入延迟,这种串联的缓冲器链在整个网格结构中是可选的。

图3 全局网格结构图[9]

局部树也是一个可选的部分,如果不定义局部树的结构,时钟网格会平衡所有网格段的偏差。

全局网格使用多个(大于等于零)前级驱动级,然后是一级主驱动。主驱动用来驱动一个最终的全局网格线网,最终的网格驱动器驱动主干和分支网格。

在Encounter工具中存在两种网格结构:

1)H-tree[9]

这种结构的网格的优点是前级驱动高度对称,因此,对于具有很多触发器的大型时钟域来说可以较好的控制偏差。缺点就是它比其他网格结构需要更多的高的功耗以及布线资源,如图4。

图4 H-tree结构示意图

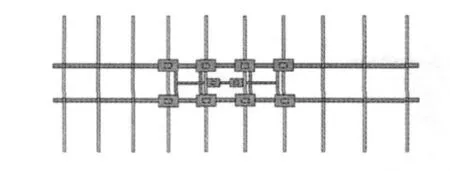

2)Fishbone[9]

Fishbone的主驱动对一个主干线网(脊干)使用多点驱动,而主干线网则驱动许多正交的分支,被多点驱动的前级驱动的主干构成了前级驱动阶段,并被放置在距离下一级的驱动输入足够近的地方,如图5。

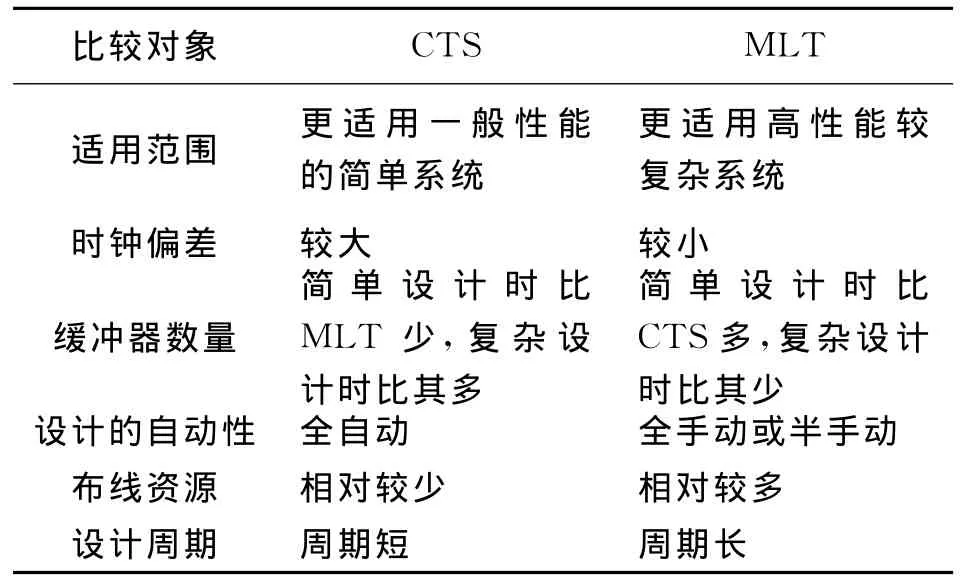

1.3 CTS与MLT的比较

我们已经对两种方法原理做了介绍,对两种设计方法的优劣做一下比较。

图5 Fishbone结构示意图

从表1可以清晰的看到这两种方法的优缺点,所以为了扬长避短,在两者之中取一个平衡,同时获得很好的性能。我们提出一种改进的设计方法。将时钟设计的两种方法结合起来,形成时钟网格(Mesh)+ 局部树自动综合 (Local Tree auto synthesize)的结构(MLTAS),同时为了节约布线资源,将时钟网格嵌入到时钟网络的Stripes中。

表1 CTS和MLT优劣比较

1.4 MLTAS时钟网络设计方法

时钟网格(Mesh)+局部树自动综合(Local Tree auto synthesize)的结构(MLTAS)是结合了CTS和MLT两种时钟网络设计方法。它的原理就是上述两种设计原来的结合。在局部树的设计上它是采用了自动时钟树综合来实现,充分利用了布线和缓冲器内插算法的EDA工具来做自动化综合,从而减少了芯片设计的周期。而在全局网络的设计则采用的是时钟网格设计,通过网格设计的高度对称性来减少时钟偏差,同时为了节约布线资源,也即节省功耗,我们不是通过预留金属层来建立网格结构而是将时钟网格嵌入到时钟Stripes中,以节约布线资源的目的。MLTAS同时具备了比MLT设计简单,设计周期短,布线资源节约的优势,又达到比CTS设计减少时钟偏差的目的。

2 MLTAS设计方法的应用

为了实现MLTAS设计方法,我们将它应用于北斗用户系统的一款0.18μm的SOC芯片设计上。MLTAS设计是一个分两阶段的自底向上的过程,第一阶段是通过自动时钟树综合来构建底层接近零偏差的局部树,第二阶段是构建上层零偏差的全局网络,从而大大减少时钟偏差。

2.1 局部树的构建

局部树的构建可以通过手动方式来完成,这样可以达到时钟偏差的可控性设计,但为了设计简单,提高设计效率,同时又能到达预期的设计效果。这部分是通过自动时钟树综合来构建底层接近零偏差的局部树。MLTAS的Local Tree部分采用的就是全自动的时钟树综合来完成的。设计思路是:根据完全的自动时钟树综合设计的CTS分析结果,追溯时钟网络,以获得时钟的结构信息,根据所得的结果,重新寻找时钟源的输入端,并且以新的时钟源的输入端为根节点(Root Pin)做自动时钟树综合。在局部树的构建过程中本设计是将单一时钟树综合后时钟树结构中的LEVEL3的标准门单元都提取出来作为新的时钟源输入端,简易示意图如图6,并将前面的驱动全部删除,而这些提取的时钟源输入端又直接连接到网格结构中的树枝上(或连接在树枝上的buffer上面)。在局部树的构建过程中首先要将原先的时钟树的规格修改,将提取出的时钟节点作为新的时钟源输入端,同时要对时钟偏差,信号跳变时间,时钟到达时钟端的延迟时间,最大扇出等做适当的修改,以得到更好的局部信号分布结构。

图6 CTS综合后的简易时钟树结构示意图

其中含Level的方框即可以代表buffer也可以代表标准时钟门单元。图7分别是单一时钟树综合(CTS)设计和局部树自动综合(LTAS)设计结果的比较,其中左边为CTS的效果图,右边是局部树自动综合的效果图。

通过两个图的对比可以看出左边的CTS后的时钟信号是从最左边的时钟根节点来提供的,而右边的LTAS后的时钟信号则是从提取的时钟源输入端而不是原先的根节点提供的。

图7 CTS后效果图VS局部树自动综合(LTAS)后的效果图

2.2 全局网格的构建

一般的时钟网格设计都是通过预留金属层以建立一个网格结构来提供时钟信号,这样会造成功耗的增加,布线资源(布线层数、过孔,线长等)的浪费。由于本款芯片设计是一个六层金属的设计,考虑到电源供电的充分性,即在第4、5、6层都有电源网络分布,同时又要节约布线资源,没有给全局网格的构建再预留单独的金属层,而是在设计中将全局网格设计在第5、6层。为了不将网格结构与电源网络的位置相冲突,必须将全局网格嵌入到电源网络Stripes之间的空隙中,以达到设计要求的同时,节约布线资源和功耗。

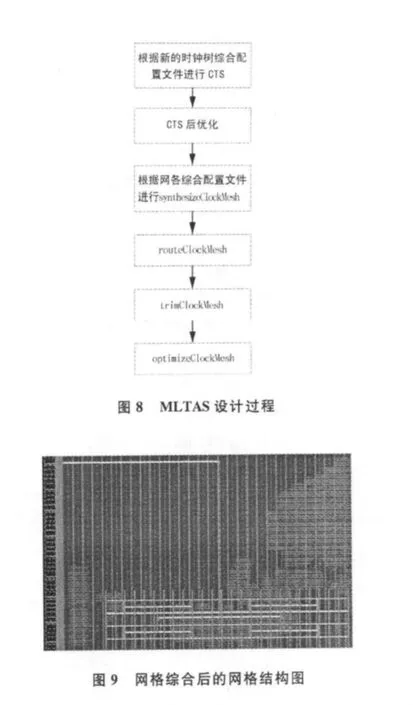

在综合全局网格之前,首先定义网格的配置文件[10],包括布线的类型(金属线宽、间距,布线分布层数)、网格的级数、网格缓冲器的类型,根节点,叶子节点。还要规定网格的结构类型,规定树干、树枝以及网格缓冲器的放置方式。比如树干、树枝放置的间距,分布方式,树干、树枝和缓冲器三者之间的接触频率。在全局网格的构建中,为了得到更好的时钟偏差,选择的是H-tree的四级网格结构。同时为了将网格结构嵌入到Stripes中,将树干之间的间距和树枝之间的间距选取特殊的值而不让其自动去设置。然后将网格的规格文件读入系统,此文件中将包含有关时钟端的信息,即规定哪些器件的输入端作为时钟的输入端。下面是Encounter中用来设计时钟网格的过程:首先是提取出所有时钟源输入端,并将提取出的时钟源输入端作为时钟根节点,进行时钟树自动综合,综合后再做优化;第二步就是将这些时钟源的输入端作为网格结构的叶子节点进行网格综合,并做布线,金属线剪裁以及优化,如图8。

在Encounter中完成上述操作后,可以看到嵌入到Stripes中的时钟网格结果,如图9。

图中的高亮显示的是网格结构的树干,次亮显示的是树枝,而浅色显示的纵横线网则是Stripes,从中我们可以很清晰看到时钟网格已经嵌入到时钟网络的Stripes之中。

3 MLTAS设计和CTS设计的结果比较

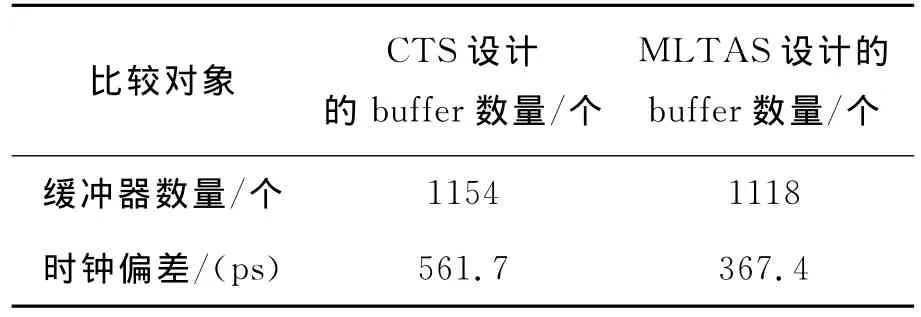

为了体现MLTAS设计方法性能的优越性,在相同设计面积和相同时钟频率的条件下,将其与CTS设计进行了比较。如表2所示,从CTS设计和MLTAS设计的结果中我们很容易得出,MLTAS在插入缓冲器方面比树形结构有一定优势,而在时钟偏差方面更是获得了较大的优化。下面我们从设计结果的数据来加以说明。

表2 CTS和MLTAS结果的比较

从表中可以明显的看到MLTAS设计比单一的CTS设计在总的buffer数量上要少36个,所以在高性能的芯片设计中MLTAS设计在缓冲器数量上会带来一定的优势。同时我们也可以看到MLTAS流程比单一的CTS流程的时钟偏差要小许多,总的时钟偏差减少了194.3ps,占CTS设计总时钟偏差的34.6%,得到了较大的优化。

4 结 论

结合CTS和MLT两种时钟网络设计方法提出了时钟网格(Mesh)+本地树自动综合(Local Tree Auto Synthesize)的一种新的时钟设计方法。将该设计方法应用到北斗用户系统的一款0.18 μm的SOC芯片设计上,并详细论述了设计的思路。最后在相同设计条件的情况下,通过比较自动综合的树结构和MLTAS的时钟设计的结果,得到MLTAS相比单一树形结构的CTS流程可以实现减少总的缓冲器数量和时钟偏差的效果,从而得出了本SOC芯片设计上,MLTAS设计比单一树结构的CTS设计具有更好的优越性,也体现了MLTAS也比CTS更适合高性能的复杂系统的芯片设计之中。

[1]汪 珺.基于Garfield5设计中时钟树综合技术研究[D].江苏:东南大学硕士学位论文,2006:1-2.

[2]Yeh C,Wilk G,Chen H.Clock distribution architecture:a comparative study[C]//Proc of the Int Symp on Quality Electronic Design.San Jose,CA,USA ,2006:85-91.

[3]Wilke G R,Murgal R.Design and analysis of“Tree+Local Meshes”clock architecture[C]//Proc of the Int Symp on Quality Electronic Design.San Jose,CA,USA,2007:165-170.

[4]殷瑞相,郭 瑢.同步数字集成电路设计中的时钟树分析[J].汕头大学学报·自然科学版,2005,20(3):75-80.

[5]Chi M C,Huang S H.A reliable clock tree design methodology for ASIC designs[J].Chung Yuan Journal,2000,28(3):115-122.

[6]Chung J,Cheng Chung-kuan.Optimal buffered clock tree synthesis[C]//ASIC Conference and Exhibit,Proceedings,Seventh Annual IEEE International,USA:Rochester,1994:130-133.

[7]刘辉华,刘 振,李蜀霞,等.层次化时钟网络设计研究[J].微电子学与计算机,2008,25(11):52-53.

[8]顾 琴,辜建伟,李玉童.在Encounter中实现网格+局部树的时钟设计流程[J].电子设计应用,2008(12):57-58.

[9]Cadence.Encounter user guide[R].2007.

[10]顾 琴,林正浩.用 Encounter实现 Mesh-Local-Tree结构的时钟设计流程[J].半导体技术,2008,33(7):628-629.